(1)MIPI定义

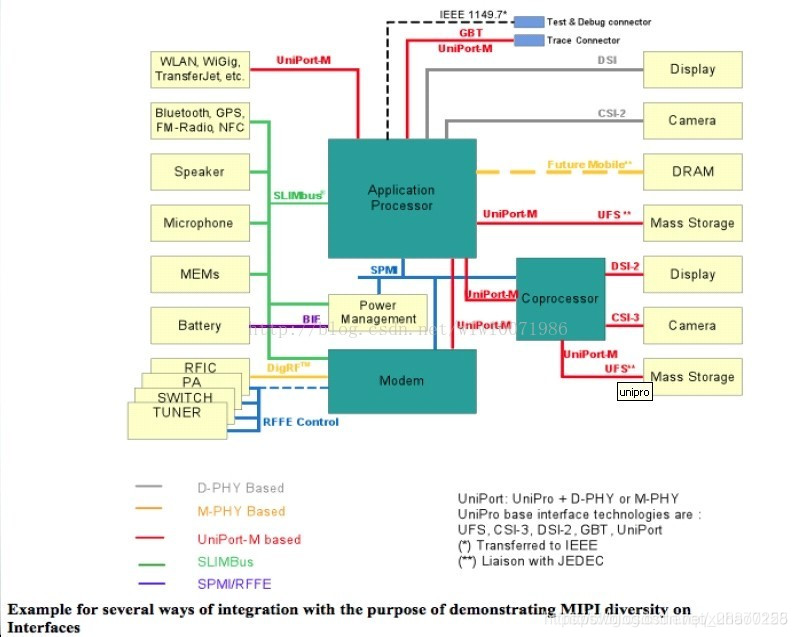

MIPI联盟定义了一套接口标准,把移动设备内部的接口如摄像头、显示屏、基带、射频接口等标准化,从而增加设计灵活性,同时降低成本、设计复杂度、功耗和EMI。

(2)MIPI特点

a. 高速:1Gbps/Lane,4Gbps吞吐量

b. 低功耗:200mV差分摆幅,200mv共模电压

c. 噪声抑制

d. 更少的pin,PCB layout更方便

(3)分辨率

MIPI-DSI:2048*1536@60fps

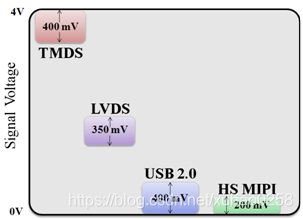

MIPI 是专门在高速(数据传输)模式下采用低振幅信号摆幅,针对功率敏感型应用而量身定做的。图2比较了MIPI与其它差分技术的信号摆幅。

由于MIPI是采用差分信号传输的,所以在设计上需要按照差分设计的一般规则进行严格的设计,关键是需要实现差分阻抗的匹配,MIPI协议规定传输线差分阻抗值为80-125欧姆。

几种流行的差分摆幅(differential-swing)技术的信号振幅比较

(4)MIPI-DSI模式

a. Command Mode

对应于并行接口的MIPI-DBI-2,带有Frame Buffer,刷屏基于DCS的Command集的方式,类似于CPU屏。

b. Video Mode

对应于并行接口的MIPI-DPI-2,刷屏基于时序控制,类似于RGB同步屏

(5)工作方式

a. command工作方式

使用DCS Long Write Command Packet刷新GRAM。

每帧第一个packet的DCS command为write_memory_start,实现每帧同步

b. video工作方式

使用sync packet实现时序同步,Pixel packet实现LCD刷屏。空白区域可以为任意,每帧要以LP为结束。

(6)硬件接口

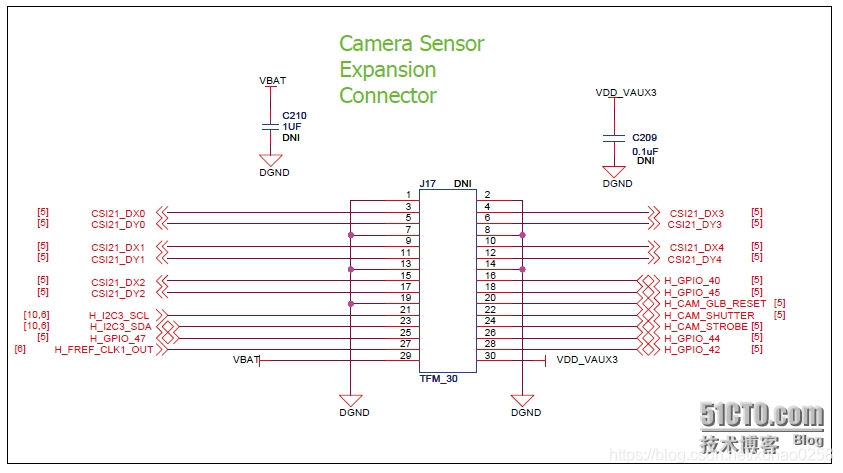

参考

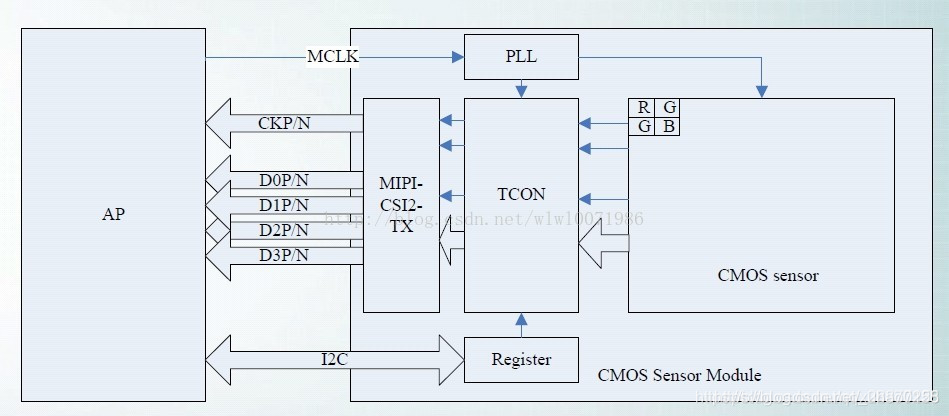

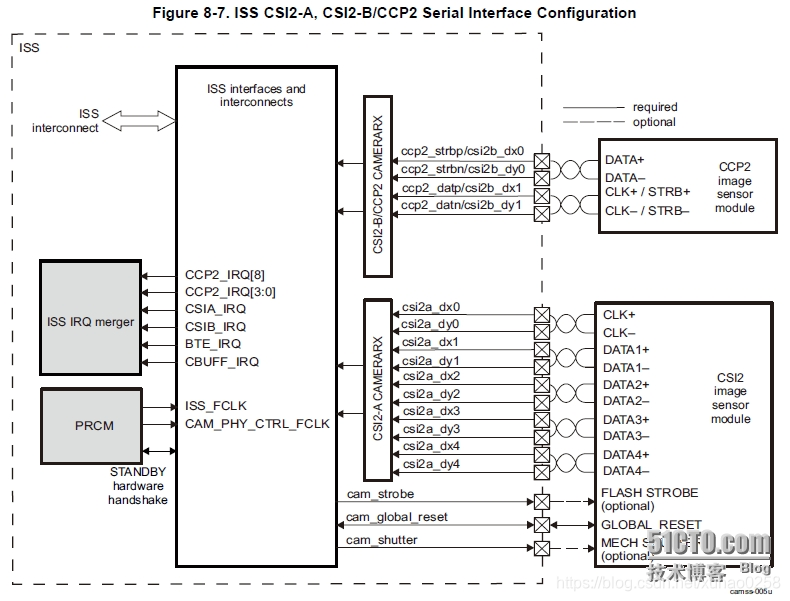

可以看到J17中包含了5组差分信号,即(CSI21_DX0,CSI21_DY0), (CSI21_DX1,CSI21_DY1), (CSI21_DX2,CSI21_DY2), (CSI21_DX3,CSI21_DY3), (CSI21_DX4,CSI21_DY4)。这五组信号来自于主芯片的CSI2-A接口,如下图所示:

2362

2362

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?