GPIO(General Purpose Input Output)通用输入输出口简介

- 可以配置为8种输入输出模式

- 引脚电平为: 0V - 3.3V,部分引脚可容忍5V

- 输出模式下可以控制端口输出高低电平(驱动LED,蜂鸣器,模拟通讯协议输出时序等)

- 输入模式下可以读取端口的高低电平或者电压,(于读取按键输入、外接模块电平信号输入、ADC电压采集、模拟通信协议接收数据等)

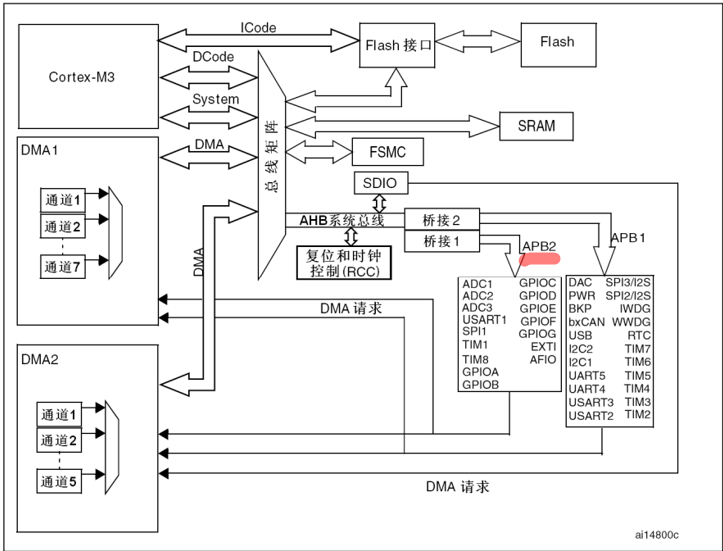

GPIO 基本结构

在STM32中,所有的GPIO都是挂载在APB2外设总线上。

图1-1

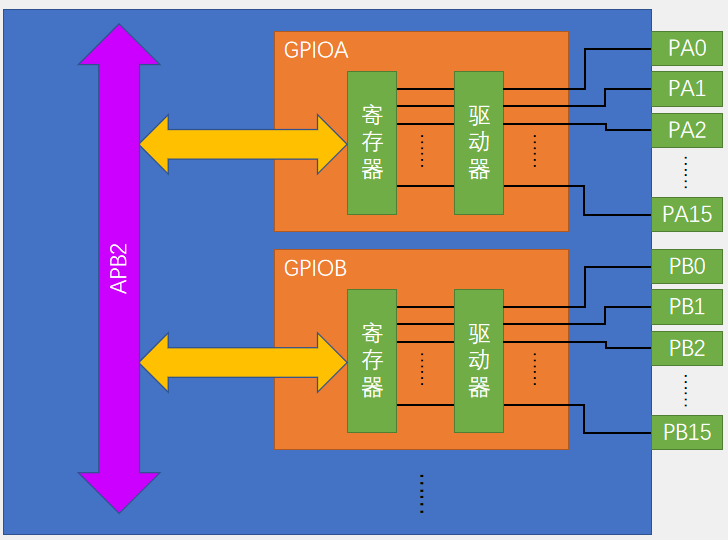

图1-2

STM32 的GPIO寄存器有32位,但是如图1-2 PA0 — PA15 只用了16位, 所以只用到了低16位,而高16位闲置。驱动器用来增强驱动能力 其命名方式为 GPIOA PA ; GPIOB

PB;GPIOC

PC

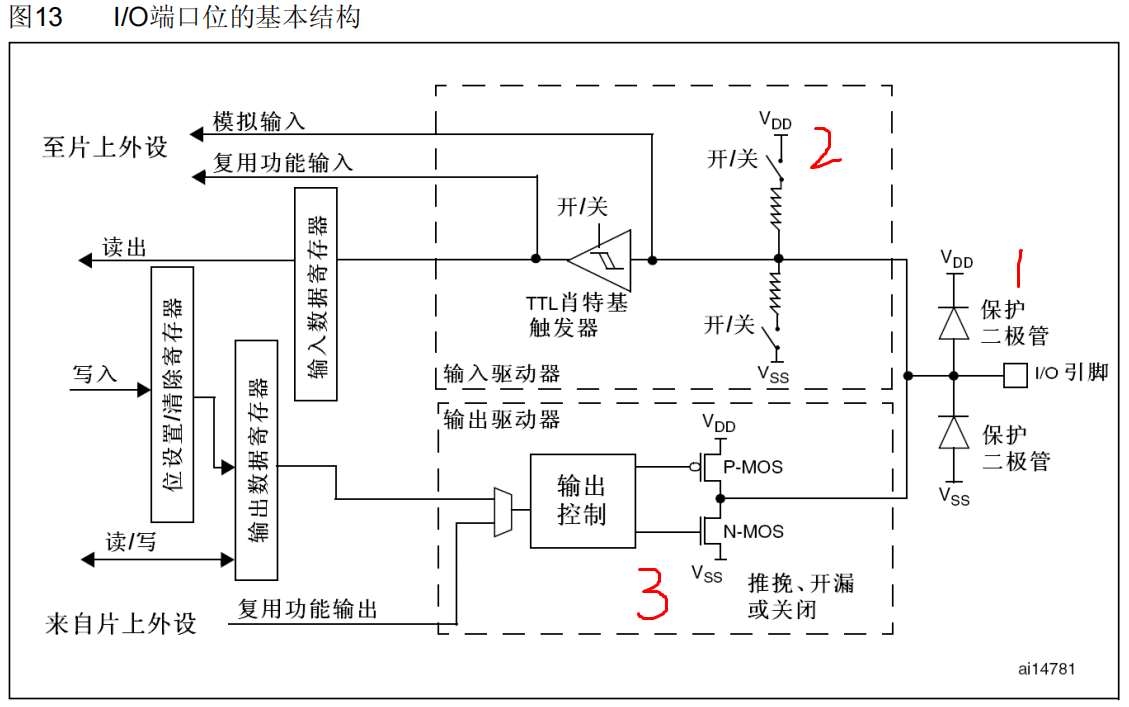

图1-3

接下来介绍GPIO的8种输入输出模式

如图1-3 ,可大致将其分为,输入 和 输出 两大部分。 在介绍之前,先看最右边1处的保护电路,作用就是限制I/O输入电压范围在0-3.3V,VDD接 3.3V ,VSS接 0V。 当I/O输入>3.3V 时,上面的二极管会导通;当I/O输入< 0V 时,下面的二极管会导通,从而保护电路。

- 浮空输入 : 在图1-3 的2处 ,对于数字端口,输入必须是 高/低 电平。如果 2 处上拉电阻和下拉电阻都不接,此时输入会处于一种浮空的状态,引脚的输入电平很容易被外界干扰导致改变。这就是浮空输入。

- 上拉输入 :在图1-3 的2处 ,如果接入上拉电阻,引脚悬空时,能有上拉电阻(电阻较大)来保证引脚高电平(默认高电平的输入模式)。

- 下拉输入 :在图1-3 的2处 ,如果接入下拉电阻,引脚悬空时,能有上拉电阻(电阻较大)来保证引脚低电平(默认低电平的输入模式)。

在输出部分,可以由两个地方来进行输出控制,一个是输出数据寄存器(16位),另一个是片上外设。

若通过输出数据寄存器来进行操作,就是普通的I/O口输出,可以通过操作数据寄存器的某一位就可以操作对应的某个端口。 而位设置/清除寄存器可以通过改变输出数据寄存器的某一位而不影响其他位。如 在位设置/清除寄存器 中将某一位设置为1,其他设置为0;那么输出数据寄存器相对应的哪一位会置1/清0,其余不变。

- 推挽输出 : 在图1-3 的3处,接有两个MOS管(一种电子开关),当选择为推挽输出模式时,P-MOS 和 N-MOS均有效。输出数据寄存器为1时,P-MOS导通,N-MOS断开,输出接VDD,I/O输出高电平;输出数据寄存器为0时,P-MOS断开,N-MOS导通,输出接VSS,I/O输出低电平。 在推挽输出下,STM32对I/O口有绝对的控制权,高低电平都是STM32控制。

- 开漏输出 : 在图1-3 的3处,此时P-MOS断开,只有N-MOS有效。输出数据寄存器为1时,N-MOS断开,此时输出相当于断开(高阻态模式); 输出数据寄存器为0时,N-MOS导通,输出接VSS,I/O输出低电平。此模式下只有低电平有驱动能力。

- 关闭 :在图1-3 的3处,P-MOS 和 N-MOS 都不工作,输出关闭,I/O的电平由外部来输入。

复用开漏输出,复用推挽输出同理。

| 模式名称 | 性质 | 特征 |

| 浮空输入 | 数字输入 | 可读取引脚电平,若引脚悬空,则电平不确定 |

| 上拉输入 | 数字输入 | 可读取引脚电平,内部连接上拉电阻,悬空时默认高电平 |

| 下拉输入 | 数字输入 | 可读取引脚电平,内部连接下拉电阻,悬空时默认低电平 |

| 模拟输入 | 模拟输入 | GPIO无效,引脚直接接入内部ADC |

| 开漏输出 | 数字输出 | 可输出引脚电平,高电平为高阻态,低电平接VSS |

| 推挽输出 | 数字输出 | 可输出引脚电平,高电平接VDD,低电平接VSS |

| 复用开漏输出 | 数字输出 | 由片上外设控制,高电平为高阻态,低电平接VSS |

| 复用推挽输出 | 数字输出 | 由片上外设控制,高电平接VDD,低电平接VSS |

5454

5454

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?