欢迎关注我的公众号:全栈芯片工程师。

MIPI是移动领域最主流的视频传输接口规范,目前应用最广泛的是MIPI DPHY和MIPI CPHY两组协议簇(另外还有MIPI MPHY,属于高速Serdes范畴,应用不那么广泛),其中CSI-2主要用于图像接入(一般是接Sensor),DSI-2主要用于图像输出(一般是输出到显示屏)。我们先看物理层协议。

-

MIPI DPHY规格

-

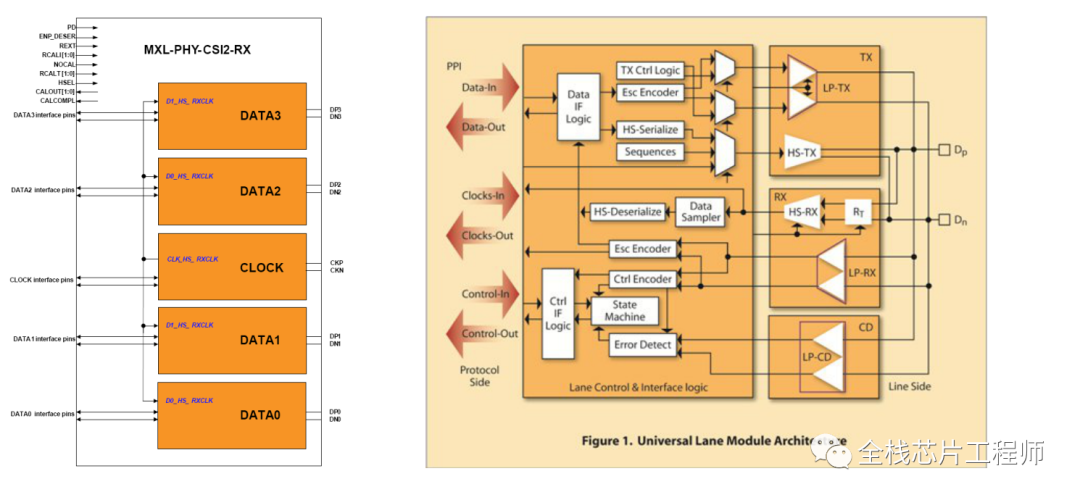

MIPI DPHY架构

-

MIPI DPHY时序

既然有了DPHY,为何要选择比DPHY复杂多的物理层CPHY呢?一切都是为了提升带宽。

-

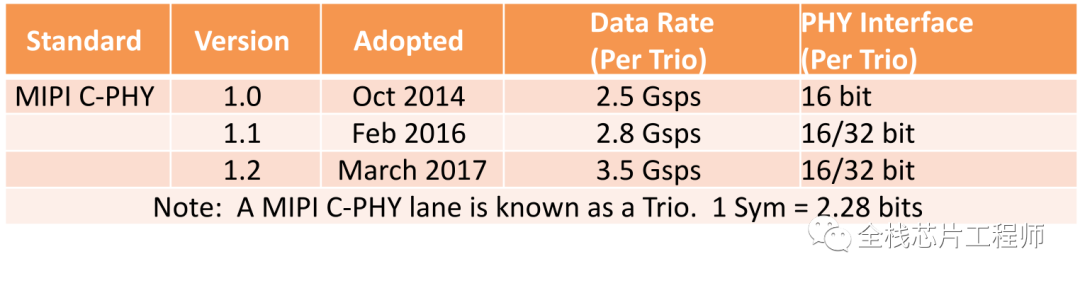

MIPI CPHY规格

-

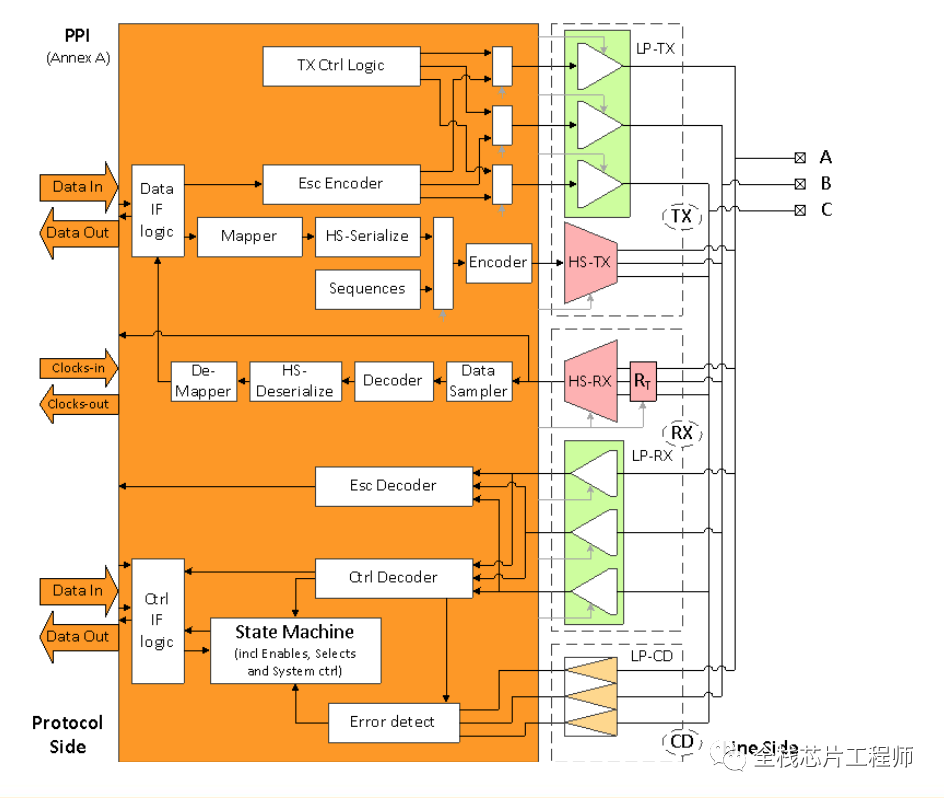

MIPI CPHY架构

-

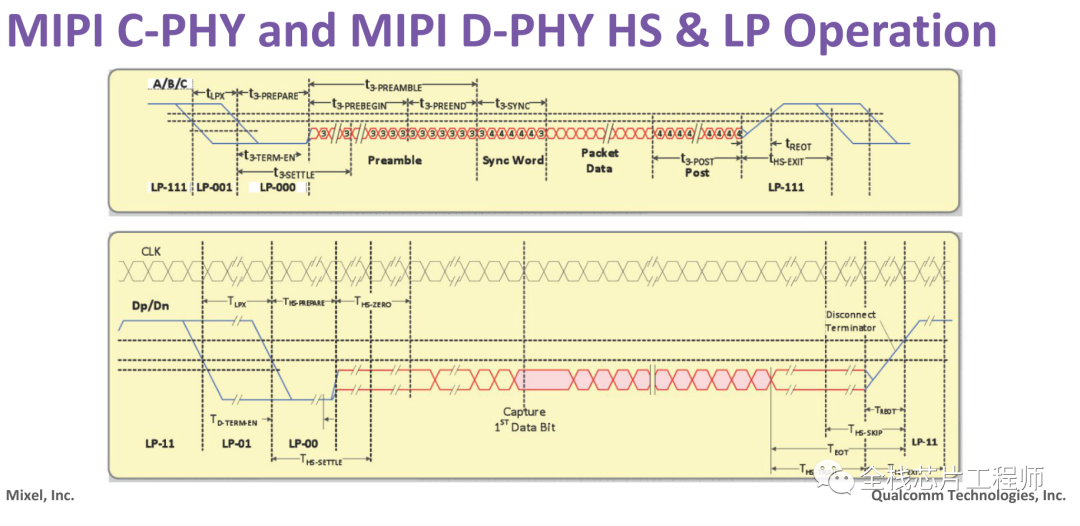

MIPI DPHY和CPHY物理层时序比较

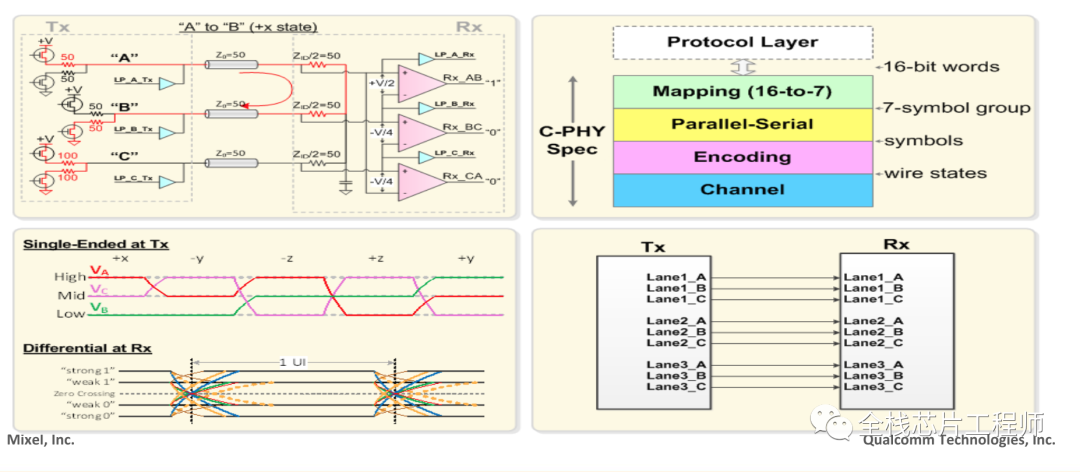

DPHY是源同步系统,有专门的同步时钟通道,但是CPHY没有同步时钟,时钟是嵌入到数据中的。显然的,实现嵌入时钟的目的是为了增加带宽,肯定会涉及到编码,物理层的结构必然是完全不同,单从线路上看,CPHY是一个A/B/C三线系统。

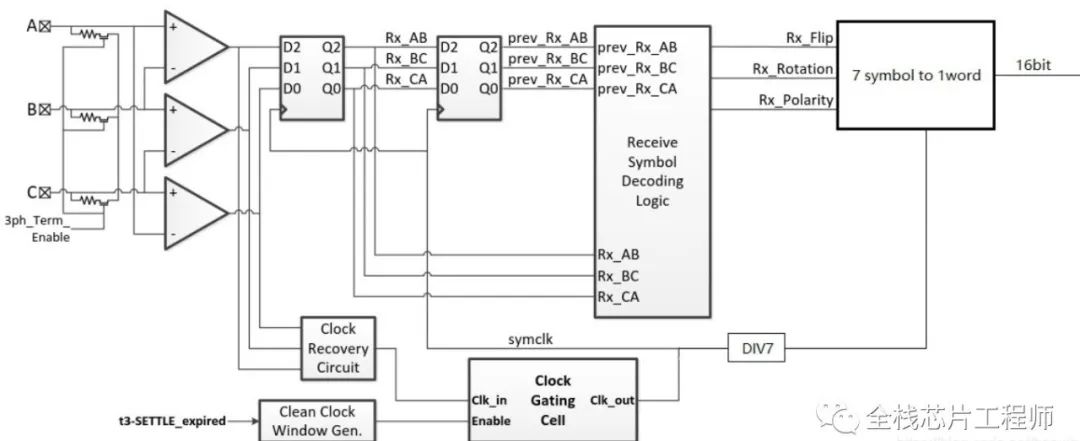

MIPI DPHY的物理层,一对时钟,几对数据,接收端根据时钟边沿采样数据,找到0xB8的同步头,物理层实现就算ok了。但MIPI CPHY不同,因为它不传输时钟,必须CDR先恢复时钟,然后再用恢复的时钟采样数据并寻找同步头,最后还需要进行数据解码恢复出最初的发送的内容(发送端的过程相反)。

CPHY“线态”变化图

CPHY接口等效电路图

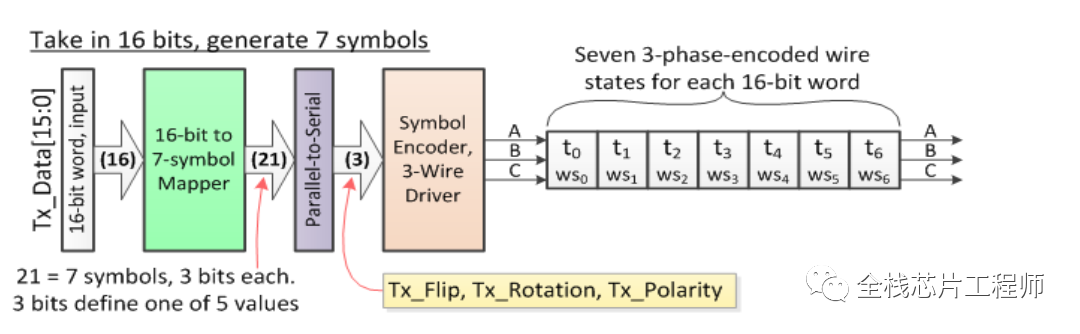

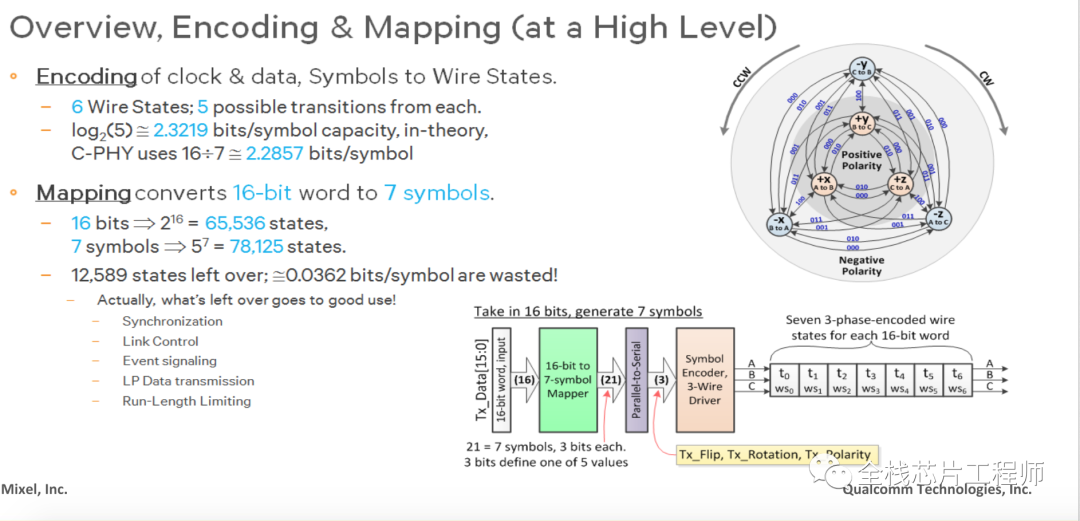

CPHY物理链路(A/B/C线)上传输的是不同的电平,通过A-B,B-C,C-A的电平运算,恢复出+x,-x,+y,-y,+z,-z六种不同的线态,通过前后线态的旋转方向,相位和极性恢复出编码符号,再通过连续7组符号解码出16bit的数据,整个过程见下图。

总的编码原理从下图便可一目了然:

为何要选择这比DPHY复杂多的物理层呢?一切都是为了提升带宽,某种线态的可能有5种不同的变化,那么它每个符号(A、B、C共3个bit)可编码的数据为log2(5)= 2.3219bit/symbol,理论带宽为DPHY的2.3219倍,每16bit数据编码成7个符号,带宽优势明显。

综上,总体来看DPHY vs CPHY有如下对比:

讲完物理层,我们再看看CSI-2层:

-

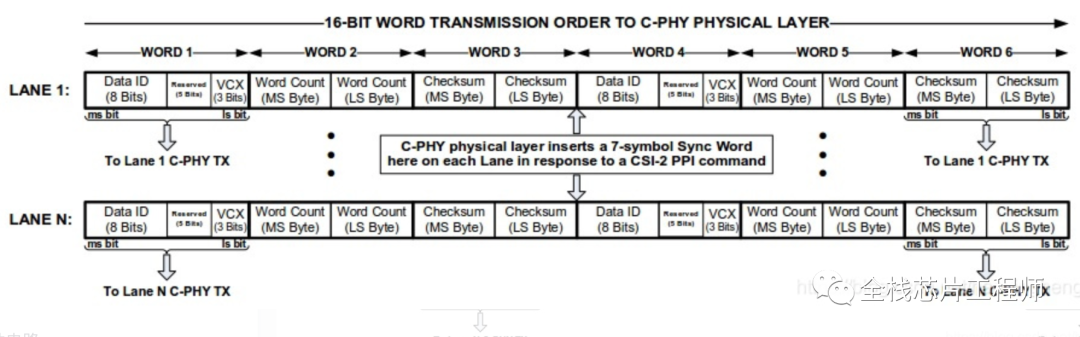

DPHY以Byte为单位进行数据组织;CPHY以16bit Word为单位进行数据组织;

-

DPHY 的短帧和长帧的帧头信息与数据的组织方式相同;CPHY则是固定每个通道为6×16bit的帧头信息(短帧信息),见下图。

欢迎关注我的公众号:全栈芯片工程师。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?