前言

Zynq的AMP模式在开发过程中,cpu1应用程序的bsp工程的boot.s中,禁用了L2 cache。在这里,阐述一下原因:

博客主体参考自下文,并在此基础上进行适当修改

https://blog.csdn.net/Franceshaa/article/details/78663213

1.开发平台

硬件平台:ZYNQ7z202clg400-2的创龙核心板

软件平台:

Windows 64位环境下:

Vivado 2017.04版本+SDK 2017.04版本

Linux环境下(Ubuntu 16.04):

Petalinux 2017.04版本

2.原理说明

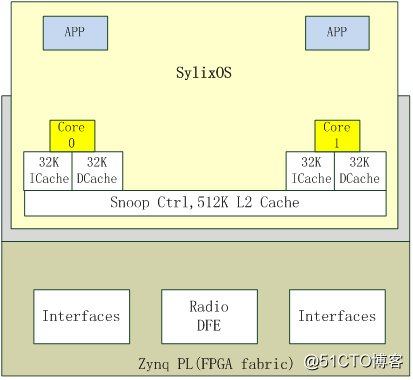

首先,在AMP模式中,core 0与core 1共用512K L2 Cache,这势必会引起两个核的Cache竞争问题。

通常情况下,L2 Cache被core 0,core 1共享。那么会出现以下情况:

core 0的内存访问操作可能会清除core 1所使用的L2缓存内容,从而使core 1的软件性能有不确定性。

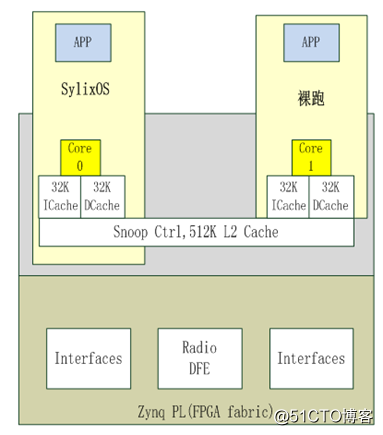

有时,我们需要为core 0 或core 1提供更多的确定性行为,尤其是架构为AMP时。

如图 2.1、图 2.2为SMP与AMP架构图。

图 2.1 SMP架构图

图 2.2 AMP架构图

3.L2 Cache的锁定

通过寄存器的控制可以将L2 Cache锁定在不同core上,这让用户可以将L2 Cache的功能保留在特定的core上。

(1)相关说明

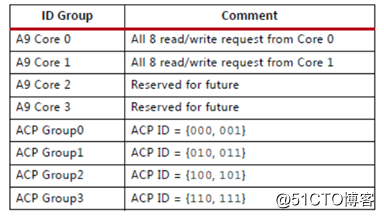

第一:Cache way是分区的宽度,Zynq的L2 Cache有8 Cache ways。

第二:L2 Cache控制器只能被锁定8个不同的方式。

如图 3.1所示,在Zynq 7000中,Cortex-A9 MP核的64个AXI被分为8个可以锁定的组。

图 3.1分组

(2)具体配置

具体的配置说明请参考官方手册《UG585 - Zynq-7000 SoC Technical Reference Manual (ver1.12.2).pdf》,下载链接:https://download.csdn.net/download/ye1223/10811782

配置1:通常情况(L2 Cache 被core 0和core 1共享)

Reg9_d_lockdown0 = 0x0;

Reg9_1_lockdown0 = 0x0;

Reg9_d_lockdown1 = 0x0;

Reg9_1_lockdown1 = 0x0;

配置2:4-0-4方式,每个核用一半(core 0使用Cache way【0..3】;core 1使用Cache way【4..7】)

reg9_d_lockdown0 = 0xFFF0;

reg9_1_lockdown0 = 0xFFF0;

reg9_d_lockdown1 = 0xFF0F;

reg9_1_lockdown1 = 0xFF0F;

配置3:2-4-2方式(core 0使用Cache way【0..1】;core 1使用Cache way【6..7】;两个核共享Cache way【2..5】)

reg9_d_lockdown0 = 0xFFC0;

reg9_1_lockdown0 = 0xFFC0;

reg9_d_lockdown1 = 0xFF03;

reg9_1_lockdown1 = 0xFF03;

配置4:

4013

4013

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?