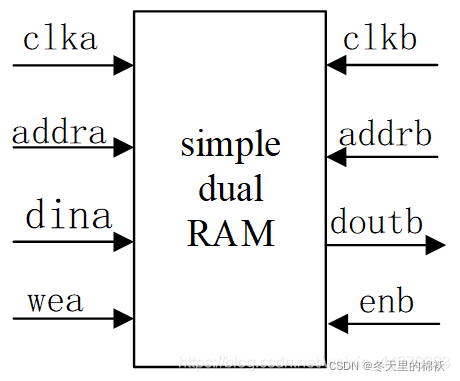

一、伪双端口RAM简介

伪双端有独立的写地址和读地址,一个端口只读,一个端口只写;我们常用的双口RAM就是伪双端口。

输入有一组数据线,两组地址线,两个时钟。

所以一个端口只读,另一个端口只写,但写入和读取的时钟可以不同,且位宽比可以不是1:1。即允许写A的同时读B,且速率可以不同。

二、伪双端口设计代码

//dual port RAM

module sram #(parameter ADDR_WIDTH = 3,

DATA_WIDTH = 8,

MEM_DEPTH = 8)

(

rddata,

wraddr,

rdaddr,

wrdata,

wren,

rden,

wrclk,

rdclk

);

output [DATA_WIDTH-1:0] rddata; //output data

input [DATA_WIDTH-1:0] wrdata; //input data

input [ADDR_WIDTH-1:0] wraddr; //write data address signal

input [ADDR_WIDTH-1:0] rdaddr; //output data address signal

input wren; //write data contral signal

input rden; //read data contral signal

input wrclk; //write data clock

input rdclk; //read data clock

reg [DATA_WIDTH-1:0] rddata;

reg [DATA_WIDTH-1:0]mem[MEM_DEPTH-1:0]; //8*8 bites register

always@(posedge wrclk)

begin

if(wren) begin

mem[wraddr] <= wrdata;

end

end

always@(posedge rdclk)

begin

if(rden) begin

rddata <= mem[rdaddr];

end

end

endmodule三、伪双端口测试代码

module srm_tb #(parameter ADDR_WIDTH = 3,

DATA_WIDTH = 8,

MEM_DEPTH = 8);

reg [DATA_WIDTH-1:0] wrdata;

reg [ADDR_WIDTH-1:0] wraddr;

reg [ADDR_WIDTH-1:0] rdaddr;

reg wren;

reg rden;

reg wrclk;

reg rdclk;

wire [DATA_WIDTH-1:0] rddata;

sram u_sram(

.rddata (rddata),

.wraddr (wraddr),

.rdaddr (rdaddr),

.wrdata (wrdata),

.wren (wren),

.rden (rden),

.wrclk (wrclk),

.rdclk (rdclk)

);

//clk generate

initial

begin

wrclk = 1'b0;

forever

#10 wrclk = ~wrclk;

end

initial

begin

rdclk = 1'b0;

forever

#20 rdclk = ~rdclk;

end

//initial statement and simulation

initial

begin

wren = 1'b1;

rden = 1'b0;

wraddr = 3'b0;

rdaddr = 3'b0;

wrdata = 8'b0;

#40

rden = 1'b1;

#320

wren = 1'b0;

#1000 $finish;

end

//wraddr and rdaddr generate

initial

begin

repeat(7)

begin

#40 wraddr = wraddr + 1'b1;

wrdata = wrdata + 1'b1;

end

end

initial

begin

#40 repeat(7)

#80 rdaddr = rdaddr + 1'b1;

end

//Dump wave of verdi

initial begin

$fsdbDumpfile("sram.fsdb");

$fsdbDumpvars(0);

end

endmodule

935

935

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?