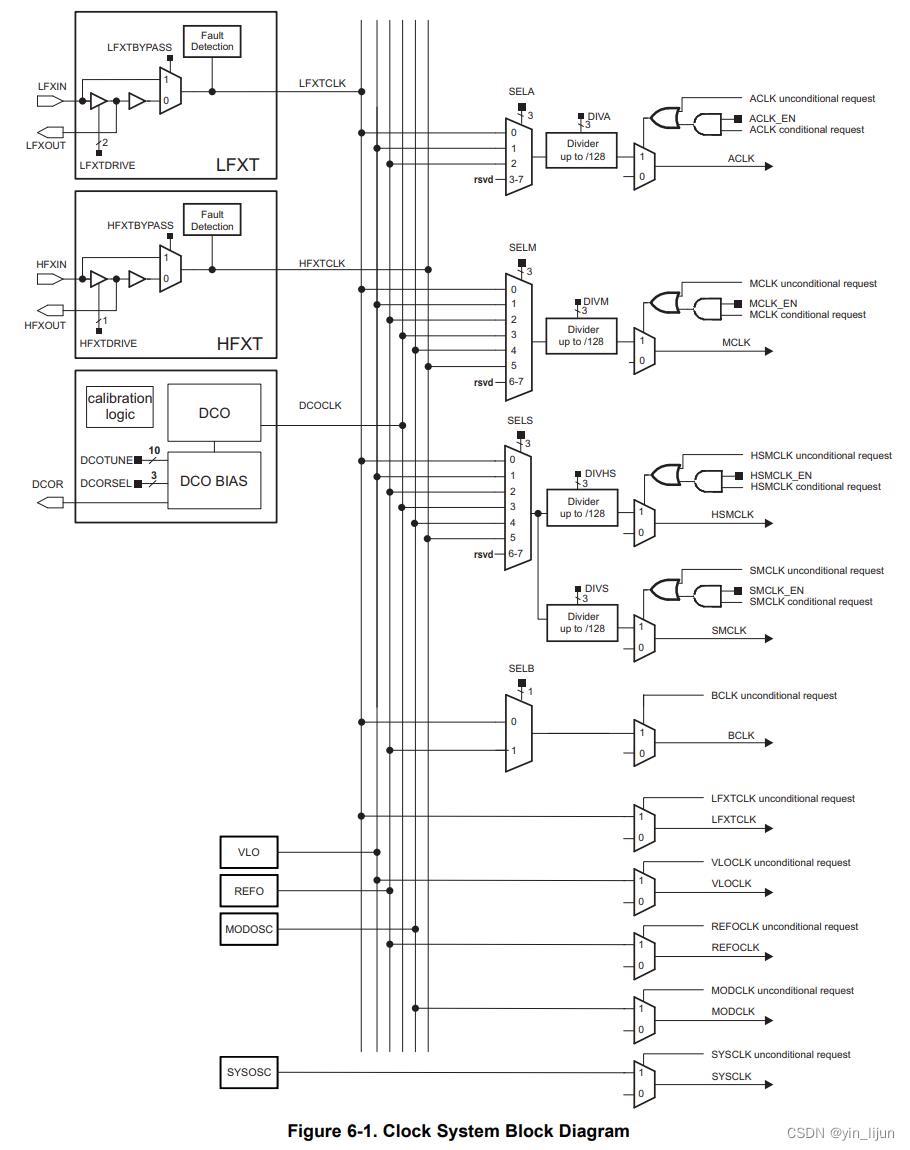

MSP432Pxx-系统时钟框图简介

SEL为选择器,DIV为分频器

外部时钟源

LFXT为外部低速时钟源,HFXT为外部高速时钟源,均需要外接晶振

内部时钟源

DCO数控时钟源,默认频率为3MHz,可通过程序改变频率,使用内部电阻时精度不高,

可外接精密电阻使用,通过DCO可以时钟超频至64MHz。(超频有风险,试玩需谨慎)

VLO超低功耗低频时钟源,典型频率为9.4KHz。

REFO低频时钟源,典型频率为32768Hz和128KHz。

MODOSC模块振荡器,典型频率为25MHz。可做ADC时钟源,采样频率1M。

SYSOSC系统震荡器,典型频率为5MHz。可做ADC时钟源,采样频率200K。

时钟来源

ACLK为辅助时钟,最大时钟频率128KHz,可为各外设提供时钟来源。

MCLK为主时钟,可选择六个时钟源,CPU和滴答定时器即是接在这个时钟上的。

HSMCLK子系统时钟和 SMCLK低速子系统时钟均是给外设使用的。

BCLK低速备用时钟,最大时钟频率限制在32768Hz。

默认时钟设置

当系统reset后或者不进行时钟配置时,会进入内核电压0的模式,等级0的最大时钟

频率为24MHz。

此时ACLK和BCLK都是选择LFXTCLK作为时钟输入,但此时LFXTCLK是禁用的,

LFXT的晶振输入输出引脚此时为通用I/O,需要启用此时钟需要复用端口,所以系统

认为LFXT故障,选择REFOCLK作为时钟来源,此时时钟频率为32768Hz。

外部高速时钟源HFXT也不启用,此时MCLK, HSMCLK, SMCLK时钟来源都是DCO

数控时钟源,此时时钟频率都为3MHz。

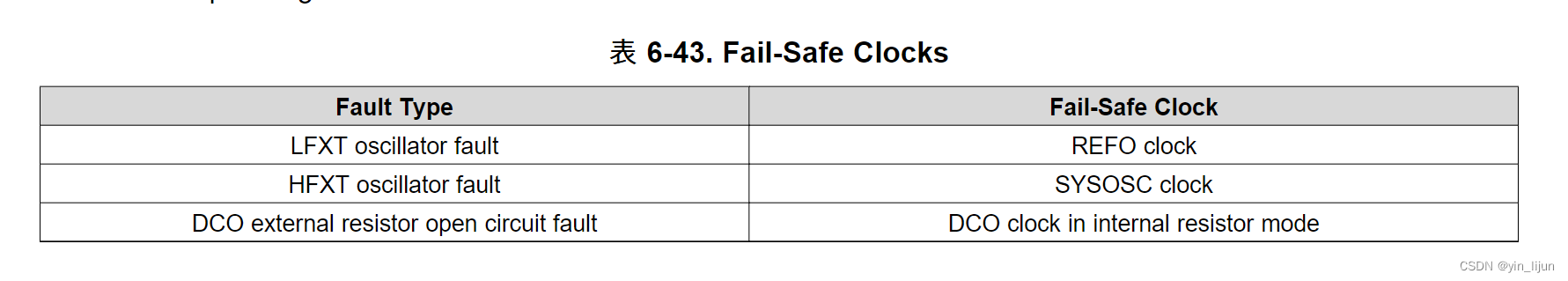

时钟故障机制

Fault Type下时钟源故障后会选择Fail-Safe Clock里的时钟源。

最后一条DCO外接精密电阻故障即开路或者短路时会启用内部电阻,但不精确。

1864

1864

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?