设计一个工作在25MHZ的频率检测器,以检测1MHZ至1GHZ的频率

误差要求尽可能小

基本功能

input cclk crstn //检测器所在时钟信号及其复位信号

input xclk //待测时钟

input start //检测开始标志信号 高有效

output done //检测完成标志信号 高有效

output freq //输出所检测的频率

在xclk稳定后,给start一个周期的1来启动检测。检测完成后,将done置高一个周期,同时输出freq。下一个周期,done至0。检测期间不可开启第二次检测。如上循环。

基本思路

检测器有三个状态:ready,running,finish。可以加入状态信号state控制,其初始状态为ready,以start上升沿,done上升沿为节点来切换。

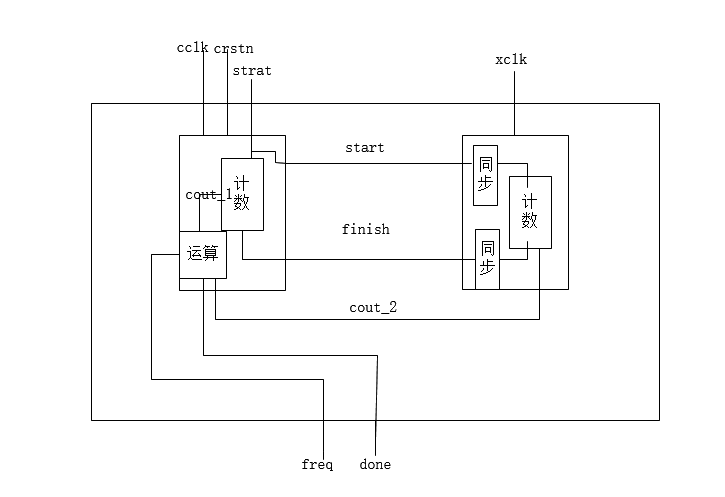

频率检测以计数的模式进行。cclk与xclk同步开始计数。cclk计数到N时,xclk计数停止。比较两个计数器的数值,即可得到xclk频率。

同步:

(1)考虑到精度和占用的资源,采用单bit打拍的方式来同步。同步之后加一个边沿检测。由于亚稳态的原因,可能有1--2个周期的误差。这里在cclk将启动信号送到xclk,计数停止时,在将停止信号由cclk送到xclk,xclk接收到之后,将计数锁死,再传递给cclk,最后在cclk内完成对频率的计算。

(2)对于部分要求比较高的数据,最好采用全握手来实现。

(3)设想中,开启信号与结束信号都有延迟,延迟大体相差不多,由于亚稳态可能导致其有一两个周期左右的延迟。

1MHZ=10^6HZ 1GHZ=10^9HZ 1GHZ=1000MHZ //1HZ即为1s内电平反转一下,即一个上升沿。不采用下降沿是因为上升沿更准。

cclk计数模块。为了相对精确与相对节约,延迟大概算2个,我们计数255个数来控制精度是绰绰有余的.xclk计数模块。1GHZ最高计数10240,共计14位即可。

运算模块。cnt_1:cnt_2=25MHZ:XMHZ。即X=25*cout_2/(2^8)。乘除还是实现起来比较复杂的,为了节约资源我们这样算。X=(2^4+2^3+1)/2^8 * cout_2;

X=cout_2右移四位加右移五位加右移八位。由于要保留小数,先对cout_2末位加上八位0,在分别右移。以第九位为个位,再根据第八位结果进位,即可得出运算结果。即运算部分要22位!(其实也可以分成8位,14位两个部分)

注意:

(1)在xclk域内计时器计数截止之后,需要将数据稳定一段时间方便cclk采集。cclk采集之后,也需要返回一个数据告知xclk计数器清零方便下一轮计数。

(2)xclk对复位信号的要求是怎样的?可以采用异步复位同步释放的方式来做xclk的复位信号。

具体模块图

代码部分就不写了,思路还是内个思路。

以上思路博主已仿真验证,注意运算部分与跨时钟域的处理,绿灯ez. O^O

本文描述了一个用于检测1MHz到1GHz频率的检测器设计,基于25MHz参考时钟。设计采用了计数器同步和单bit打拍方式减少误差,同时考虑了亚稳态的影响和资源效率。检测器有三个状态:ready、running和finish,通过状态机控制。计数模块和运算模块分别处理cclk和xclk的计数,以确定待测时钟频率。运算部分进行了简化以节省资源,且仿真已验证设计的正确性。

本文描述了一个用于检测1MHz到1GHz频率的检测器设计,基于25MHz参考时钟。设计采用了计数器同步和单bit打拍方式减少误差,同时考虑了亚稳态的影响和资源效率。检测器有三个状态:ready、running和finish,通过状态机控制。计数模块和运算模块分别处理cclk和xclk的计数,以确定待测时钟频率。运算部分进行了简化以节省资源,且仿真已验证设计的正确性。

2730

2730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?