暑期高阶实验

目录

7.15 启动会

主要内容:

参与高阶实验启动会,了解各个项目大致情况,选定暑期实践具体项目。

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可编程逻辑器件,属于专用集成电路(ASIC)领域的一种半定制电路。通过硬件描述语言(如Verilog或VHDL)进行编程,将逻辑功能加载到芯片中,从而实现定制化的数字电路设计。与传统的ASIC不同,FPGA在出厂后仍可重新编程,能够灵活适应不同的应用需求,同时避免了ASIC高昂的开发成本和长开发周期的问题。

一 开源工具

多FPGA系统的硬件逻辑划分是指将一个复杂的逻辑设计分割成多个部分,并将这些部分分别映射到不同的FPGA芯片中执行。这种划分的目的是在单颗FPGA无法容纳整个设计的情况下,通过多颗FPGA的协同工作来实现高性能、高可靠性的系统。这种技术广泛应用于芯片验证、原型设计和高性能计算等领域

二 系统外设(网络外设)

项目目标:在开源高性能香山“昆明湖”的FPGA原型验证环境上进行网络外设扩展

这个项目的核心目标是在一个已经存在的、基于FPGA的香山“昆明湖”处理器原型系统上,添加网络通信能力。具体来说:

-

平台: 开源高性能RISC-V核“香山”的特定版本“昆明湖”,并且这个版本已经有一个在FPGA上的原型验证环境。这意味着基础硬件平台(FPGA型号、板载资源、已有的“昆明湖”实现)是确定的。

-

功能: 添加“网络外设”。这通常意味着实现一个网络接口控制器(NIC),比如以太网MAC(Media Access Control),并可能需要配合PHY(Physical Layer)芯片(虽然PHY有时也集成在FPGA或板上)来实现物理层的连接。

-

方式: 通过扩展,即在不破坏原有系统功能的前提下,增加新的硬件模块和软件驱动/协议栈支持,使得“昆明湖”系统能够通过网络发送和接收数据。

-

目的: 使得这个FPGA原型系统能够与外部网络设备(如PC、交换机)通信,便于进行更复杂的系统级测试、数据交换、远程控制或作为网络终端使用。

二 系统外设(可信I/O)

项目目标:在开源高性能RISC-V核的FPGA原型验证环境上实现DMA隔离

目标解读:

这个项目的核心是在一个基于FPGA的原型系统(运行开源高性能RISC-V核)上,实现直接内存访问(DMA)隔离。这意味着:

-

平台: 同样是基于FPGA的开源高性能RISC-V核(可能是香山系列或其他)的原型验证环境。这通常包含RISC-V处理器核、内存(DDR)、各种外设(如NIC、NVMe、USB等)以及连接它们的总线(如AXI)。

-

核心概念: DMA隔离 (DMA Isolation)。DMA允许外设(如网卡、硬盘控制器)直接读写主内存,而无需CPU的持续干预,从而提高I/O性能。然而,这也带来了安全风险:一个不受信任的外设(例如,被攻击的网络接口卡)如果能够任意访问内存,就可能窃取敏感数据(如密钥、密码)或破坏系统。DMA隔离的目标就是限制DMA访问的范围,确保一个外设只能访问其被授权的内存区域,防止其访问其他进程或操作系统的内存。

-

实现方式: 项目提到了使用 IOPMP 模块,这是一个具体的实现技术。IOPMP(Input/Output Page Map Protection)是一种机制,允许操作系统(如Linux)通过页表条目来控制DMA设备对内存的访问权限,提供类似CPU虚拟化中内存隔离的机制。

-

最终目的: 在FPGA原型上验证DMA隔离机制的有效性,确保外设的DMA操作不会越权访问内存,提升系统的安全性。项目还进一步探索了结合可信执行环境(TEE)*构建*可信I/O通路,这旨在将敏感的I/O操作放在一个隔离、受保护的执行环境中进行,提供更强的安全保障。

三 应用加速(transformer)

数据流Transformer模型加速器是一种硬件或软件优化方案,其核心目标是通过高效的数据流管理,降低Transformer模型计算和存储的开销,从而提升模型的运行速度和资源利用率。Transformer模型因其复杂的自注意力机制和多头注意力机制,计算量大且内存占用高,这使其在部署时面临挑战。数据流加速器通过优化数据传输路径和计算流程,显著缓解了这些问题

三 应用加速(同态加密)Fully Homomorphic Encryption, FHE

开源FHE加速器调研。

FHE(全同态加密)是一种先进的加密技术,允许在加密数据上直接进行计算,而无需解密。这种特性使其在隐私保护计算场景中具有极高的应用价值,例如云计算、机器学习、区块链等。然而,FHE的计算开销巨大,密文操作通常比明文操作慢数千倍甚至上万倍,这限制了其广泛应用。FHE加速器通过硬件或软件优化,旨在降低计算开销,提高计算效率,从而推动FHE技术的落地

四 平台优化

这个项目旨在通过创建一个智能的“中间层”工具,极大地简化 GitLab Runner 的跨平台部署和注册过程,将其从一项繁琐、易出错的手动任务转变为简单的一键操作。这不仅提高了 CI/CD 环境的部署效率,也使得动态扩展 CI/CD 算力变得更加容易和可靠,完全符合“跨平台算力一键接入”的愿景。实现这个工具需要综合运用脚本编程、系统管理、网络通信、API 集成等多方面技能。

CI (Continuous Integration) - 持续集成 意思: 持续地将代码集成到共享的主干(main branch)或发布分支中。

7.16 基础知识学习

时间:8小时

主要内容:

掌握vivado使用(IP Integrator-> RTL Analysis-> Systhesis->Bitstream),了解计算机网络基本知识。

需要了解的基础知识: 1.Vivado的基本操作 2.网络相关知识,PHY,MAC,SGMII等概念 3.AXI协议理论

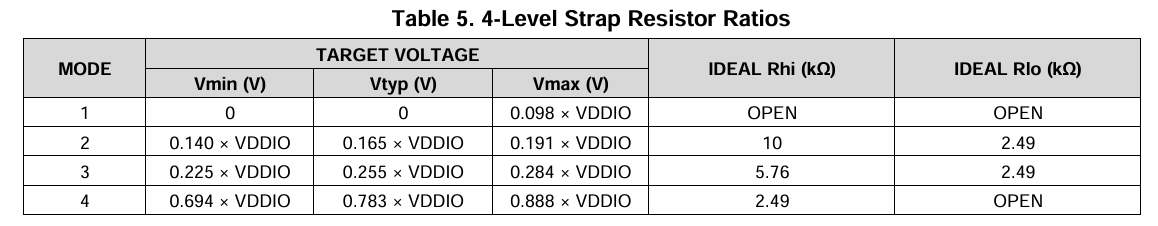

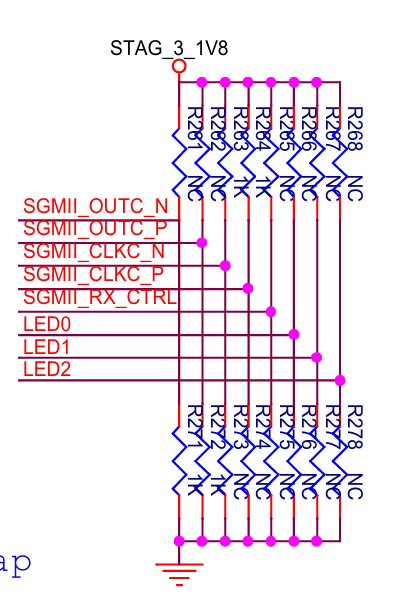

近期可以开展的工作: 1.明白如何看电路图,根据电路图查找并阅读芯片手册,了解电路工作原理 2.搞清楚NP19A_SCH_ETH原理图文件网络部分的工作原理 3.调研是否可以通过Tri-Mode Ethernet Media Access Controller 这个IP将网络功能使用起来

一、PHY(物理层)

PHY(Physical Layer,物理层)是OSI模型中的第一层,负责在物理介质(如电缆、光纤)上传输和接收原始比特流。它是数字信号与模拟信号之间的桥梁,确保数据在硬件层面的可靠传输。

主要功能

-

信号调制与编码:将MAC层发送的数字信号转换为适合物理介质传输的模拟信号,例如差分电压或光脉冲。

-

时钟恢复与同步:从接收信号中提取时钟信息,确保发送端与接收端时序一致。

-

链路检测与自协商:通过链路脉冲检测物理连接状态,并支持自动协商功能,选择最佳速率和双工模式。

-

错误检测与校正:使用前向纠错技术(如RS-FEC)减少高速传输中的误码率。

应用场景

-

网络接口卡(NIC):如Realtek RTL8211F,用于PC网卡或嵌入式设备。

-

交换机与路由器:多端口PHY芯片(如Broadcom BCM5396)支持高密度端口设计。

-

光纤模块:将电信号转换为光信号,用于长距离数据传输。

PHY层直接与物理介质交互,为数据链路层(MAC层)提供可靠的物理传输基础。

二、MAC(媒体访问控制)

MAC(Media Access Control,媒体访问控制)位于OSI模型的数据链路层(第二层),负责管理数据帧的传输和接收,确保数据在局域网内的有序、无冲突传输。

主要功能

-

帧同步与分帧:识别数据帧的开始和结束,确保接收端能正确解析数据。

-

介质访问控制:通过CSMA/CD协议(冲突检测)避免数据冲突,支持全双工和半双工模式。

-

唯一标识设备:MAC地址是设备的物理地址,用于局域网内设备间的通信。

应用场景

-

局域网通信:如交换机通过MAC地址表转发数据帧。

-

ARP协议:将IP地址解析为MAC地址,用于数据链路层通信。

-

网络安全:通过MAC地址过滤限制设备访问网络。

MAC层接收来自网络层的数据包,将其封装为数据帧,并通过物理层(PHY)发送到网络中。

三、SGMII(串行千兆媒体无关接口)

SGMII(Serial Gigabit Media Independent Interface)是一种用于千兆以太网的串行接口标准,用于连接MAC层和PHY层,减少引脚数量,提高通信效率。

主要功能

-

引脚精简:通过差分串行信号,将数据线从GMII的8位减少到1对发送+1对接收,节省PCB面积。

-

高速传输:支持1Gbps速率,信号速率为1.25Gbps,采用8B/10B编码技术。

应用场景

-

光纤通信:通过光模块实现长距离传输。

-

网络设备:如交换机和路由器,用于MAC与PHY之间的通信。

-

工业与嵌入式系统:支持工业以太网和FPGA网络功能。

SGMII是MAC层与PHY层之间的接口标准,简化了两者之间的通信,同时支持多种物理介质。

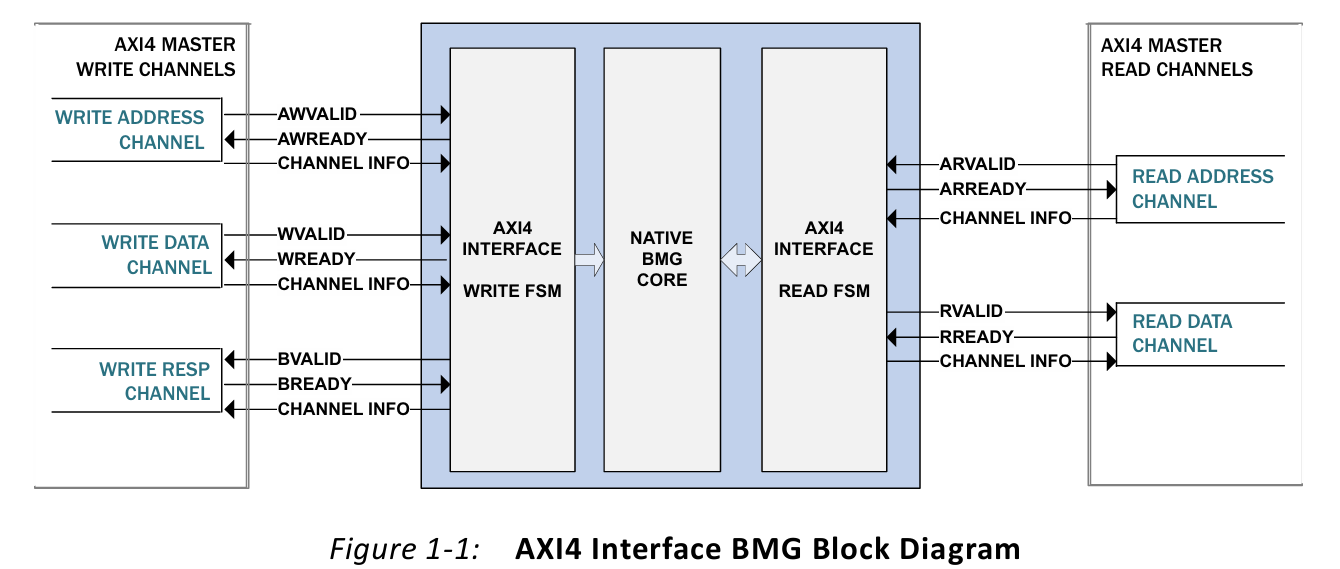

四 AXI协议理论

AXI总线是AMBA总线的子集。AMBA全称Advanced Microcontroller Bus Architecture,即高级微控制总线架构。是ARM 公司推出的一种用于片上系统(SOC)设计的开放标准总线协议

常见名词及英文释义

-

host 主机

-

ISP (internet service provider) 互联网服务提供者

-

IP地址(Internet Protocol Address)是互联网协议地址的简称,用于唯一标识网络中的设备。每个连接到网络的设备(如计算机、手机、服务器等)都需要一个IP地址,以便在网络中进行通信。IP地址由32位(IPv4)或128位(IPv6)的二进制数组成,通常以点分十进制的形式表示,例如192.168.1.1

互联网的组成

边缘部分:一台台主机

核心部分:网络、路由器

AXI

(Advanced eXtensible Interface,高级可扩展接口)是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)协议的一部分,是一种面向高性能、高带宽、低延迟的片上总线协议。它被广泛应用于现代SoC(System-on-Chip,片上系统)设计中,以满足复杂多核系统的数据通信需求。以下从定义、特点、核心机制、应用场景和优势等方面为您详细解析AXI协议。

以太网

是由Xerox公司于20世纪70年代在帕洛阿尔托研究中心(PARC)开发的一种基带局域网技术。1980年,Xerox与Intel、DEC公司联合发布了第一个以太网标准,即DIX Ethernet V1。随后,IEEE于1983年制定了IEEE 802.3标准,明确了以太网的技术规范。以太网作为局域网通信的事实标准,取代了其他局域网技术(如令牌环、FDDI等),成为目前应用最广泛的网络技术。

DHCP

(Dynamic Host Configuration Protocol,动态主机配置协议)

通常被应用在大型的局域网络环境中,主要作用是集中的管理、分配IP地址,使网络环境中的主机动态的获得IP地址、Gateway地址、DNS服务器地址等信息,并能够提升地址的使用率。

DHCP协议采用客户端/服务器模型,主机地址的动态分配任务由网络主机驱动。当DHCP服务器接收到来自网络主机申请地址的信息时,才会向网络主机发送相关的地址配置等信息,以实现网络主机地址信息的动态配置。DHCP具有以下功能:

保证任何IP地址在同一时刻只能由一台DHCP客户机所使用。 DHCP应当可以给用户分配永久固定的IP地址。 DHCP应当可以同用其他方法获得IP地址的主机共存(如手工配置IP地址的主机)。 DHCP服务器应当向现有的BOOTP客户端提供服务。 DHCP有三种机制分配IP地址:

自动分配方式(Automatic Allocation),DHCP服务器为主机指定一个永久性的IP地址,一旦DHCP客户端第一次成功从DHCP服务器端租用到IP地址后,就可以永久性的使用该地址。 动态分配方式(Dynamic Allocation),DHCP服务器给主机指定一个具有时间限制的IP地址,时间到期或主机明确表示放弃该地址时,该地址可以被其他主机使用。 手工分配方式(Manual Allocation),客户端的IP地址是由网络管理员指定的,DHCP服务器只是将指定的IP地址告诉客户端主机。 三种地址分配方式中,只有动态分配可以重复使用客户端不再需要的地址。

DHCP消息的格式是基于BOOTP(Bootstrap Protocol)消息格式的,这就要求设备具有BOOTP中继代理的功能,并能够与BOOTP客户端和DHCP服务器实现交互。BOOTP中继代理的功能,使得没有必要在每个物理网络都部署一个DHCP服务器。RFC 951和RFC 1542对BOOTP协议进行了详细描述。

RMII

是 Reduced Media Independent Interface 的缩写,中文通常翻译为 简化介质无关接口。

它是一种用于连接以太网媒体访问控制器(MAC)和物理层(PHY)芯片的接口标准,是IEEE 802.3标准的一部分。

一、RMII 的设计目的

传统的以太网 MII(Media Independent Interface)接口需要较多的信号线(例如,对于 10/100 Mbps 的 MII,需要 4 对数据线、时钟线、控制线等,共 16 或 20 根信号线),这在空间受限或希望降低成本的嵌入式系统中可能不够理想。

RMII 的主要设计目的是:

-

减少信号线数量:通过更高效的数据传输方式,显著减少 MAC 和 PHY 之间所需的物理连接线。

-

降低系统复杂度和成本:更少的引脚意味着更小的芯片封装、更简单的 PCB 布局和潜在的更低成本。

-

提高接口效率:在减少信号线的同时,保持或提高数据传输的有效带宽。

MDI

是 Medium Dependent Interface 的缩写,中文通常翻译为 介质相关接口。

它是 OSI 模型物理层(Layer 1)的一部分,定义了网络设备(如网卡、交换机、集线器)的物理端口如何与特定类型的传输介质(如双绞线、光纤、同轴电缆等)进行连接。

理解 MDI 需要提到它的“孪生兄弟”——MDIX (Medium Dependent Interface Crossover)。

-

MDI (直通线接口):发送(Tx)和接收(Rx)线对是分开的。例如,设备 A 的发送线连接到设备 B 的接收线,设备 A 的接收线连接到设备 B 的发送线。这通常用于连接不同类型的设备,如计算机(终端)连接到交换机或集线器。传统上,这需要使用直通线 (Straight-Through Cable)。

-

MDIX (交叉线接口):发送和接收线对在物理连接器内部就已经进行了交叉。也就是说,发送线对直接连接到另一个 MDIX 端口的发送线对,接收线对直接连接到另一个 MDIX 端口的接收线对。这通常用于连接相同类型的设备,如交换机连接到交换机,或计算机连接到计算机(对等连接)。传统上,这需要使用交叉线 (Crossover Cable)

MII

(Medium Independent Interface, 媒体独立接口): MII 支持 10Mbps 和 100Mbps 的操作,数据位宽为 4 位 在 100Mbps 传输速率下,时钟频率为 25Mhz 在 10Mbps 传输速率下,时钟频率为 2.5Mhz

RMII

(Reduced MII): RMII 是 MII 的简化版, 数据位宽为 2 位 在 100Mbps 传输速率下,时钟频率为 50Mhz 在 10Mbps 传输速率下,时钟频率为 5Mhz

GMII

(Gigabit MII): GMII 接口向下兼容 MII 接口, 支持 10Mbps、 100Mbps 和 1000Mbps 的操作,数据位宽为 8 位 在 1000Mbps 传输速率下,时钟频率为 125Mhz 在 100Mbps 传输速率下,时钟频率为 25Mhz 在 10Mbps 传输速率下,时钟频率为 2.5Mhz

RGMII

(Reduced GMII): RGMII 是 GMII 的简化版,数据位宽为 4 位 在 1000Mbps 传输速率下,时钟频率为 125Mhz,在时钟的上下沿同时采样数据 在 100Mbps传输速率下,时钟频率为25MHz,为单个时钟沿采样 在 10Mbps传输速率下,时钟频率为2.5MHz,为单个时钟沿采样 在千兆以太网中,常用的接口为 RGMII 和 GMII 接口。 RGMII 接口的优势是同时适用于10M/100M/1000Mbps 通信速率,同时占用的引脚数较少。但 RGMII 接口也有其缺点,就是在 PCB 布线时需要尽可能对时钟、控制和数据线进行等长处理,且时序约束相对也更为严格。

MDIO和MDC

是现代以太网通信中两个重要的信号线,它们共同构成了MDIO(Management Data Input/Output)接口,用于MAC(介质访问控制)层与PHY(物理层)之间的管理通信。下面我将从定义、功能、协议细节以及应用场景等方面对这两个概念进行详细解析。

一、MDIO和MDC的基本定义

MDIO和MDC是IEEE 802.3以太网标准中定义的一对信号线,专门用于MAC控制器与PHY芯片之间的管理通信。MDIO全称为"Management Data Input/Output",即管理数据输入输出;而MDC全称为"Management Data Clock",即管理数据时钟。

-

MDIO:这是一条双向数据信号线,用于在MAC和PHY之间传输控制和管理信息。它连接MAC控制器和PHY芯片,允许两者交换配置信息、状态信息以及寄存器数据。

-

MDC:这是一条单向时钟信号线,由MAC控制器驱动,为MDIO上的数据传输提供时钟同步。MAC通过MDC时钟信号来同步PHY对MDIO信号的采样或驱动。

2. PWDN 的含义

PWDN 是 “Power Down” 的缩写,通常用于表示一个低功耗控制信号。在硬件设计中,PWDN 信号用于控制芯片或模块的电源状态,例如:

-

激活状态:当 PWDN 信号为高电平时,设备正常工作。

-

关闭状态:当 PWDN 信号为低电平时,设备进入低功耗模式或完全关闭电源,以节省电能。

在 ZU5EV 芯片或相关开发板中,PWDN 信号可能用于控制芯片的某个部分(如 PS 或 PL)的电源状态,以实现动态功耗管理。

电路原理图的阅读

电路原理图(Schematics

1. 图形符号

图形符号是构成电路图的主体。例如小长方形表示电阻器

![]()

两道短杠表示电容器

![]()

连续的半圆形表示电感器

![]()

等等。各个元器件图形符号之间用连线连接起来,就可以反映出电路结构。需要说明的是这是国标GB4728,我们接触的很多是欧美国家的电路图,电阻是

2. 文字符号

文字符号是构成电路图的重要组成部分。为了进一步强调图形符号的性质,同时也为了分析、理解和阐述电路图的方便,在各个元器件的图形符号旁,标注有该元器件的文字符号。例如“R”表示电阻器,“C”表示电容器,“L”表示电感器,“VT”表示晶体管,“IC”表示集成电路等。

除了规定统一的图形符号和文字符号外,电路图还遵循一定的画法规则。了解并掌握电路图的一般画法规则,对于看懂电路图是必不可少的。

-

R - 电阻器(Resistor) 用于限制电流或分压,单位为欧姆(Ω)。

-

C - 电容器(Capacitor) 用于储存电荷或滤波,单位为法拉(F)。

-

L - 电感器(Inductor) 用于储存磁能或滤波,单位为亨利(H)。

-

VT - 晶体管(Transistor) 通常指双极结型晶体管(BJT)或场效应晶体管(FET),用于放大或开关信号。

-

IC - 集成电路(Integrated Circuit) 包含多个电子元件(如逻辑门、放大器等)的微型芯片。

其他常见元件标识符

-

D - 二极管(Diode)

-

ZD - 稳压二极管(Zener Diode)

-

LED - 发光二极管(Light Emitting Diode)

-

SW 或 S - 开关(Switch)

-

B - 电池(Battery)或变压器(Transformer)

-

X 或 XTAL - 晶振(Crystal Oscillator)

A. 电路图的信号处理流程方向

电路图中信号处理流程的方向一般为从左到右,即将先后对信号进行处理的各个单元电路,按照从左到右的方向排列,这是最常见的排列形式。

B.连接导线

元器件之间的连接导线在电路图中用实线表示。导线的连接与交叉处画有一圆点,表示两导线连接在一起。交点处无圆点,表示两导线交叉而不连接。跨页的连线通常起一个名字,并在旁边有些数字,表明连接到何处。

3.引脚旁边的小红圈表示低电平有效。

引脚名称上面的横线也表示低电平有效。

7.17 vcu128电路阅读、TRi-mode

时间:8小时

主要内容:

vcu128电路原理图阅读,Tri-mode论文阅读

FPGA电源引脚

的命名通常基于其功能、供电对象和电气特性,命名逻辑清晰且具有行业惯例。以下是针对VCCINT、VCCBRAM、VCCAUX、VCCO和VCCAUX_IO等常见电源引脚命名的详细解释:

1. VCCINT

-

命名逻辑: VCCINT是“Voltage Common Collector Internal”的缩写,其中“VCC”代表常见的供电电压符号,“INT”代表“Internal”(内部)。

-

功能说明: VCCINT专门为FPGA内部逻辑单元供电,如查找表(LUT)、触发器和其他逻辑模块。它是FPGA运行的核心供电引脚,电压通常为1.2V、1.5V、1.8V等,具体取决于芯片的制造工艺和设计需求。

-

命名依据: 在电子工程中,供电引脚常以“VCC”开头,后接供电对象的名称或功能模块。例如,VCCINT的命名直接表明其是为FPGA内部逻辑供电的电压引脚。

2. VCCBRAM

-

命名逻辑: VCCBRAM是“Voltage Common Collector Block RAM”的缩写,其中“BRAM”代表“Block RAM”(块存储器)。

-

功能说明: VCCBRAM专门为FPGA中的Block RAM供电,用于支持片上存储器的操作。这种供电方式可以确保RAM模块的稳定性和性能。

-

命名依据: 类似于VCCINT,VCCBRAM的命名也遵循“VCC + 供电对象”的规则,直接反映了其供电目标为Block RAM。

3. VCCAUX

-

命名逻辑: VCCAUX是“Voltage Common Collector Auxiliary”的缩写,其中“AUX”代表“Auxiliary”(辅助)。

-

功能说明: VCCAUX为FPGA的辅助电路供电,如时钟管理单元(如PLL和MMCM)、模拟电路和其他外围模块。这种电压通常为1.8V,是FPGA设计中不可或缺的一部分。

-

命名依据: “AUX”表示辅助功能,命名逻辑表明该引脚是为FPGA的非核心但重要的辅助模块供电。

4. VCCO

-

命名逻辑: VCCO是“Voltage Common Collector Output”的缩写,其中“O”代表“Output”(输出)。

-

功能说明: VCCO为FPGA的I/O引脚供电,电压范围通常为1.2V、1.5V、1.8V、2.5V或3.3V,具体取决于外部接口的电气特性。每个I/O Bank可以独立供电,以适应不同的外部设备需求。

-

命名依据: “VCCO”直接表明其是为输出接口供电的电压引脚,命名逻辑简洁明了。

5. VCCAUX_IO

-

命名逻辑: VCCAUX_IO是“Voltage Common Collector Auxiliary Input/Output”的缩写,其中“IO”代表“Input/Output”(输入/输出)。

-

功能说明: VCCAUX_IO为高性能I/O电路供电,如高速差分信号接口(如LVDS)。在高性能模式下,该引脚的电压可能需要提升至2.0V,以支持更高的信号速率。

-

命名依据: 该命名结合了辅助供电(AUX)和I/O接口供电的功能,表明其是为高性能I/O电路供电的专用电压引脚。

MGTAVCC

-

定义

:MGTAVCC 是 “Multi-Gigabit Transceiver Auxiliary Voltage Common Collector” 的缩写,其中:

-

MGT:代表 Multi-Gigabit Transceiver,即高速收发器模块。

-

Auxiliary:表示这是辅助电压,通常用于模拟电路部分。

-

VCC:代表供电电压。

-

-

功能:MGTAVCC 专门为 FPGA 内部的高速收发器模块(如 GTX 或 GTH)的模拟电路部分提供电源。这些模拟电路负责处理高速信号的调制、解调和时钟恢复等任务,因此 MGTAVCC 的稳定性对收发器的性能至关重要。

1. LN、LO、LS 的可能含义

-

LN(Low Noise) 可能表示该电源引脚或电路设计具有低噪声特性。在高速收发器供电中,低噪声电源是保证信号质量的关键,因此 LN 可能用于标识该引脚的电源设计需要满足低噪声要求。

-

LO(Low Output 或 Logic Output) LO 可能与电源输出的电压电平有关,例如低电压输出或逻辑电平输出。在 FPGA 设计中,某些电源引脚可能需要提供特定的逻辑电平以匹配内部电路或外部接口。

-

LS(Low Speed 或 Low Swing) LS 可能与信号速率或电压摆幅相关。例如,低速率信号或低电压摆幅信号可能需要特定的电源配置来减少功耗或干扰。

2. RN、RO、RS 的可能含义

-

RN(Reference Node 或 Reference Noise) RN 可能表示参考节点或参考噪声。在高速电路设计中,参考节点用于提供稳定的基准电压,而参考噪声则可能指电源噪声的参考值。

-

RO(Reference Output 或 Reference Oscillator) RO 可能与参考输出或参考振荡器有关。例如,某些电源引脚可能需要为振荡器电路提供稳定的电源,以确保时钟信号的准确性。

-

RS(Reference Supply 或 Resistor Sense) RS 可能表示参考电源或电阻感测。在电源管理中,参考电源为其他电路提供基准电压,而电阻感测则用于监控电流或电压。

3. 与 MGTAVCC 的关系

这些后缀可能与 MGTAVCC 的电源设计或功能扩展有关。例如:

-

在高速收发器供电中,可能需要针对不同性能需求设计不同电源引脚,LN、LO、LS 等后缀可能用于区分不同电源的噪声特性或输出电平。

-

RN、RO、RS 则可能与电源的参考特性或监控功能相关,确保 MGTAVCC 供电的稳定性和信号完整性。

MGTAVTT

的全称是 “Multi-Gigabit Transceiver Analog Termination VTT”。

可以分解理解:

-

MGT: Multi-Gigabit Transceiver(多吉比特收发器),指的是 FPGA 中用于高速串行通信的模块。

-

A: Analog(模拟),表示这部分电路是模拟性质的。

-

VTT: Voltage Termination Terminal(终端电压端),通常指用于终端匹配的电压。

所以,MGTAVTT 指的是为 FPGA 内部多吉比特收发器的模拟终端匹配电路提供电源的引脚

HBM

是 “High Bandwidth Memory” 的缩写,即高带宽内存。这是一种基于 3D 堆叠技术的高性能 DRAM,主要用于提升数据传输带宽,降低功耗,并缩小芯片体积。HBM 广泛应用于高性能计算、人工智能(AI)和高带宽需求的场景,如 GPU 和 FPGA 中的内存模块

1. QDR4的定义与分类

QDR4(Quad Data Rate 4)是四倍数据速率同步SRAM的第四代产品,属于静态随机存取存储器(SRAM)的一种。与动态随机存取存储器(DRAM,如DDR4)不同,SRAM是一种非易失性存储器,主要用于需要高速数据访问的场景。

RLD3

Memory Data” 指的是与 RLDRAM 3(Reduced Latency DRAM 3)相关的内存数据。

JTAG

JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。Jtag用的比较多的是单片机的在线仿真,当然也有ISP在线仿真的

UART

UART是一种通用串行数据总线,用于异步通信。该总线双向通信,可以实现全双工传输和接收。主要是用作串口通信的,还有一种SPI通信。

SPI

(Serial Peripheral Interface)是一种同步串行通信协议,常用于微控制器与外围设备之间的高速数据传输。

USB

在嵌入式系统开发中,常作为与其他接口(如 UART 和 JTAG)转换的桥梁,便于调试和通信。

I2C0

PORT EXTENDER"指的是基于I2C(Inter-Integrated Circuit)通信协议的端口扩展器。这种扩展器主要用于解决嵌入式系统中端口数量不足的问题,通过I2C总线扩展额外的GPIO(通用输入/输出)端口,从而连接更多外设。

I2C(Inter-Integrated Circuit)总线是一种由飞利浦公司(现恩智浦半导体)于1982年开发的串行通信协议,主要用于集成电路之间的通信。

SFP

( small form-factor pluggable)称为小封装热拔插光模块,应用于电信行业和光通信,它主要由光电子器件(光发射器、光接收器)、功能电路和光接口等部分组成,主要作用就是实现光纤通信中的光电转换和电光转换功能。

FMC

(FPGA Mezzanine Card)接口

相关。FMC是一种用于扩展FPGA功能的接口标准,通常用于连接高速接口模块或定制硬件

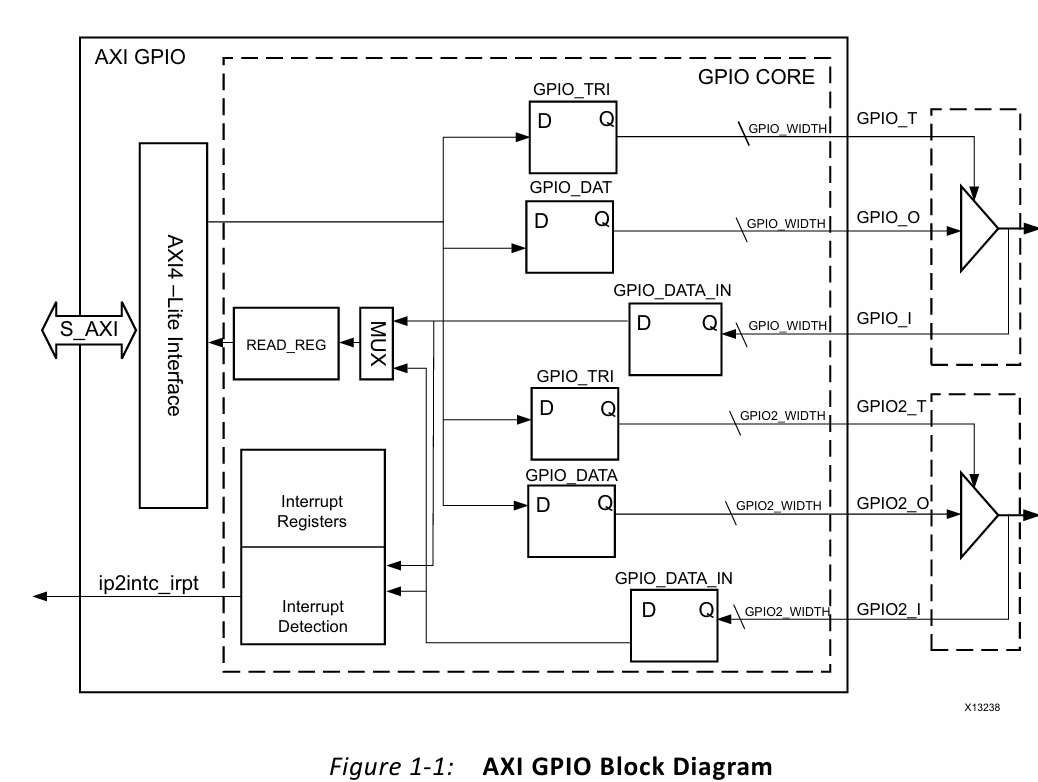

GPIO

是什么? General Purpose Input Output 通用功能输出输出 GPIO就是从芯片内部引出来一根功能复用的口线(电线) 功能复用是指:GPIO的引脚可以由CPU配置成不同的功能 比如:输入功能 输出功能 模拟功能 复用功能等等

RJ45

(Registered Jack-45)是一种标准化网络接口,由美国电子工业协会(EIA)和电信行业协会(TIA)制定。它的名称来源于“注册插孔”(Registered Jack)和接口编号“45”。RJ45接口通常采用8P8C(8位置8触点)设计,支持通过双绞线进行高速数据传输,是局域网(LAN)和广域网(WAN)中最常见的连接器类型

跳线接口(Jumper Pin)

在电路板设计中,JP1通常代表第一个跳线接口(Jumper Pin)。跳线是一种用于连接电路板上两个分离节点的导线,主要用于调整电路参数或实现某些功能。例如,在主板设计中,JP1可能用于调整电压、外频等设置。

tri-mode 阅读

7.18 项目初始

时间:8小时

主要内容:

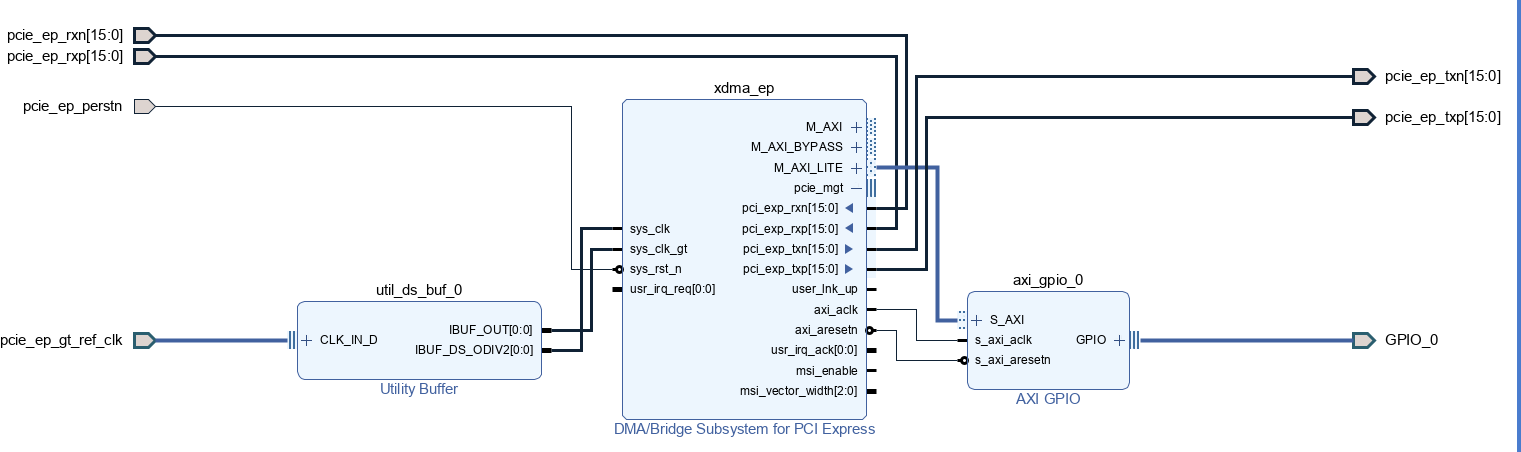

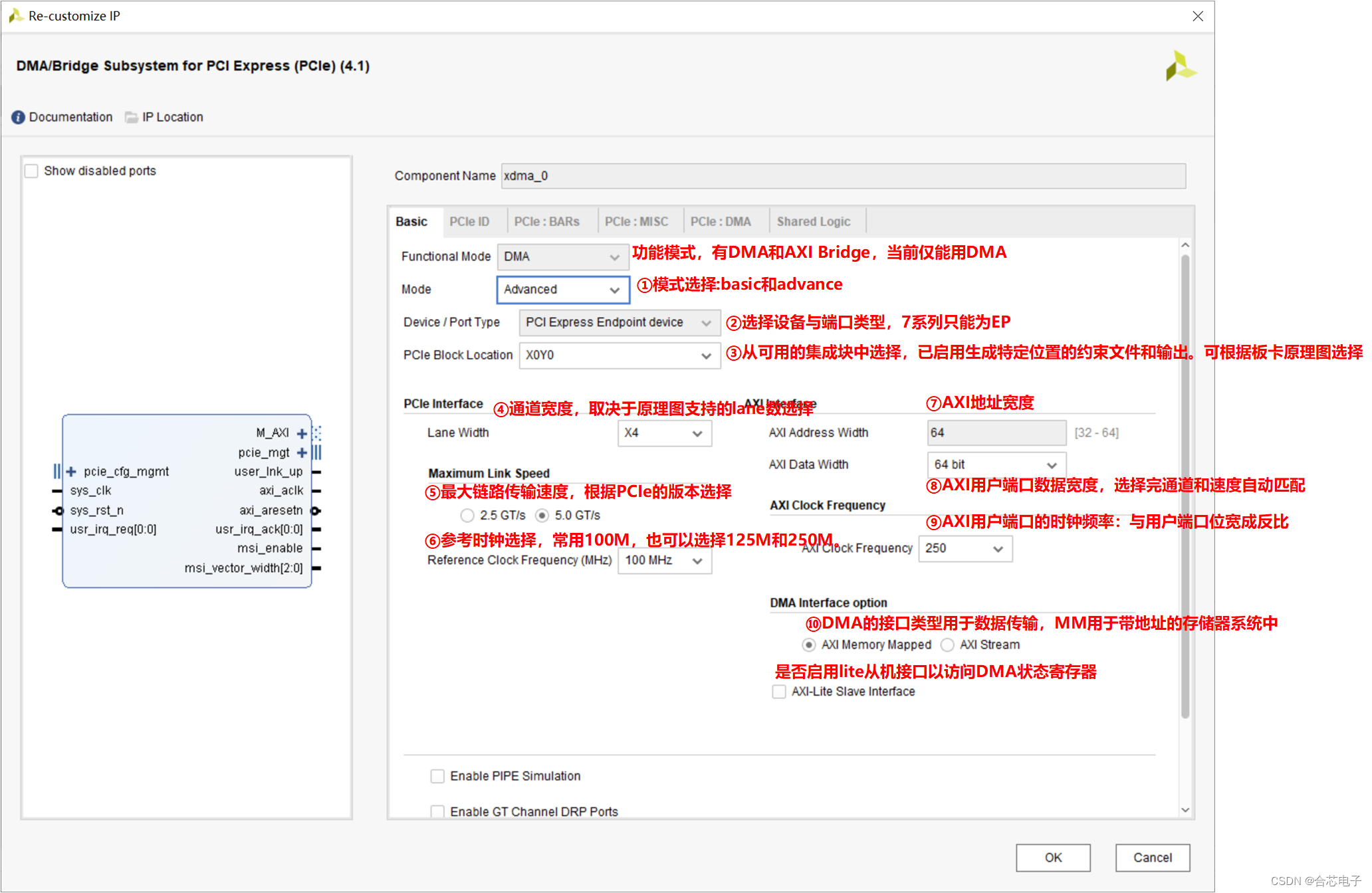

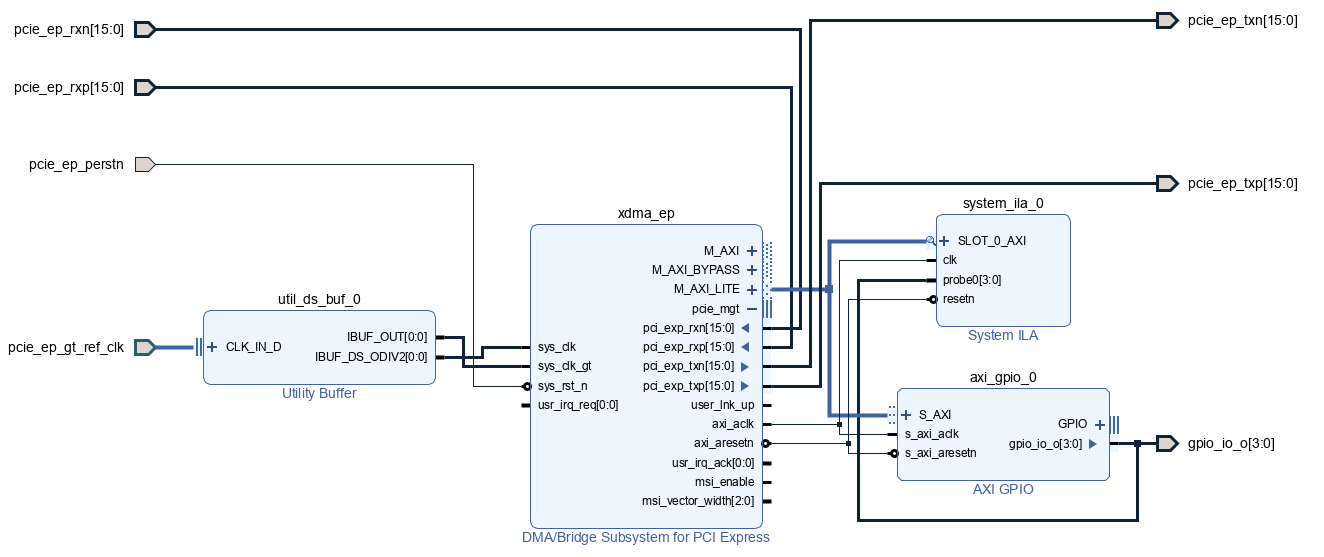

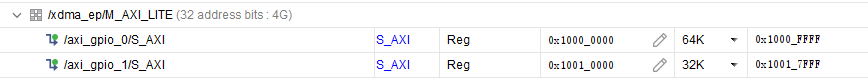

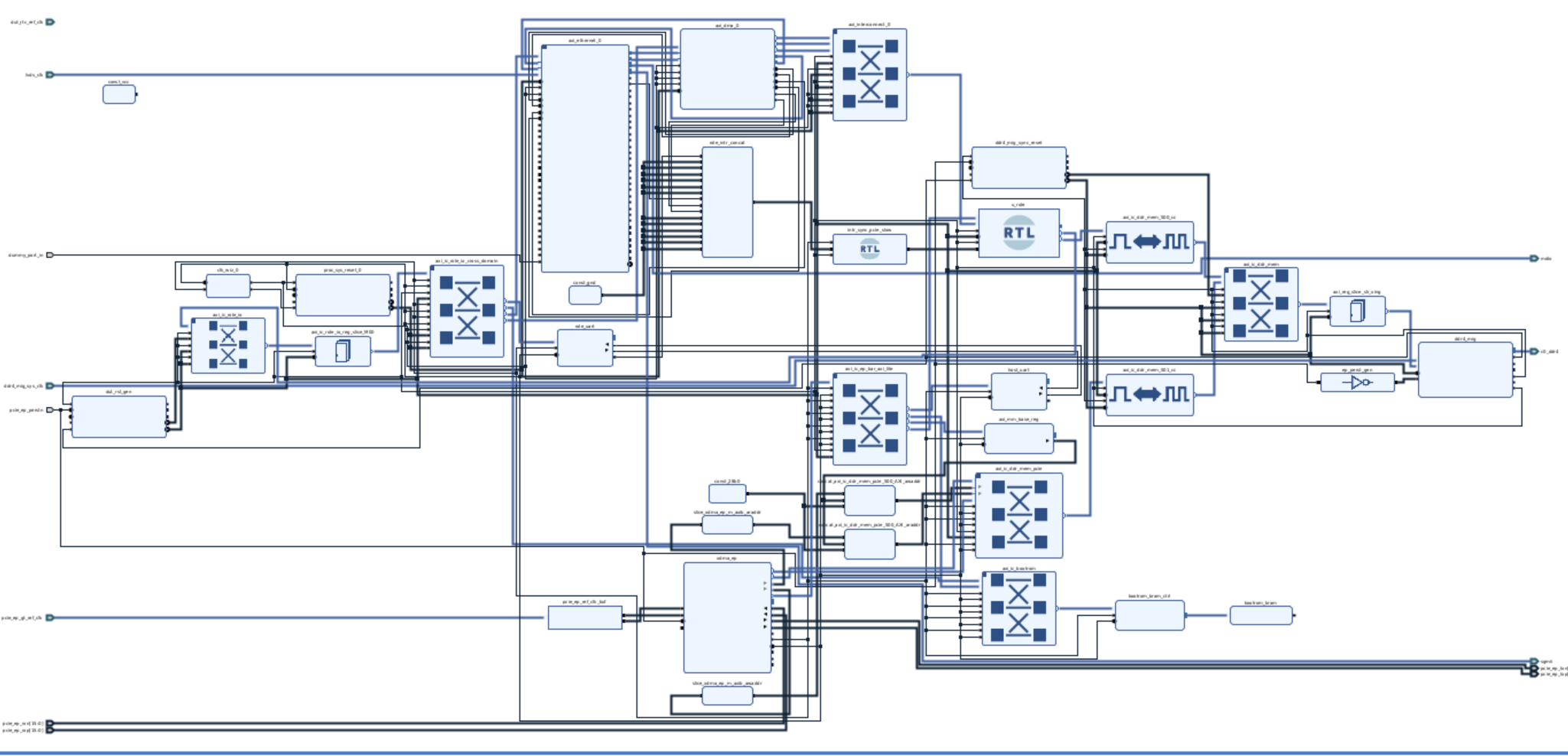

在xczu19eg-ffvc1760-2-e芯片上实现图示模块功能,利用xdma_ep模块实现pcie标准总线信号到axi总线协议信号转变,通过axi_gpio_0 IP核 控制4个LED灯。

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。

IBUFDS

是 Input Buffer for Differential Signaling 的缩写,中文可以翻译为“差分信号输入缓冲器”。它是一种在 FPGA(现场可编程门阵列)设计中广泛使用的缓冲器,主要用于将外部的差分信号转换为 FPGA 内部的单端信号。

xdma

# Create instance: xdma_ep, and set properties

set xdma_ep [ create_bd_cell -type ip -vlnv xilinx.com:ip:xdma:4.1 xdma_ep ]

set_property -dict [ list \

CONFIG.axilite_master_en {true} \

CONFIG.axilite_master_scale {Megabytes} \

CONFIG.axilite_master_size {32} \

CONFIG.axist_bypass_en {true} \

CONFIG.axist_bypass_scale {Megabytes} \

CONFIG.axist_bypass_size {256} \

CONFIG.cfg_mgmt_if {false} \

CONFIG.en_gt_selection {true} \

CONFIG.functional_mode {DMA} \

CONFIG.mode_selection {Advanced} \

CONFIG.pcie_blk_locn {X1Y0} \

CONFIG.pciebar2axibar_axil_master {0x10000000} \

CONFIG.pf0_base_class_menu {Processing_accelerators} \

CONFIG.pf0_sub_class_interface_menu {Unknown} \

CONFIG.pl_link_cap_max_link_speed {8.0_GT/s} \

CONFIG.pl_link_cap_max_link_width {X16} \

CONFIG.select_quad {GTH_Quad_227} \

CONFIG.xdma_axi_intf_mm {AXI_Memory_Mapped} \

] $xdma_ep7.21 服务器运行

时间:8小时

主要内容:

在服务器上运行设计好的模块,正确控制LED灯。

流程:

-

连接内网

-

检测目标设备是否开机并联网

ping 10.128.157.241

# ping 10.128.157.241是一个网络诊断命令,用于测试你的计算机是否能与目标 IP 地址 10.128.157.241通信。-

连接服务器

session -> ssh -> ip -> username -> rsa

-

打开vivado

/opt/Xilinx_2020.2/Vivado/2020.2/bin/vivado -nolog -nojour-

烧录

open hard ware manager -> open target -> program device -> add bit stream

-

终端运行

重

sudu reboot

(此时bit stream)已经加载到板卡上了 加载驱动(注意该步骤需要在xdma目录下进行) cd tab 可以到下一目录 cd 可以回到home目录 make 编译命令

sudo insmod xdma.ko【 sudo insmod xdma.ko这条命令的作用是 ••在Linux系统中动态加载一个内核模块(Kernel Module)••,具体来说: ••sudo••:以管理员权限执行(因为加载内核模块需要root权限)。 ••insmod••:Linux命令,用于••插入(Install)内核模块••(Insert Module)。 ••xdma.ko••:要加载的••内核模块文件••(.ko是Kernel Object的缩写),通常与Xilinx的••XDMA(PCIe DMA)驱动••相关。 】

该步骤如果bit流错误导致卡死的话,需要重启设备

读

sudo ~/proto/pcie-util /dev/xdma0_user read 0x000000007.22 ILA

时间:8小时

主要内容:

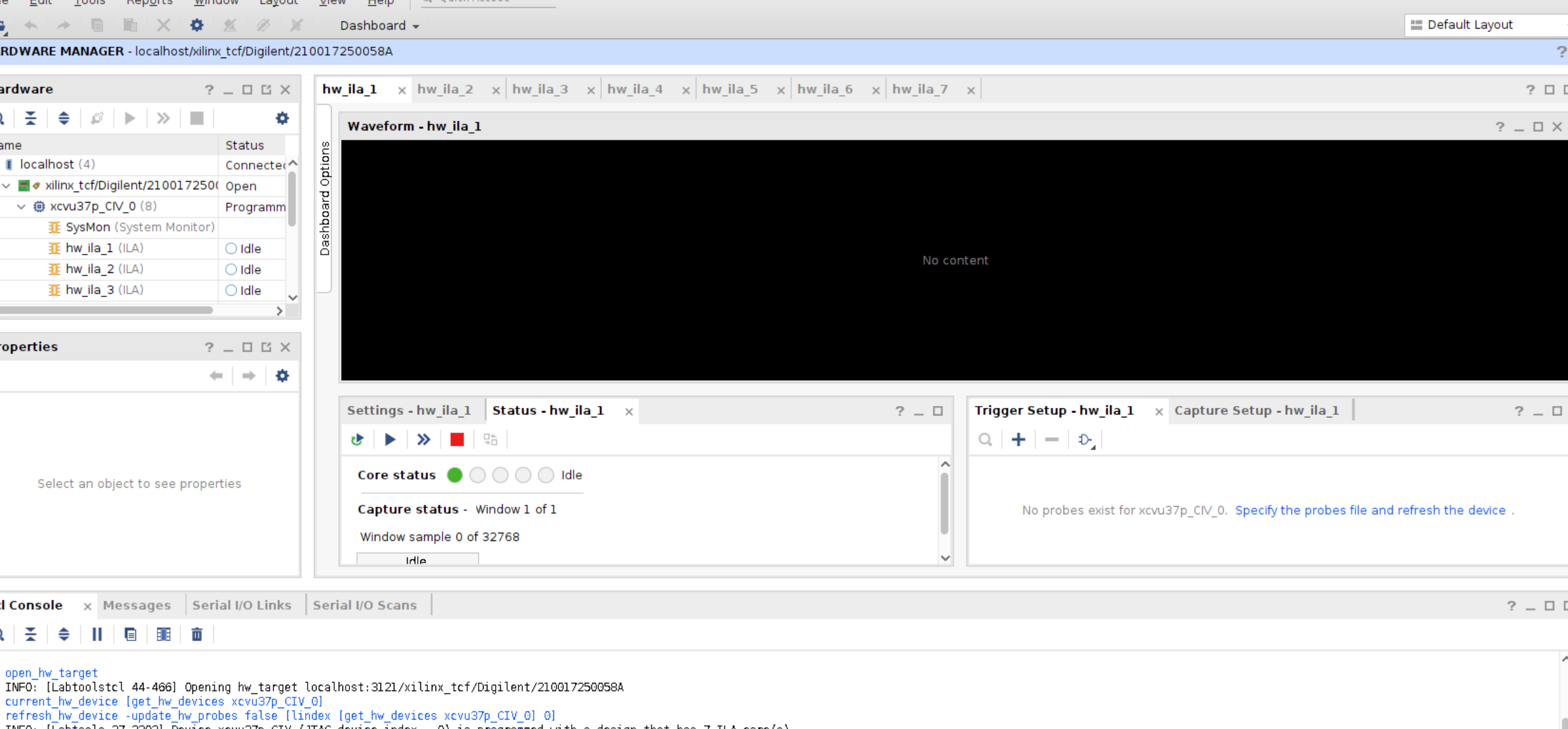

实现图示block design的模块,利用ILA抓取M_AXI_LITE以及GPIO数据,进行调试。

ILA工具使用(在BD添加IP版本)

在BD设计中添加ILA 对应IP,抓取相应的数据

在后续过程中会生成对应的.ltx文件

生成bitstream后进入Open Hardware Manager 进行烧录后重启

再一次进入Open Hardware Manager

点击specify the probes file and refresh the device添加.ltx文件

点击 + 添加trigger并设置触发条件

7.23 分频GPIO设计

时间:8小时

主要内容:

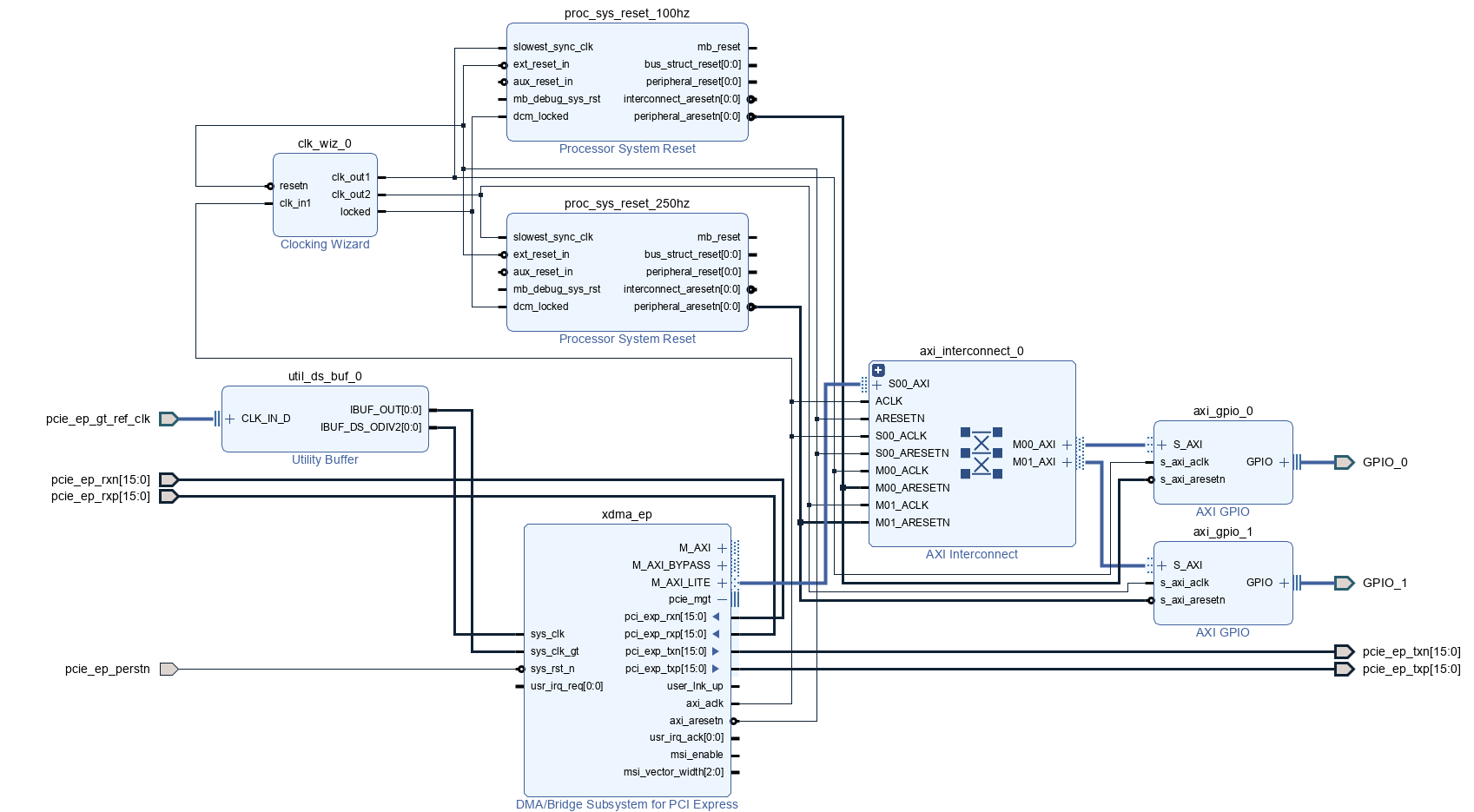

扩展GPIO,实现不同频率的GPIO控制(100MHz,250MHz);进行引脚约束。

初步想法:添加clock wizard IP核,得到100MHz和250MHz的时钟信号;

添加axi interconnect IP核,将xdma的M_AXI_LITE信号分为两个不同频率的信号。

axi interconect手册:

https://gitcode.com/Open-source-documentation-tutorial/eddcb/blob/main/pg059-axi-interconnect.pdf

引脚约束:

set_property PACKAGE_PIN E16 [get_ports {GPIO_0_tri_io[3]}]

set_property PACKAGE_PIN D16 [get_ports {GPIO_0_tri_io[2]}]

set_property PACKAGE_PIN C16 [get_ports {GPIO_0_tri_io[1]}]

set_property PACKAGE_PIN B16 [get_ports {GPIO_0_tri_io[0]}]

set_property PACKAGE_PIN N10 [get_ports pcie_ep_perstn]

set_property PACKAGE_PIN AF11 [get_ports {pcie_ep_gt_ref_clk_clk_n[0]}]

set_property PACKAGE_PIN AF12 [get_ports {pcie_ep_gt_ref_clk_clk_p[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports pcie_ep_perstn]

set_property IOSTANDARD LVCMOS18 [get_ports {GPIO_0_tri_io[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {GPIO_0_tri_io[2]}]

set_pjroperty IOSTANDARD LVCMOS18 [get_ports {GPIO_0_tri_io[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {GPIO_0_tri_io[0]}]7.24 分频GPIO完善

时间:8小时

主要内容:

添加Processor System Reset保证时序一致,

板卡号:xczu19eg-ffvc1760-2-e (active)

后续问题:在服务器上运行过程中发现read全为ffffffff,且不能读。

7.25 运行调试

时间:8小时

主要内容:

进一步运行调试

三态gpio:

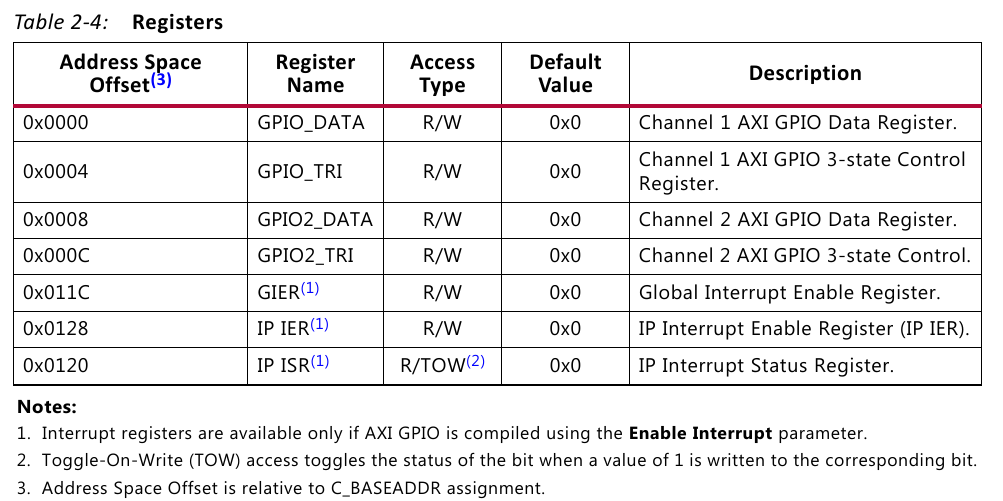

AXI GPIO v2.0 LogiCORE IP Product Guide (PG144)

从手册中可以得出,在读写之前,需要将基地址偏移量为0x0004的寄存器设置为0。

7.28 ILA调试

时间:8小时

主要内容:

在分频gpio基础上添加ILA IP核抓取S_AXI信号进行调试。

通过ILA IP核抓取M_AXI_LITE信号对比发现,低地址读取触发正常,高地址读取时虽然服务器读取值任为全f,但不能正常触发。

xdma IP核中PCIe to AXI Translation为0x1000_0000。

初步推断是基地址设定的问题,修改完善Address Map,烧录bit运行。

最终运行成功。

7.29 前期总结

时间:8小时

主要内容:

总结前期实验流程及内容,撰写实验报告

7.30 vcu128相关

时间:8小时

主要内容:

了解 基于Xilinx VCU128板卡的SERVE.h平台设计,明确大致任务方向;

通过vcu128的设计,掌握Ethernet System IP、DMA IP的原理及使用方法。

基于vu19p着手设计。

基于Xilinx VCU128板卡的SERVE.h平台设计

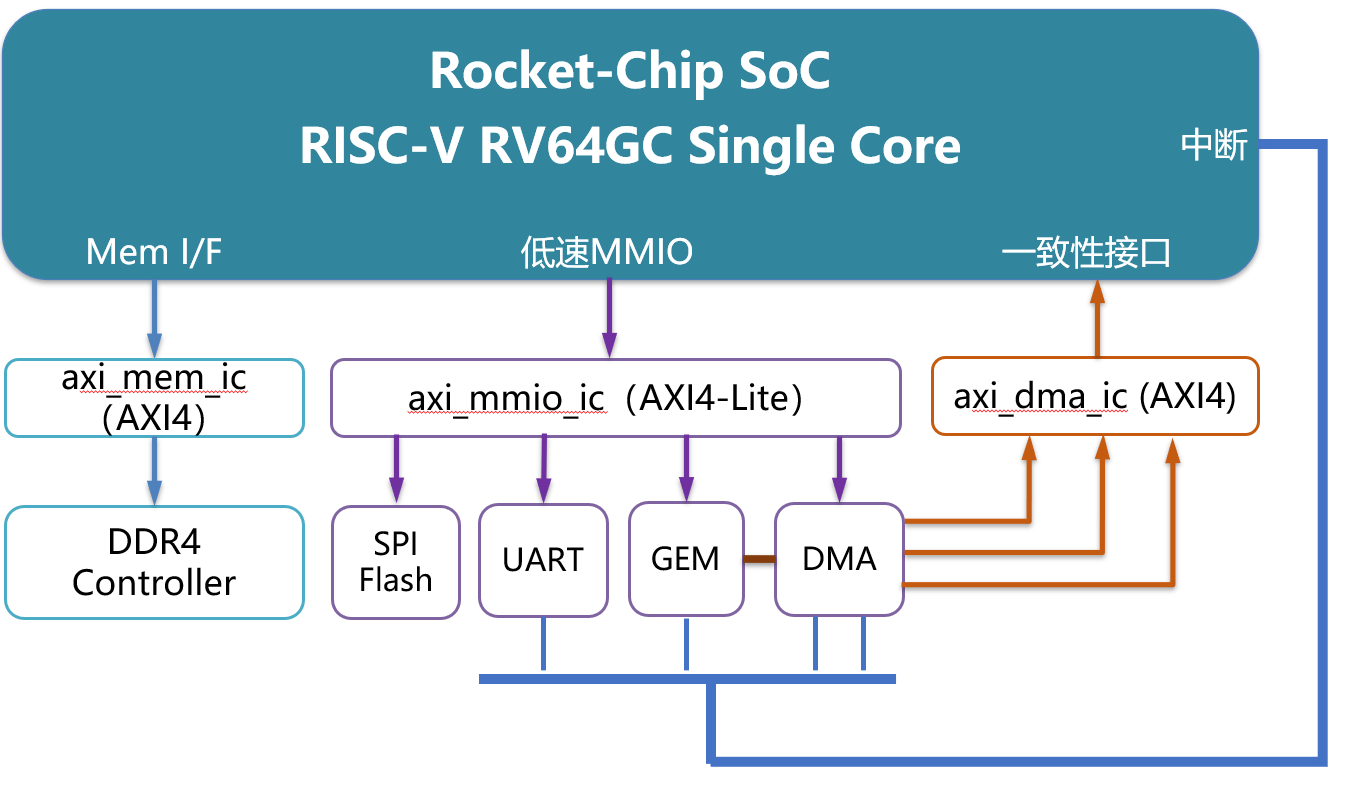

本次任务便是围绕MMIO-AXI4-Lite-GEM展开

AXI HWICAP

AXI High-Speed Internal Configuration Access Port。它是Xilinx FPGA芯片中的一种IP核,主要用于将ICAP原语进行封装,并提供AXI接口,以便集成到基于MicroBlaze等软核处理器的SoC系统中。通过AXI HWICAP,用户可以通过软件层调用的方式访问FPGA底层的配置单元,实现对硬件的动态配置。这种设计简化了硬件配置流程,使开发者能够更灵活地管理和操作FPGA资源。

SPI Flash

“Serial Peripheral Interface Flash”,即“串行外设接口闪存”。它是一种基于SPI协议的非易失性存储器芯片,广泛应用于嵌入式系统和便携式设备中

GEM

Gigabit Ethernet Media-independent Interface (GEM),这是一种用于以太网通信的硬件接口标准。GEM接口主要用于实现物理层(PHY)与数据链路层之间的数据传输,支持千兆以太网(Gigabit Ethernet)的速率

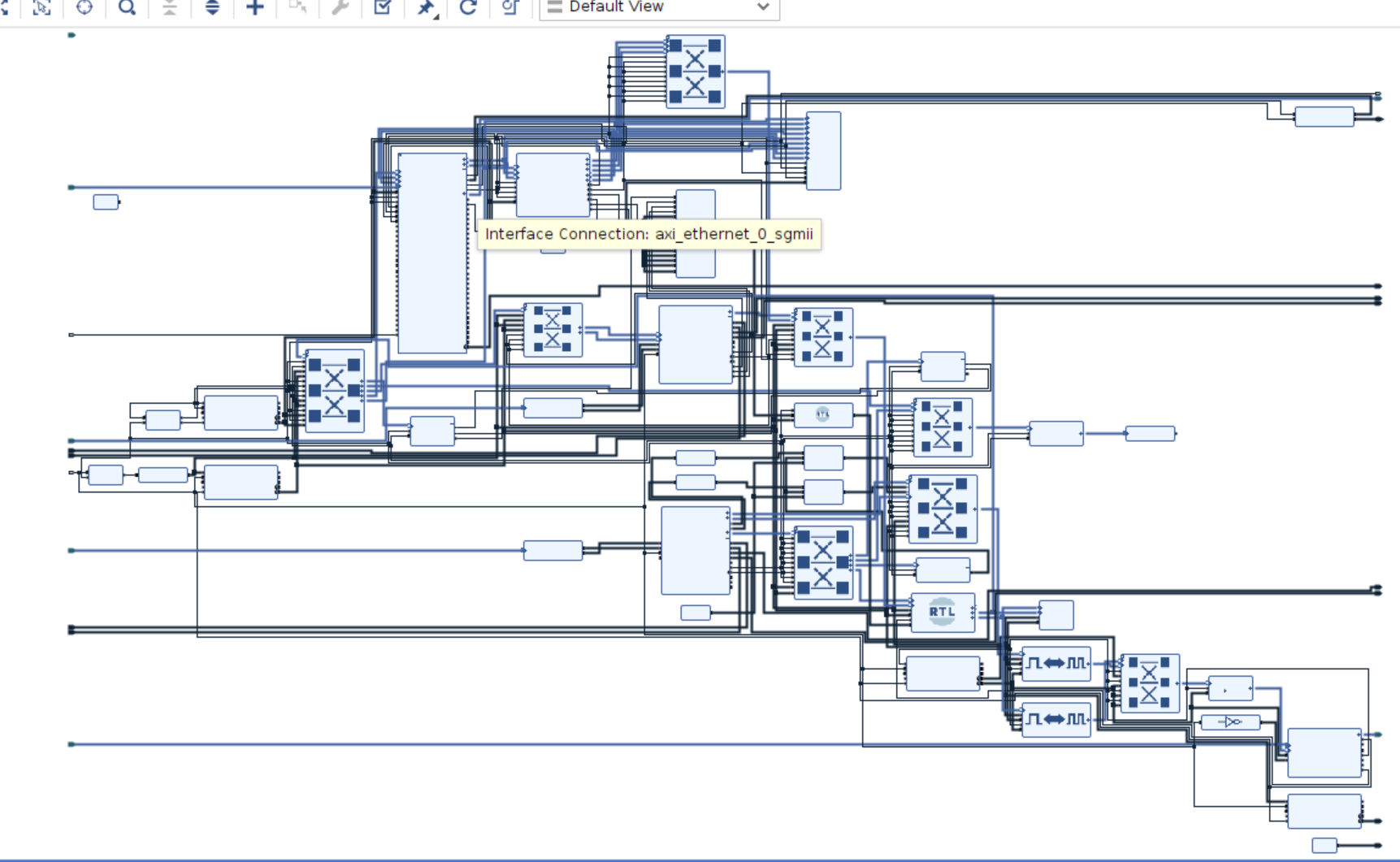

vu19p BD:

后续问题:

实现步骤出错。

7.31 vu19p

时间:8小时

主要内容:

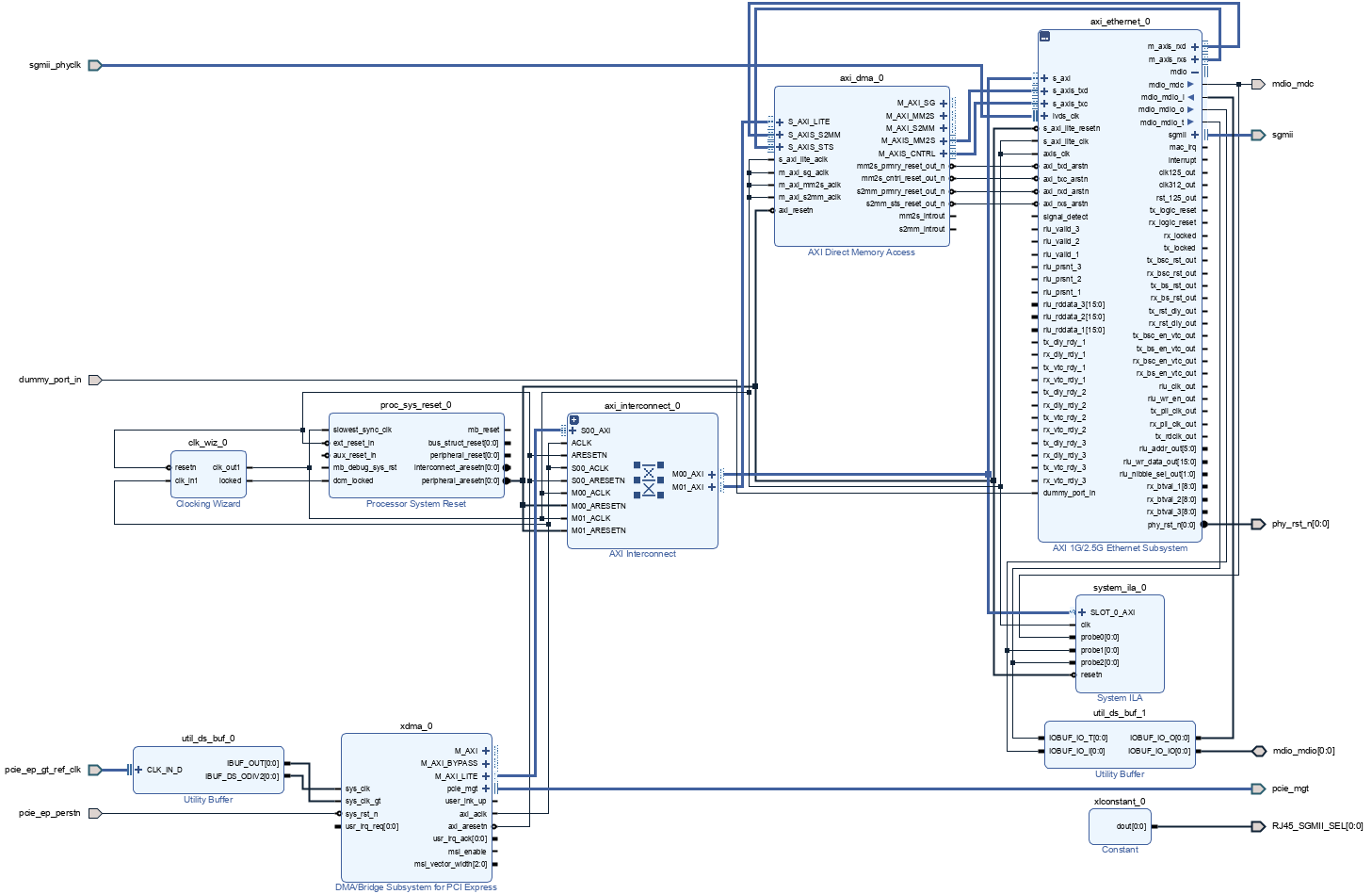

修改block design;依据电路原理图进行引脚约束;通过AXI 1G/2.5G Ethernet Subsystem和AXI Direct Memory Access的手册了解相应IP核的原理;

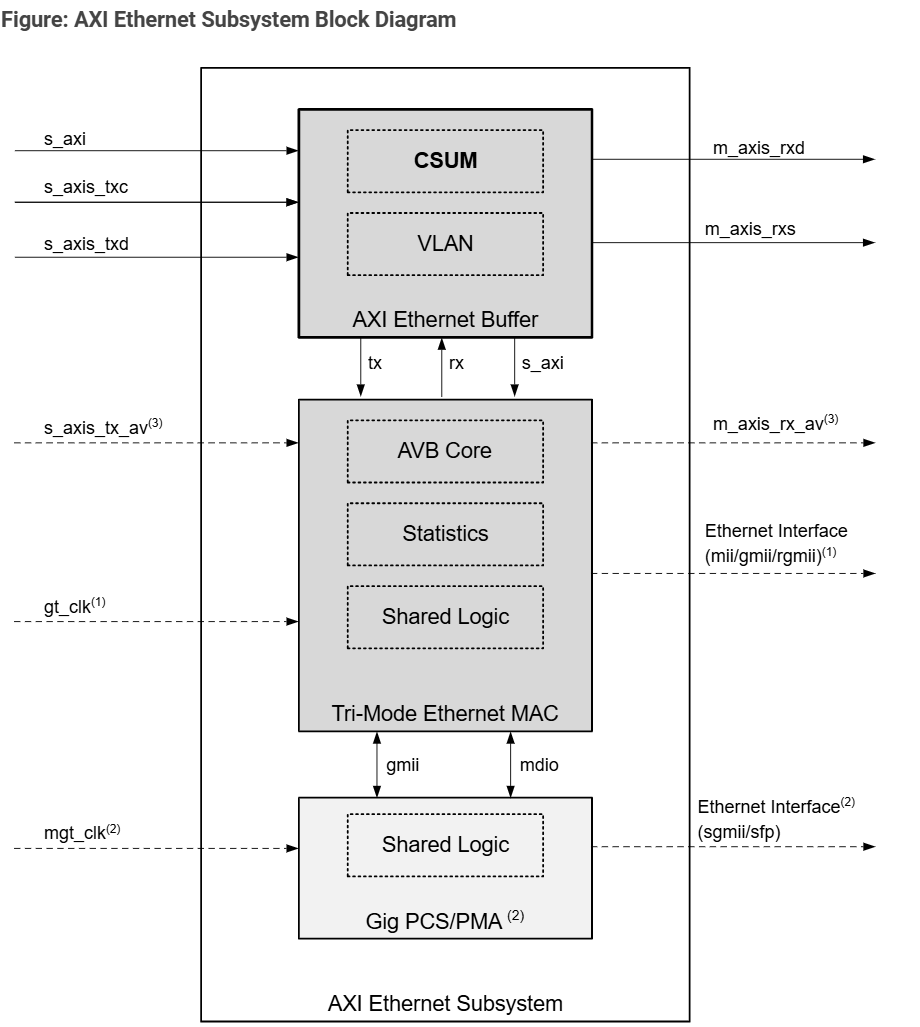

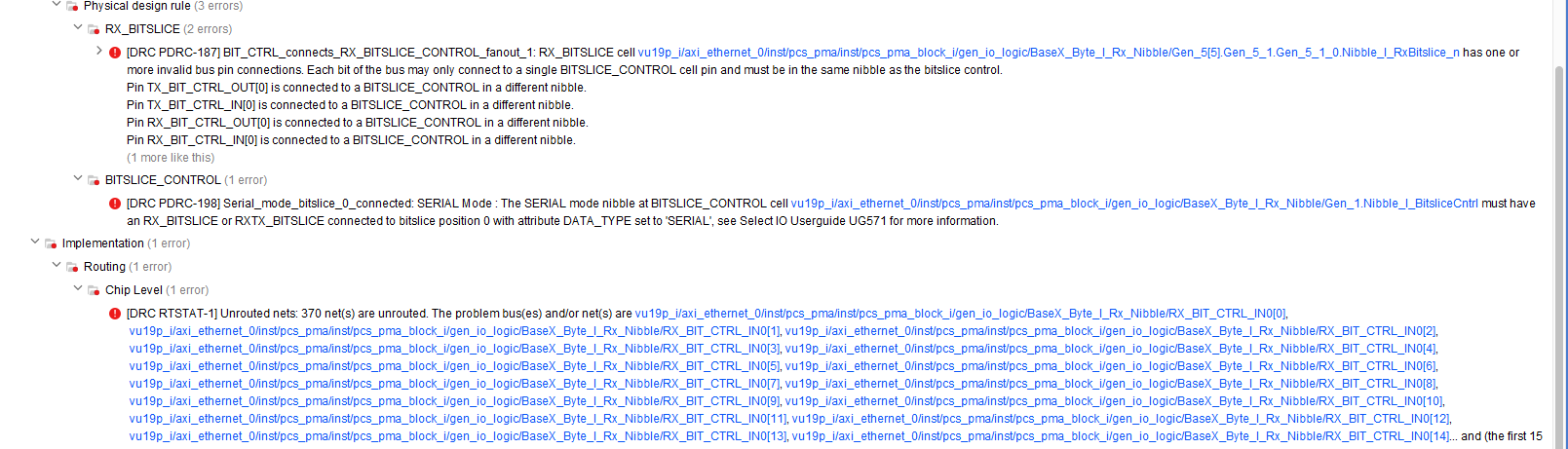

根据报错内容可知Ethernet location部分出了问题,回想电路原理图中并没有包括dummy_port_in,故我们在Re-customize IP的Location栏目里勾选RX nibble BITSLISE_0 is used.

删除dummy_port_in信号。

axi 1g/2.5g ethernet subsystem 手册:

Functional Description • AXI 1G/2.5G Ethernet Subsystem Product Guide (PG138) • 阅读器 • AMD 技术信息门户网站

注:IP核手册可以直接从vivado IP核进入相应手册网址。

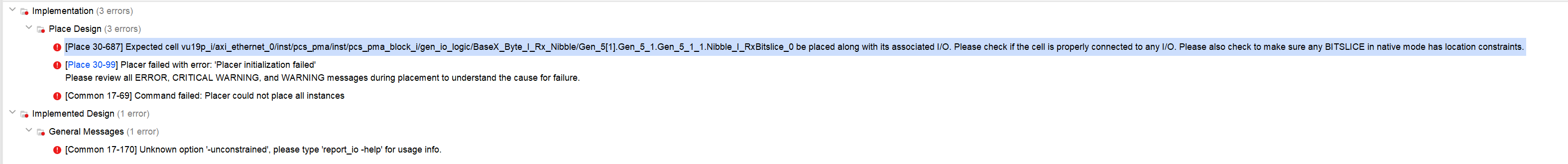

axi 1g/2.5g ethernet subsystem high level block diagram:

后续问题:

最后生成bitstream步骤出现IP核不支持。

8.1 Ethernet System IP 相关

时间:8小时

主要内容:

AXI 1G/2.5G Ethernet Subsystem IP核 license的申请及应用,修改调试程序。

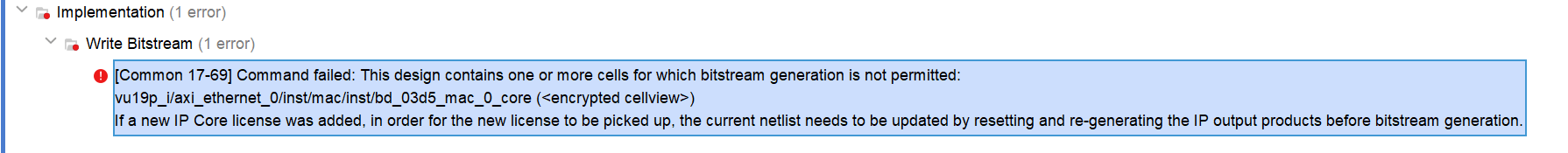

报错说明存在IP核不允许生成bitstream。

进入AXI 1G/2.5G Ethernet Subsystem IP核re-customize界面,确实发现最下角为design linking license字样。

补充 IP license的类型说明:

design_linking:允许客户进行包括时许仿真的各种仿真,但是不能生成bit文件

hardware_evaluation license:这就是申请的license,允许生成bit文件,但有时间限制,一定时间后不能使用。

key for product use:购买生成的license,全部功能都可以使用。

具体申请方法参看我的另一篇博客

Xilinx收费IP核hardware_evaluation license申请-CSDN博客

后续问题:发现勾选了RX nibble BITSLISE_0 is used之后会随之引入一个新的问题,可能之前一个错误解决方法错误,或者该问题可以通过不改变现有Ethernet IP实现。

8.4 调试

时间:8小时

主要内容:调试

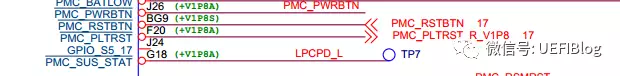

存在block location错误,由此查看xdma的电路原理图,发现GT quad应该为226.

Xilinx UltraScale/UltraScale+ FPGA 中,GT Quad(Gigabit Transceiver Quad) 是指 由4个高速串行收发器(GTY/GTM/GTH/GTZ)及其共享资源组成的物理单元

FPGA(如 Xilinx UltraScale/UltraScale+、Intel Stratix 等) 中,Bank 是芯片上按物理和电气特性划分的独立 I/O 资源区域,用于管理引脚配置、电压标准、时钟分配等关键功能。

bank以物理隔离和电器划分为核心概念

Pin and Bank Rules (PG150)

• Pins in a byte lane are numbered N0 to N12.

• Byte lanes in a bank are designed by T0, T1, T2, or T3. Nibbles within a byte lane are distinguished by a “U” or “L” designator added to the byte lane designator (T0, T1, T2, or T3). Thus they are T0L, T0U, T1L, T1U, T2L, T2U, T3L, and T3U.

Designs using x8 or x16 components – dqs must be located on a dedicated byte clock pair in the upper nibble designated with “U” (N6 and N7).dq associated with a dqs must be in same byte lane on any of the other pins except pins N1 and N12. b. Designs using x4 components – dqs must be located on a dedicated byte clock pair in the nibble (N0 and N1 in the lower nibble, N6 and N7 in the upper nibble). dq associated with a dqs must be in same nibble on any of the other pins except pin N12 (upper nibble). The lower nibble dq and upper nibble dq must be allocated in the same byte lane.

取消勾选RX nibble bitslice_0 is used,恢复dummy_port_in---

8.5 调试

时间:8小时

主要内容:进一步调试

8.6 工程仓库相关

时间:8小时

主要内容:

相关知识tcl、bash、vim学习;熟悉工程仓库

.tar(全称 Tape Archive,磁带归档)是 Unix/Linux 系统 中常见的归档文件格式,用于将多个文件或目录打包成单个文件(不压缩,仅合并)

知识整理链接:

8.7 工程仓库相关

时间:8小时

主要内容:

生成shell和role工程,熟悉工程文件。

1. Shell 层工程生成

make PRJ="shell:mimic_turbo" FPGA_BD=mimic_turbo FPGA_ACT=prj_gen vivado_prj

-

创建FPGA外围基础设施的Vivado工程框架

-

初始化板级支持包(BSP)和硬件约束

| 参数 | 值 | 作用 |

|---|---|---|

PRJ | shell:mimic_turbo | 标识为Shell层工程,目标平台mimic_turbo |

FPGA_BD | mimic_turbo | 加载开发板定义文件 |

FPGA_ACT | prj_gen | 工程生成模式 |

输入

-

work_farm/shell/rtl/:Shell层RTL代码 -

work_farm/fpga/boards/mimic_turbo/:板级约束(XDC)和IP配置

输出

work_farm/fpga/vivado_prj/shell_mimic_turbo_mimic_turbo/ ├── shell_mimic_turbo.xpr # Vivado工程文件 ├── constrs_1/ # 约束文件目录 │ └── mimic_turbo.xdc # 板级物理约束 └── ip/ # 预生成IP核

日志文件

-

work_farm/fpga/vivado_out/shell_mimic_turbo/prj_gen.log

2. Shell层综合

make PRJ="shell:mimic_turbo" FPGA_BD=mimic_turbo FPGA_ACT=run_syn vivado_prj

-

将Shell层RTL转换为门级网表

-

执行逻辑优化和初步时序分析

-

FPGA_ACT=run_syn:触发综合流程

输出

work_farm/fpga/vivado_out/shell_mimic_turbo_mimic_turbo/synth_1/ ├── synth.dcp # 设计检查点文件 ├── timing_summary.rpt # 时序报告 ├── utilization.rpt # 资源利用率报告 └── synth.log # 详细综合日志

3. Role层工程生成

make PRJ="target:nanhu-g:proto" FPGA_BD=mimic_turbo FPGA_ACT=prj_gen vivado_prj

-

创建香山处理器核的独立工程

-

集成Shell层生成的接口约束

-

自动继承Shell层的时钟和总线定义

-

加载处理器核专用约束:

-

nanhu-g/constraints/timing.xdc -

nanhu-g/constraints/power.xdc

-

输出

text

work_farm/fpga/vivado_prj/target_nanhu-g_proto_mimic_turbo/ ├── target_nanhu-g.xpr ├── constrs_1/ │ ├── mimic_turbo_derived.xdc # 从Shell衍生的约束 │ └── nanhu_specific.xdc # 处理器专用约束 └── srcs_1/ # 香山RTL代码

4. Role层综合

make PRJ="target:nanhu-g:proto" FPGA_BD=mimic_turbo FPGA_ACT=run_syn vivado_prj

输出

work_farm/fpga/vivado_out/target_nanhu-g_proto_mimic_turbo/synth_1/ ├── nanhu_g.dcp # 处理器核网表 ├── merged.dcp # 与Shell的合并网表 ├── clock_util.rpt # 时钟网络分析 └── power_estimate.rpt # 功耗预估

5. 生成比特流

make PRJ="target:nanhu-g:proto" FPGA_BD=mimic_turbo FPGA_ACT=bit_gen vivado_prj

输出

nanhu-g/ready_for_download/proto_mimic_turbo/

├── system.bit # 主比特流文件

├── system.ltx # 调试探针文件

└── reports/

├── route_status.rpt # 布线成功率

└── io_placement.rpt # 引脚分配报告

后续问题:license

8.8 shell

时间:8小时

主要内容:

了解shell部分IP核功能作用,梳理数据流向及各组件作用。

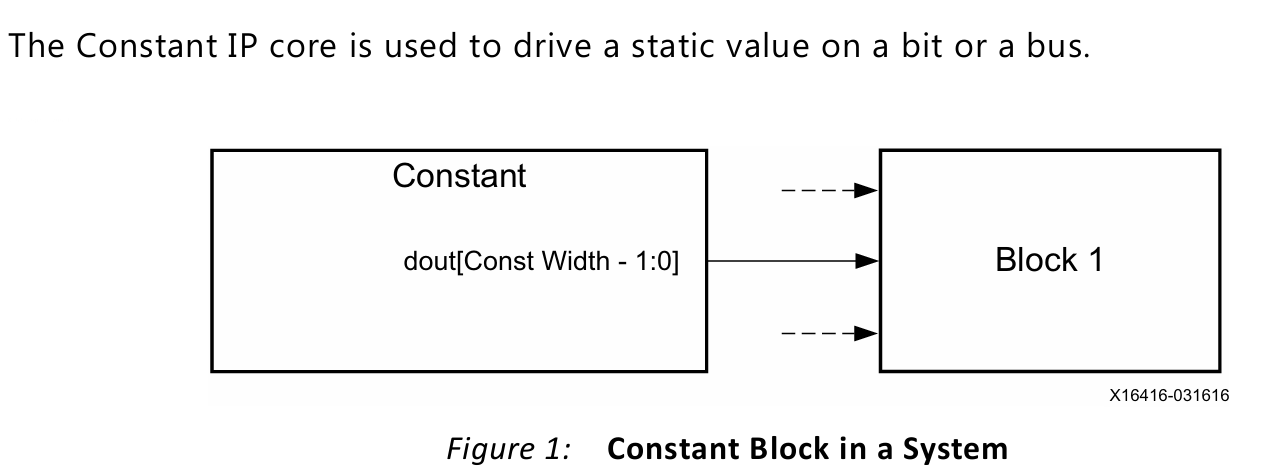

constand IP core

constand IP core 驱动信号或者总线到一个设定值

具有可参数化线宽、以十进制传递参数等优点

PB040 Constant v1.1 Product Brief (PB040) • 查看器 • AMD 技术信息门户网站

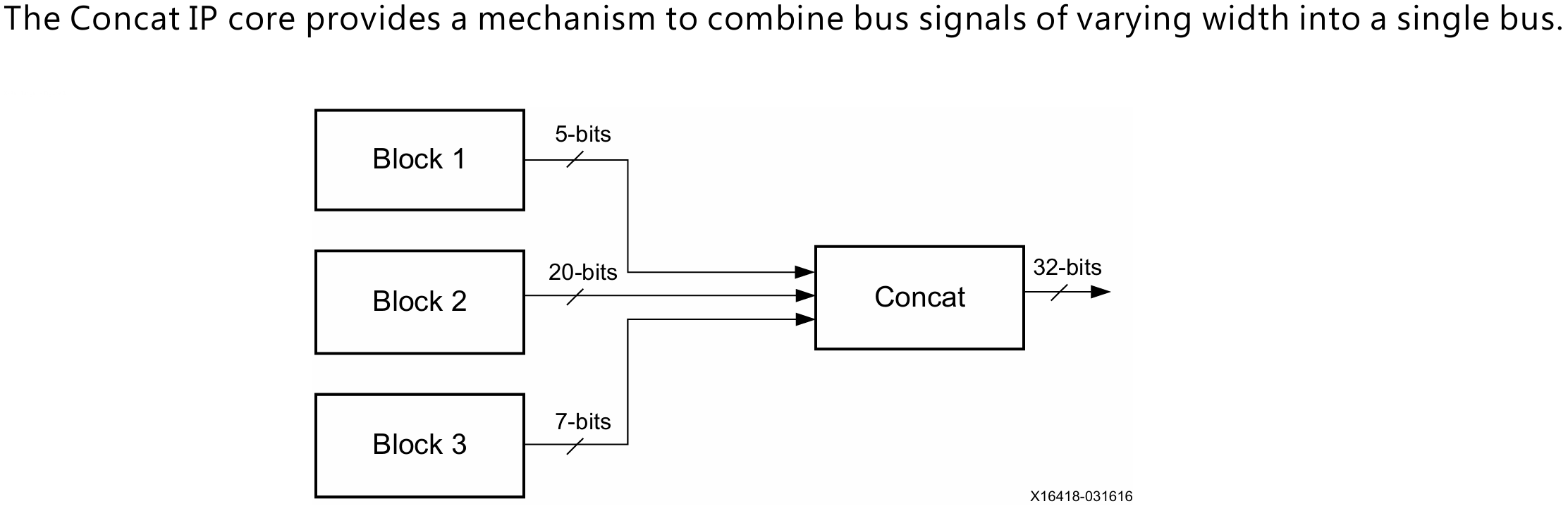

concat IP core

concat IP 核用于连接不同宽度的总线信号

PB041:

Concat v2.1 Product Brief (PB041) • 查看器 • AMD 技术信息门户网站

DMA/Bridge for PCIE Subsystem core

PCIe BARs Tab • DMA/Bridge Subsystem for PCI Express Product Guide (PG195) • 阅读器 • AMD 技术信息门户网站

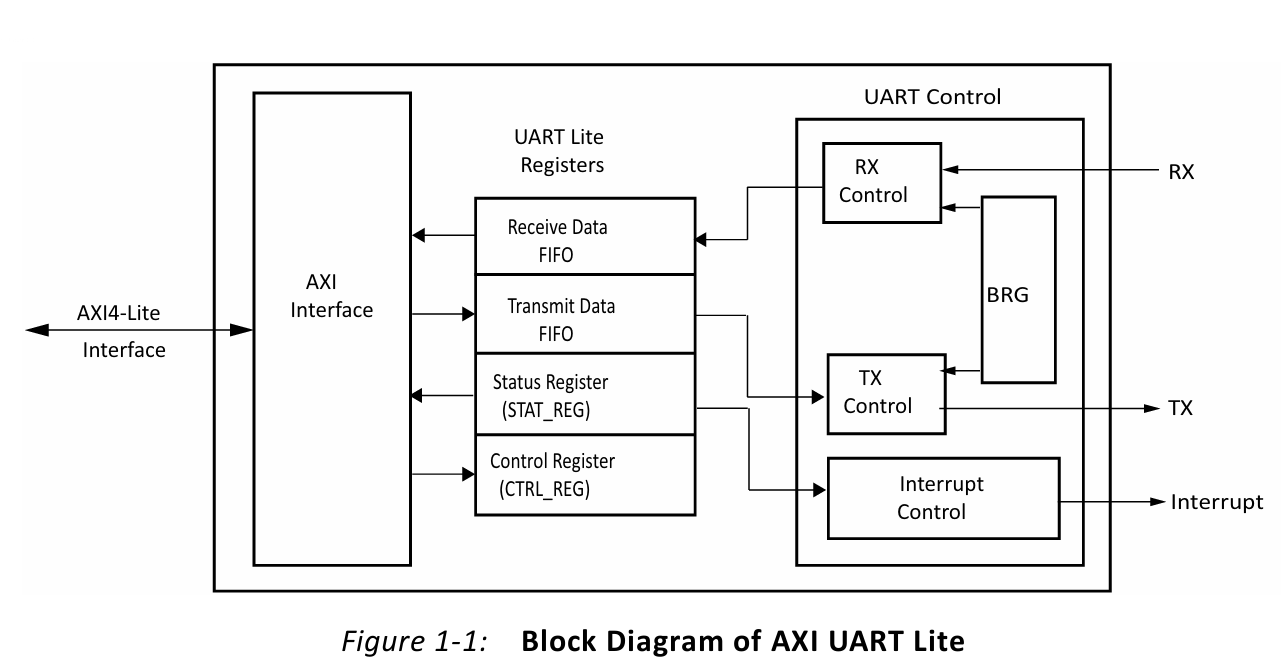

AXI Uartlite

LogiCORE™ IP AXI Universal Asynchronous Receiver Transmitter (UART) Lite 核心 在 UART 信号与高级微控制器总线架构(AMBA®)AXI 接口之间提供桥接,并支持异步串行数据传输的控制器接口。

AXI UART Lite v2.0 Product Guide (PG142) • 查看器 • AMD 技术信息门户网站

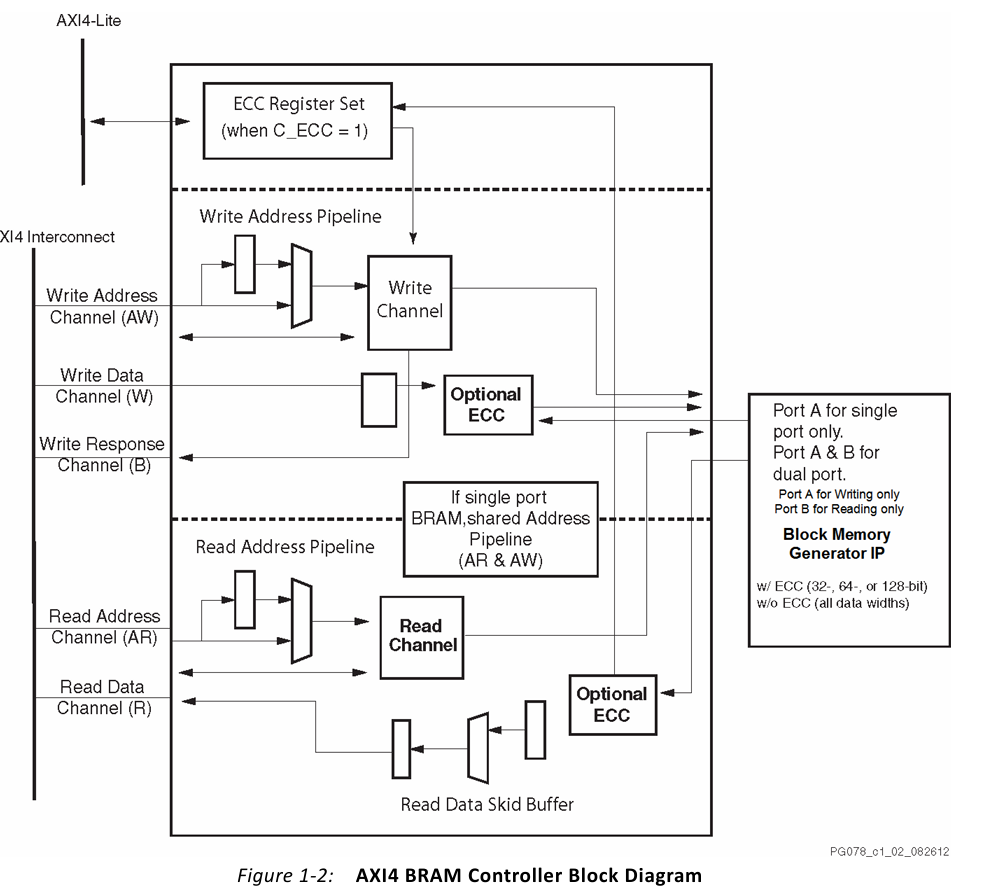

AXI BRAM controller

AXI BRAM 内核被设计为 AXI 端点从站 IP,用于与 AXI 互连和系统主设备集成,以与本地 BRAM 进行通信。该内核支持对 BRAM 的单次和突发事务,并针对性能进行了优化。

block memory generator

块内存生成器IP 核可自动为 AMD FPGA 创建资源和功耗优化的块内存。使用户能够创建块内存功能以满足各种要求。

AXI GPIO

AXI GPIO 为 AXI(高级可扩展接口)接口提供通用输入/输出接口。该 32 位软 IP 核设计用于与 AXI4-Lite 接口连接。

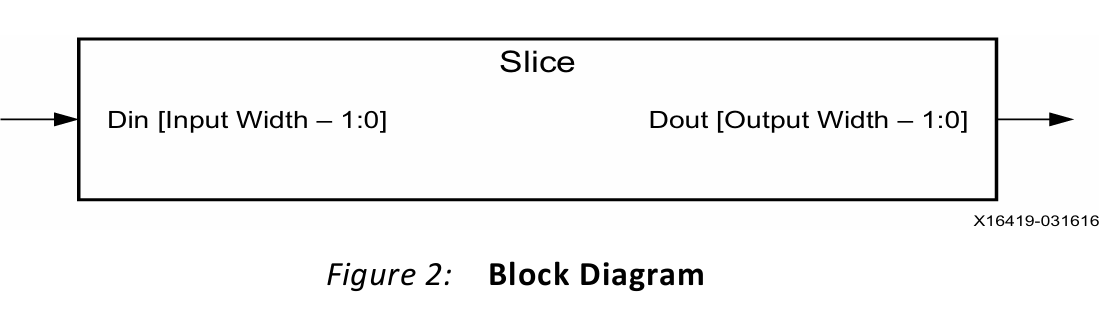

SLICE

Slice IP 核用于从总线网络上撕下位。

AXI Register Slice

AXI 寄存器切片可用于 AXI 端点、交叉条和互连之间的选定路径,以中断关键定时路径并实现更高的时钟频率。

AXI clock converter

AXI Clock Converter 为 AXI4 和 AXI4-Lite 协议设计,用于在不同时钟域之间桥接 AXI 事务,支持同步和异步时钟域的转换。它通过内部 FIFO 或轻量级寄存器同步机制,确保跨时钟域的数据传输完整性和协议合规性.

DDR4 SDRAM

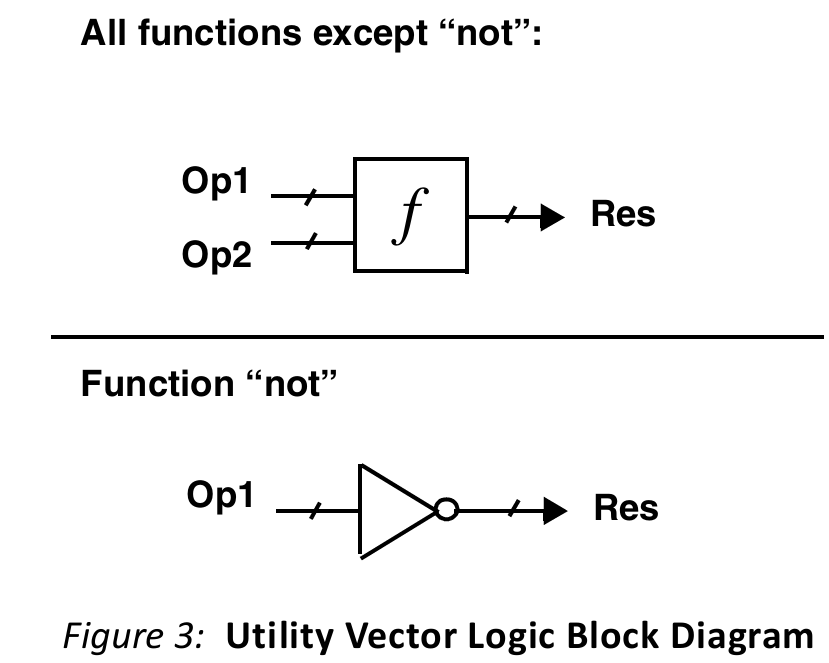

Utility Vector Logic

Utility Vector Logic Core(实用向量逻辑核心) 接收两个向量操作数,按位应用逻辑函数运算,生成单个向量结果。该核心设计用作外设间的"胶合逻辑"(连接逻辑)。

8.11 ethernet模块(vcu128)/ 服务器运行np19a

时间:8小时

主要内容:

服务器运行vcu128;

在vu19p上搭建ethernet工程

io standard

1. 单端电平标准

-

LVCMOS

-

电压:1.2V/1.5V/1.8V/2.5V/3.3V

-

特点:低功耗、通用型,用于低速至中速信号(如GPIO、配置引脚)。

-

示例:LVCMOS18(1.8V)、LVCMOS25(2.5V)。

-

-

LVTTL

-

电压:3.3V(兼容5V输入)

-

特点:传统TTL兼容,用于旧系统接口,功耗较高。

-

-

HSTL

-

电压:1.5V/1.8V

-

特点:高速内存接口(如QDR SRAM),需匹配终端电阻(VTT)。

-

子类:HSTL_I(无终端)、HSTL_II(更高速)。

-

-

SSTL

-

电压:1.8V/2.5V

-

特点:DDR内存接口标准(如SSTL18用于DDR3,SSTL15用于DDR4)。

-

子类:SSTL135(DDR4低电压版)。

-

2. 差分电平标准

-

LVDS

-

电压:350mV差分摆幅(共模1.25V)

-

特点:高速低功耗(可达数Gbps),用于SerDes、摄像头接口等。

-

衍生:

-

RSDS:低摆幅LVDS。

-

BLVDS:总线型LVDS。

-

-

-

TMDS

-

特点:HDMI/DVI视频传输,阻抗严格匹配(100Ω)。

-

-

差分HSTL/SSTL

-

示例:DIFF_HSTL_II(用于高速差分时钟)。

-

-

MIPI D-PHY

-

特点:移动设备接口(如摄像头、显示屏),需专用IP支持。

-

3. 电压参考标准

-

PCI/PCI-X

-

电压:3.3V

-

特点:支持热插拔,33/66MHz时钟。

-

-

GTL/GTL+

-

电压:低摆幅(GTL+约1V)

-

特点:背板总线,需外部上拉。

-

4. 高速收发器标准

-

GTX/GTH/GTY

-

协议支持:PCIe、SATA、10G以太网等。

-

电平:

-

CML:高速串行(如PCIe Gen3 8Gbps)。

-

LVDS:自定义协议(如JESD204B)。

-

-

后续问题:

1) 继续修改Ethernet 工程

2)将服务器运行vu19p的剩余没解决的192个port修改好

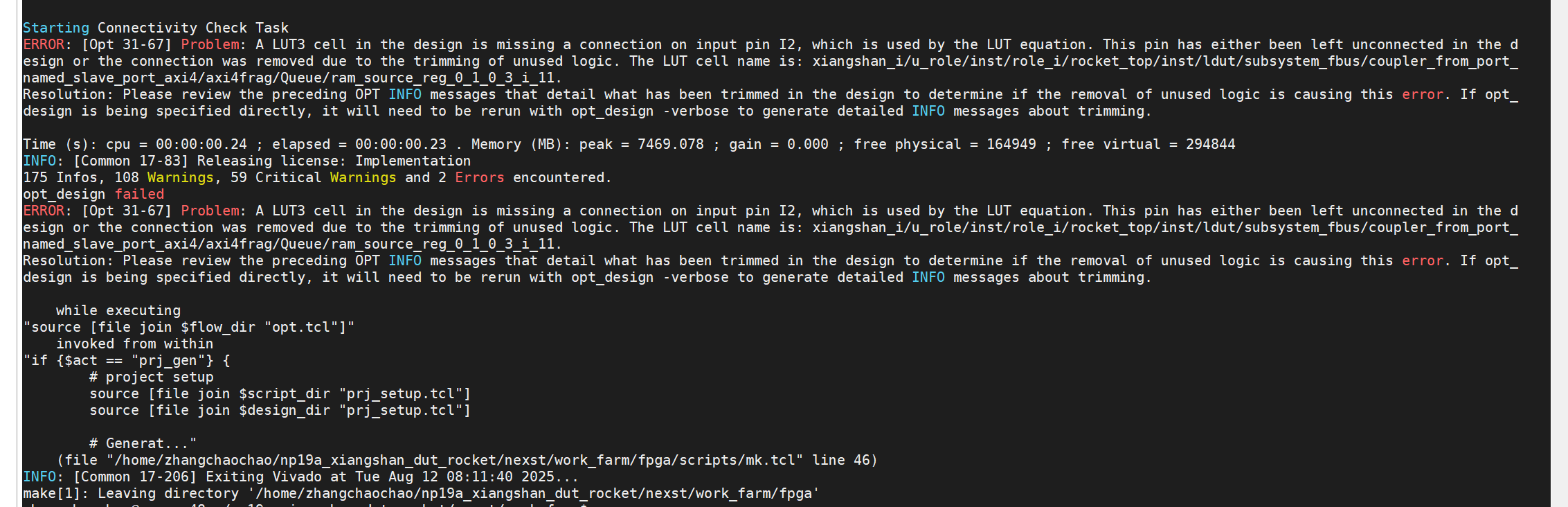

8.12 服务器下vu19p相关

时间:8小时

主要内容:

将vu19p报错中提到的port修改好,并继续调试

解压 .tar 文件可以使用以下命令:

tar -xvf filename.tarnohup 是 Linux/Unix 系统中的一个命令,用于在用户退出或关闭终端后,继续运行一个命令或程序。nohup 这个命令的全称是 "no hang up",意思是 "不挂断"。

nohup command &-

command是你要执行的命令或程序。 -

&是将进程放到后台执行。 -

nohup会自动将标准输出(stdout)和标准错误(stderr)重定向到文件nohup.out,如果没有指定输出文件的话。

示例:

-

运行一个脚本并在后台执行:

nohup ./my_script.sh & -

查看输出:

如果没有指定输出文件,nohup默认会将输出写入到nohup.out文件中:tail -f nohup.out -

将输出重定向到其他文件:

如果你想指定输出文件,可以这样写:nohup ./my_script.sh > output.log 2>&1 &-

> output.log将标准输出重定向到output.log文件。 -

2>&1将标准错误也重定向到同一个文件。

-

-

查看后台进程:

你可以使用ps命令查看后台进程:ps aux | grep my_script.sh -

杀掉后台进程:

使用kill命令来终止后台进程:kill <PID>其中

<PID>是进程的ID。

后续问题:

8.13 复现vcu128及服务器运行vu19p

时间:8小时

主要内容:成功复现vcu128相关

在Xilinx VU19P FPGA中,I/O bank通常被划分为多个Tri-state(T)组,例如 T0、T1、T2 和 T3,这一分区主要与I/O引脚的分配、数据流控制和接口标准有关。为了更详细地解释这一结构,我们需要深入了解几个关键概念:I/O Bank、Tri-state(T)、以及如何将这些划分映射到FPGA的实际硬件架构上。

-

每组T控制多个Lane:一个T组控制多个

lane,而每个lane又可以携带多个nibble。例如,PCIe协议中的数据传输通常是通过多个lane并行传输的。在一个Bank中,T组(如T0、T1、T2、T3)管理每个lane的数据传输,确保数据可以同时从多个通道传输,从而增加带宽。 -

多个nibble组成一个lane:每个

lane可以划分为两个nibble,每个nibble包含4位数据。这样,数据传输过程就被拆分成更小的部分,通过不同的lane并行工作来提高传输速率。例如,一个lane如果包含两个nibble(即8位),通过并行的lane,可以组成16位、32位等宽的数据通道。

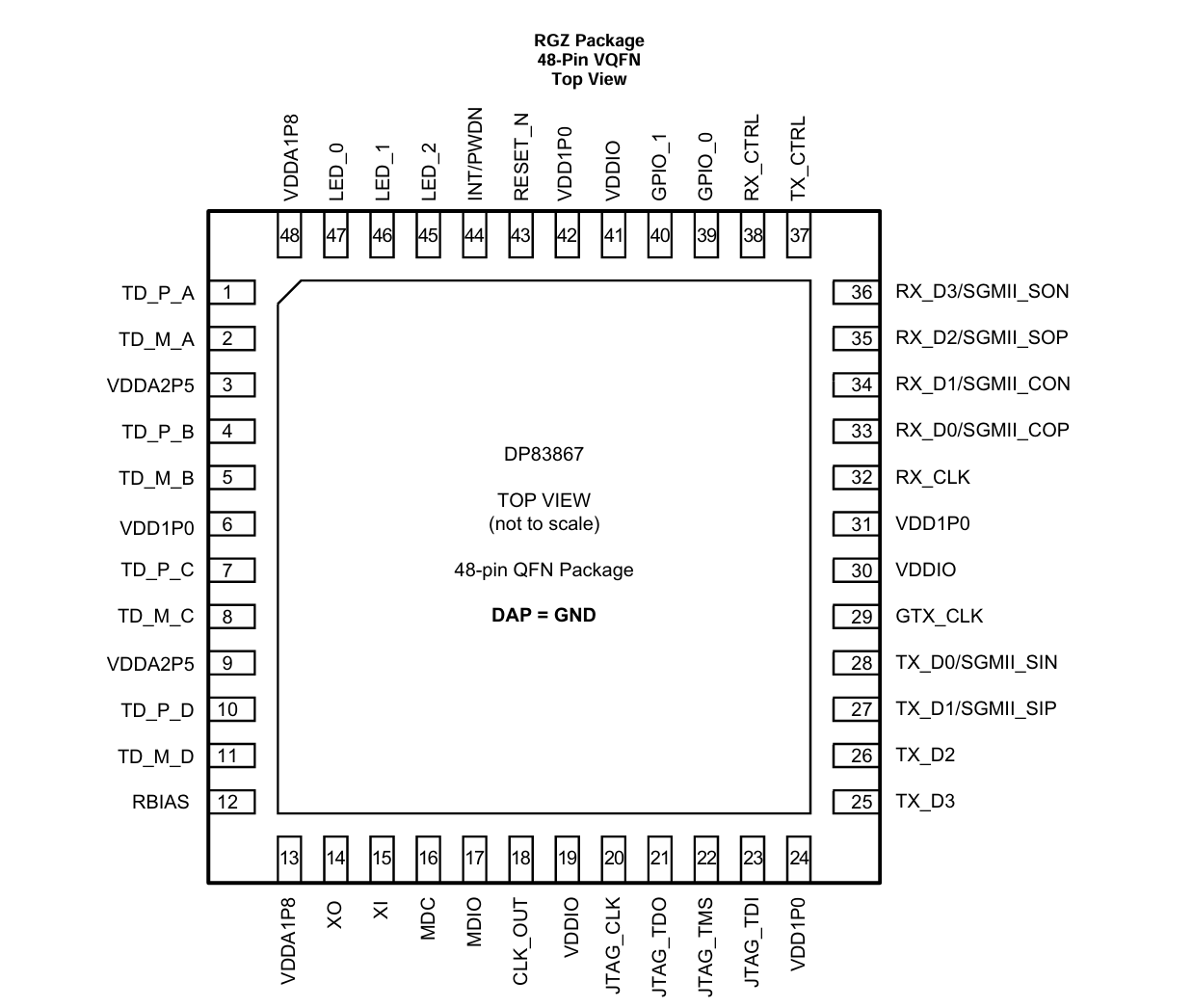

8.14 vu19p bitstream生成、SelectIO相关、MDIO

时间:8小时

主要内容:

调试后成功生成vu19p 开发板的bitstream;

阅读Virtex UltraScale+ SelectIO Resource手册;

https://docs.amd.com/v/u/en-US/ug571-ultrascale-selectio

掌握Ethernet内部寄存器的读写以及,Ethernet IP 和 PHY的连接;

virtex ultrascale+ selectIO手册 UltraScale Architecture SelectIO Resources User Guide

在 FPGA 中,PLL 指的是 Phase-Locked Loop(锁相环)。它是一个非常常见的时钟管理电路,用于生成、调整或稳定时钟信号

MMCM:Mixed-Mode Clock Manager(混合模式时钟管理器)

-

Xilinx 在 7 系列及之后 FPGA 中提供的时钟管理 IP。

-

可以说是 PLL 的增强版,除了 PLL 的功能,它还能提供更灵活的相位、延迟和分频控制。

N/A 是 Not Applicable 或 Not Available 的缩写

详情参看 博客

Virtex UltraScale(+) SelectIO BITSLICE 相关-CSDN博客

8.15 上板

时间:8小时

主要内容:

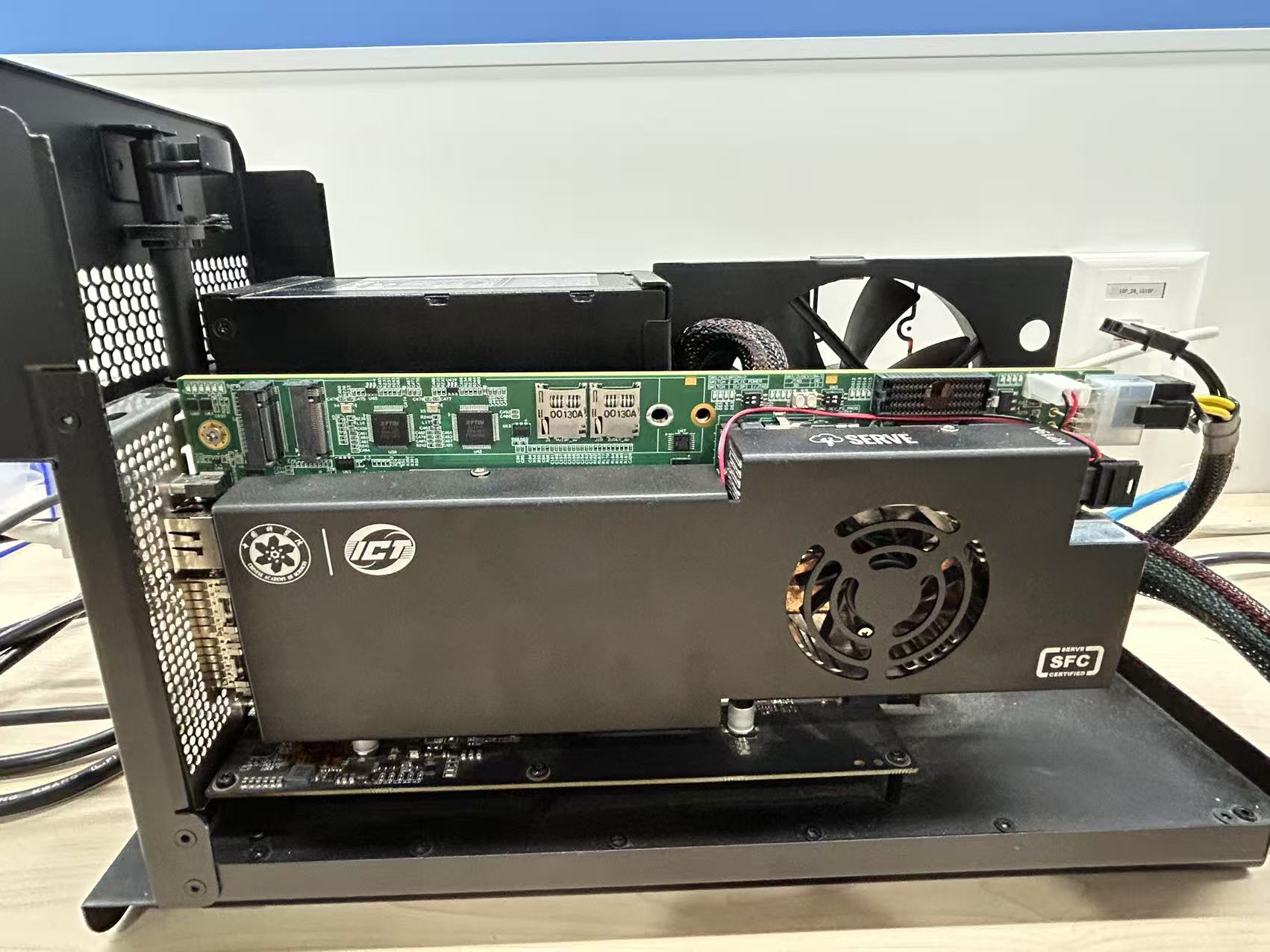

vu19p FPGA开发板

连接电脑型号:

将xdma相关参数配置正确(Device ID、Base Class Menu、PCIe to AXI_lite 相关参数);

上板加载驱动并识别PCIe设备;

读写ethernet内部寄存器;

连接Ethernet IP 与 PHY,同时读写相应地址的寄存器;

lspci

是 Linux 下一个常用的命令行工具,用来显示 PCI 总线及其连接的所有设备的信息。

常用选项

-

-v/-vv/-vvv

显示越来越详细的信息(Verbose mode)。 -

-k

显示驱动相关信息(当前设备绑定的驱动、可用驱动)。 -

-nn

同时显示厂商 ID 和设备 ID(十六进制),常用于驱动匹配。

后续问题:基本读取寄存器的方法同昨天的日志博客。但是利用对0x500地址寄存器赋值的方法没有成功实现Ethernet IP与PHY之间的连接。

8.18 定位PHY,完善片选,加入ILA调试,

时间:8小时

主要内容:

试图通过读取REGAD=2/3来寻找PHY的地址(发现行不通);

根据原理图及相应器件手册,加入相应IP实现片选始终为19p;

给MDIO加上ILA进行调试;

switch手册:

PI2DBS6212ZHEX -PDF数据手册-参考资料-立创商城

加入constant IP

8.19 修改

时间:8小时

主要内容:通过服务器上板运行发现,PHY与Ethernet之间仍然无法通信,已经确定了PHY的地址为3,继续修改设计。

8.20 加入ILA抓取MDIO进行调试

时间:8小时

主要内容:

加入ILA抓取mdio_o、mdio_t,查看Ethernet IP是否正确往PHY发送信息

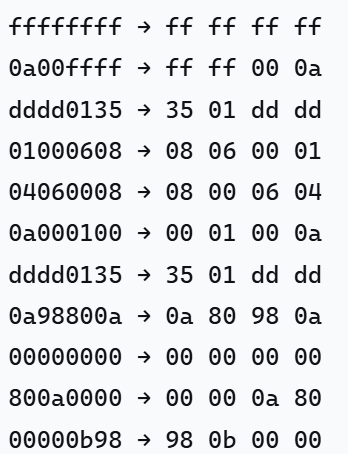

MDC/MDIO(Management Data Clock和Management Data Input/Output)主要被应用于以太网的MAC和PHY层之间,用于MAC层器件通过读写寄存器来实现对PHY层器件的操作与管理。

MDIO协议类似于IIC接线,采用2根总线进行通信,分别为MDC和MDIO信号线。分主从设备,其中主设备称作STA,从设备称作MDI,一个主设备可以对多个从设备进行命令读写操作。

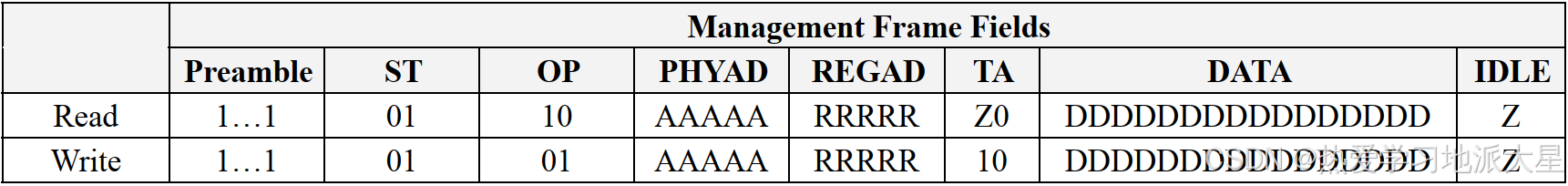

Clause22协议说明

MDIO 接口的读写通信协议如下图所示:

Preamble:32 位前导码,由 MAC 端发送 32 位逻辑“1”,用于同步 PHY 芯片。

ST(Start of Frame):2 位帧开始信号,用 01 表示。

OP(Operation Code):2 位操作码,读:10 写:01。

PHYAD(PHY Address):5 位 PHY 地址,用于表示与哪个 PHY 芯片通信,因此一个 MAC 上可以连 接多个 PHY 芯片。

REGAD(Register Address):5 位寄存器地址,可以表示共 32 位寄存器。

TA(Turnaround):2 位转向,在读命令中,MDIO 在此时由 MAC 驱动改为 PHY 驱动,在第一个 TA 位,MDIO 引脚为高阻状态,第二个 TA 位,PHY 将 MDIO 引脚拉低,准备发送数据;在写命令中,不需 要 MDIO 方向发生变化,MAC 固定输出 2’b10,随后开始写入数据。

DATA:16 位数据,在读命令中,PHY 芯片将读到的对应 PHYAD 的 REGAD 寄存器的数据写到 DATA 中;在写命令中,PHY 芯片将接收到的 DATA 写入 REGAD 寄存器中。需要注意的是,在 DATA 传 输的过程中,高位在前,低位在后。

IDLE:空闲状态,此时 MDIO 为无源驱动,处于高阻状态,但一般用上拉电阻使其上拉至高电平。

后续问题:通过ILA抓取发现mdio确实给PHY发送了相应的帧信号。故目前sgmii、mido、interrupt、restn等信号没有影响,需继续排查原因。

8.21 实现Ethernet与PHY通信,初步构建昆明湖架构中的Ethernet模块

时间:8小时

主要内容:跟进昨天的排查(首先Ethernet内部寄存器可以读写,故Ethernet及前序模块没问题,而Ethernet及PHY之间通信的mdio、sgmii也正常工作,还可能存在问题的输出引脚为RJ45_sgmii_select,检查后发现将其约束到了ETH_select,改之则成功);初步将Ethernet模块移植到昆明湖现有架构中;

.bak 文件通常是某个原始文件的 备份文件(backup file)。它不是特定格式的文件,而是一种通用的命名习惯,表示“这是某个文件的备份版本”。

示例:并排彩色对比

diff -y --color=always file1 file2

第二行用 ## 进一步标注:该 IP 放置在 SLR2(Super Logic Region 2)。在多片/多 SLR 的大 FPGA(如 Virtex UltraScale+ 系列)中,SLR 是逻辑区划分,放在特定 SLR 影响后端布局/走线和时序。

DUT(被测/被连接模块)

1. proc 命令语法

proc <过程名> {参数列表} { # 过程体(代码块) }

参数说明:

-

<过程名>:过程(函数)的名字 -

{参数列表}:参数变量的名称,可以有 0 个或多个 -

{代码块}:这个过程要执行的 Tcl 语句

8.22 搭建最终设计

时间:8小时

主要内容:

将最终Ethernet模块设计完整搭建到昆明湖架构中。

大致的思路为添加Ethernet、DMA IP及相应的配置时钟及复位的IP,利用interconnect 将该设备挂在m_axi_io总线上。

可以利用GUI配置IP及连线,配置地址,而后将tcl脚本复制导入原有工程。

后续问题:细节调试,解决error

8.25 工程建立

时间:8小时

主要内容:

初步实现shell_np19a_vu19p的工程建立及综合。

1. connect_bd_net:连接普通信号

语法:

connect_bd_net <端口或信号1> <端口或信号2> ...-

可以一次性连接多个信号。

-

适用于 clk、reset、GPIO、单bit或多bit总线 等。

示例 1:连接时钟

# 获取时钟信号并连接 connect_bd_net [get_bd_pins clk_wiz_0/clk_out1] [get_bd_pins axi_ethernet_0/ref_clk]示例 2:连接复位

connect_bd_net [get_bd_pins rst_gen_0/peripheral_aresetn] [get_bd_pins axi_ethernet_0/aresetn]示例 3:多个端口一起连

connect_bd_net \ [get_bd_pins rst_gen_0/peripheral_aresetn] \ [get_bd_pins axi_dma_0/aresetn] \ [get_bd_pins axi_bram_ctrl_0/s_axi_aresetn]2. connect_bd_intf_net:连接总线接口

语法:

connect_bd_intf_net <接口1> <接口2>-

用于 总线级接口(AXI、APB、MDIO、Ethernet MAC、DDR 接口等)。

-

保证协议层面对接正确。

示例 1:连接 AXI 主从接口

# AXI Interconnect S00_AXI <---> AXI DMA M_AXI connect_bd_intf_net [get_bd_intf_pins axi_interconnect_0/S00_AXI] \ [get_bd_intf_pins axi_dma_0/M_AXI]示例 2:连接 AXI Lite 接口

connect_bd_intf_net [get_bd_intf_pins axi_gpio_0/S_AXI] \ [get_bd_intf_pins ps7_0/M_AXI_GP0]示例 3:连接 Ethernet 接口

connect_bd_intf_net [get_bd_intf_pins axi_ethernet_0/MDIO] \ [get_bd_intf_pins mdio_0/MDIO]后续问题:

ERROR: [DRC NSTD-1] Unspecified I/O Standard: 1 out of 139 logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value. This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards. This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined. To allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: mdio_mdio_io.

ERROR: [DRC UCIO-1] Unconstrained Logical Port: 1 out of 139 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: mdio_mdio_io.

8.26 调试

时间:8小时

主要内容:修改tcl脚本及约束;

8.28 驱动相关

时间:8小时

主要内容:

成功生成bitstream;

了解驱动

1. 驱动总体架构

AXI 1G/2.5G Ethernet Subsystem 驱动由以下几层组成:

| 层次 | 主要角色 | 说明 |

|---|---|---|

| MAC 驱动(axienet driver) | 控制 AXI Ethernet 硬核 MAC | 负责 MAC 的配置、寄存器访问、收发包流程管理 |

| DMA 驱动(axidma driver / mcdma driver) | 控制 AXI DMA 或 AXI MCDMA | 负责高速数据搬运,配合 MAC 完成 TX/RX 队列 |

| PHY 驱动(phylib/PHY framework) | 控制外部或内部 PHY | 负责链路状态监测、速度协商、RGMII/SGMII 模式管理 |

| 网络协议栈(Linux Net stack) | 用户空间接口 | 提供标准的 ethX 接口,支持 ifconfig、ethtool、iperf、ptp4l 等工具 |

2. 驱动的主要组成模块

-

MAC 驱动 (

drivers/net/ethernet/xilinx/xilinx_axienet_main.c)-

管理 MAC 初始化和寄存器配置

-

控制收发队列启动、停止、复位

-

配合 DMA 层完成数据包的收发

-

对上层提供标准 Linux

net_device接口

-

-

DMA 驱动

-

AXI DMA (

axidma)-

支持单通道收发(简单应用)

-

-

AXI MCDMA (

mcdma)-

支持多队列并行收发(高性能、多流应用)

-

-

驱动负责描述符管理、内存分配、DMA 中断响应等

-

-

PHY 子系统 (

phylib)-

通过 MDIO 总线访问 PHY 寄存器

-

自动检测链路速度(1G / 2.5G)、双工模式

-

支持

ethtool查询链路状态和统计信息

-

3. 驱动关键流程

初始化阶段

-

设备树加载 → 驱动匹配 → 调用

probe() -

初始化 MAC、DMA、PHY

-

注册

net_device到 Linux 网络栈,生成ethX接口

收发数据流程

-

发送

-

应用通过 socket → Linux 网络栈

-

驱动将数据放入 DMA 描述符队列

-

DMA 将数据搬到硬核 MAC → PHY → 线缆

-

-

接收

-

MAC 收到帧 → DMA 写入内存

-

触发中断通知驱动

-

驱动将数据交给网络栈 → 应用读取

-

4. 与项目相关的实用点

设备树配置

1G/2.5G Subsystem 的设备树节点一般包含:

axi_ethernet: ethernet@40e00000 { compatible = "xlnx,axi-ethernet-1.00.a"; ... phy-mode = "sgmii"; /* 或 rgmii */ xlnx,has-mdio = <1>; xlnx,phy-type = <PHY_TYPE>; ... };确保:

-

phy-mode与硬件连接匹配 -

有效的 MDIO 节点让驱动能找到外部 PHY

-

配置了 DMA 或 MCDMA 节点与 MAC 绑定

内核配置

确保打开以下选项:

CONFIG_ETHERNET=y CONFIG_NET_VENDOR_XILINX=y CONFIG_XILINX_AXI_EMAC=y CONFIG_XILINX_PHY=y如果使用多通道 DMA:

CONFIG_AXIENET_HAS_MCDMA=y常用调试命令

-

查看网卡:

ip link show -

测试收发:

ping <ip> iperf3 -c <server_ip> -

查看链路状态:

ethtool eth0 -

查看内核日志:

dmesg | grep axienet

5. 驱动层限制

-

不支持 Pause Frame:高负载下可能掉包

-

不支持 software timestamp:只能用硬件时间戳(PTP)

-

固定速率问题:2.5G 模式下需要设置

max-speed = <2500>; -

性能瓶颈:AXI DMA 模式下单队列吞吐不足,多流建议用 MCDMA

6. 推荐调试策略

-

链路确认:用

ethtool检查 PHY 是否 up -

性能优化:大包(Jumbo Frame)、MCDMA、多队列结合使用

-

时间同步:PTP 测试用

ptp4l和phc2sys -

日志分析:抓取

dmesg与/sys/class/net/ethX/statistics/*统计信息

8.29 驱动

时间:8小时

主要内容:

根据bd、原理图等进一步修改驱动相关信息。

设备树(Device Tree)

一种描述硬件资源的数据结构,可以通过 bootloader 将它传给内核,内核(Kernal)使用它对硬件进行初始化,好处是使得内核和硬件资源描述相对独立,不需要太多的硬编码。

相关名词

-

DTS(Device Tree Source):.dts文件是一种ASCII文本对Device Tree的描述,位于linux-x.xx/arch/arm64/boot/dts目录下。

-

DTC(Device Tree Compiler):DTC为编译工具,它可以将.dts文件编译成.dtb 文件,DTC 的源码位于 linux-x.xx/scripts/dtc目录下。

-

DTB(Device Tree Blob):DTC编译.dts 生成的二进制文件(.dtb)(实际上是字节码),bootloader 在加载内核时,也会同时把.dtb加载到内存,后面传递给内核使用。

BootROM(引导只读存储器)是固化在处理器芯片内部或FPGA软核处理器内部的一小段不可修改的代码。它是系统上电或复位后第一个执行的代码,是启动过程的最初阶段,因此被称为“第一级引导加载程序”或“零级引导加载程序”。

bootrom.bin 是这个引导代码的二进制镜像文件。它的主要职责是完成最基础的硬件初始化,并加载下一阶段的、更复杂的引导程序。具体任务通常包括:

-

最小化硬件初始化:

-

设置核心的时钟、PLL。

-

初始化最关键的内存控制器(如DDR SDRAM),以便后续代码可以在更快、容量更大的外部内存中运行。

-

关闭看门狗定时器(防止系统意外复位)。

-

-

引导设备选择与探测:

-

按照预定义的顺序(或通过GPIO引脚判断)探测一个或多个引导设备,例如:

-

QSPI Flash:最常见的FPGA引导设备。

-

SD/TF卡:常见且方便调试。

-

UART:用于通过串口下载代码(如XModem协议)。

-

Ethernet:通过网络引导(如TFTP协议)。

-

-

-

加载下一阶段代码:

-

从找到的引导设备中,将下一阶段的引导程序(例如 U-Boot SPL 或 OpenSBI FW_JUMPER)读取到芯片内部SRAM或已经初始化好的外部DDR内存中。

-

内部SRAM空间非常小(几十到几百KB),所以这个阶段的代码也必须非常精简。

-

-

跳转执行:

-

验证下一阶段代码的完整性(可选,如校验CRC)。

-

将处理器的执行权移交给刚刚加载的代码,完成自己的使命。

-

| 特性 | 分析 |

|---|---|

| 文件类型 | 纯二进制机器码文件 |

| 目的 | 作为第一级引导加载程序,初始化硬件并加载第二级引导程序 |

| 运行位置 | 通常在芯片内部SRAM或ROM中 |

| 代码特点 | 极其精简,高度依赖特定硬件,多用汇编编写 |

| 后续阶段 | 通常是 OpenSBI -> U-Boot -> Linux Kernel |

bootrom.bin 是整个RISC-V系统在VCU128 FPGA上能够成功启动的“第一块基石”。 它的正确性和可靠性至关重要,如果它无法正常工作,整个系统将无法启动。在开发过程中,通常需要通过JTAG将其直接烧写到Flash中,或者通过Vivado硬件管理器将其与FPGA比特流一起加载。

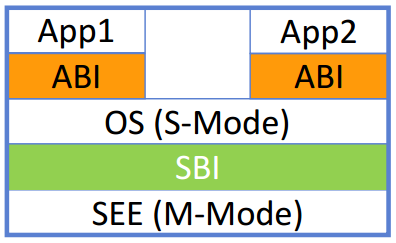

SBI

SBI指的是RISC-V Supervisor Binary Interface。

SEE指的是Supervisor Execution Environment。

SBI是类系统调用的Supervisor和SEE之间的调用转换。

他们之间的关系如下图:

SBI的作用:

- 提高不同OS之间的代码复用。

- 提供不同平台共用的OS通用驱动。

- 提供直接访问M模式下专有资源接口。

典型的RISC-V启动流程

典型的RISC-V启动流程如下,以Loader为spl、Bootloader为U-Boot、OS为Linux为例。

- 系统POR之后,从ROM开始启动。将SPL加载到SRAM中。跳转到SPL运行。

- SPL进行DDR初始化,并将OpenSBI和U-Boot加载到DDR中。跳转到OpenSBI中运行。

- OpenSBI从DDR中开始执行,进行相关设置。跳转到U-Boot中执行。

- U-Boot加载Linux到DDR中,进行解析、解压等操作。最后跳转到Linux中运行。

- 最后处于运行态的仅有OpenSBI和Linux,Linux通过sbi指令和OpenSBI进行交互。

/opt/Xilinx_2024.2/Vivado/2024.2/bin/vivado -nolog -nojour

vim ~/np19a_xiangshan_202402_dut_kmh_update_addrp_slr1/nexst/shell/np19a_vu19p/fpga/scripts/xiangshan.tcl

vim /home/zhangchaochao/nm37-xiangshan/work_farm/target/kmh/software/dt/XSTop.dts

# should executed under the work_farm directory

make PRJ="target:kmh:proto" FPGA_BD=vcu128 DT_TARGET=XSTop target_dt

make PRJ="target:kmh:proto" FPGA_BD=vcu128 ARCH=riscv phy_os.os

make PRJ="target:kmh:proto" FPGA_BD=vcu128 ARCH=riscv DT_TARGET=XSTop opensbi

# DTB

cd ~/nm37-xiangshan/kmh/ready_for_download/proto_vcu128

vim ~/nm37-xiangshan/work_farm/software/linux/arch/riscv/configs/riscv_serve_defconfig

vim ~/nm37-xiangshan/work_farm/software/linux/drivers/net/ethernet/xilinx/Kconfig

vim ~/nm37-xiangshan/work_farm/software/linux/drivers/net/ethernet/xilinx/Makefile

9.1 调试

时间:8小时

主要内容:修改dts文件的chosen后能够正常使用框架,继续修改调试。

注释

-

移动光标到要注释的第一行的行首。

-

按

Ctrl+v进入块可视模式(左下角会显示-- VISUAL BLOCK --)。 -

用方向键

↓或j选中多行的首列位置。 -

按

I(大写字母 i) 进入插入模式。 -

输入注释符,例如:

此时光标仍在第一行,不会立即出现多行注释。

-

按

<Esc>,Vim 会把刚才输入的//应用到所有选中行的开头。 -

如果想 取消注释:

-

Ctrl+v进入块模式 -

用

→或l选中// -

按

x删除

-

1. 撤销(Undo)

| 操作 | 命令 | 说明 |

|---|---|---|

| 撤销最近一次修改 | u | 普通模式下按 u |

| 撤销当前行的修改(行撤销) | U | 恢复光标所在行到最初状态 |

后续问题:

修改chosen:

chosen {

bootargs = "root=/dev/nvme0n1p2 earlycon=sbi console=ttyUL0";

};

后error -22 能够解决,但Ethernet 也还出现问题。

9.2 调试

时间:8小时

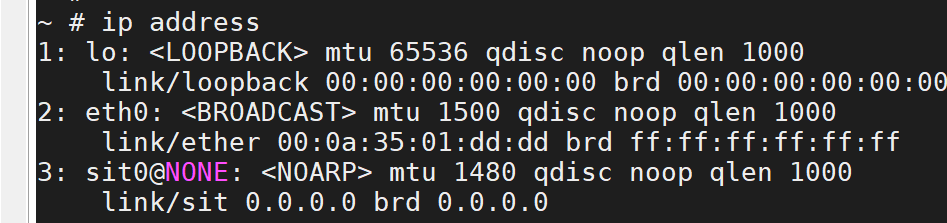

主要内容:将Ethernet 和dma对应设备树中的配置信息进行修改,对设备时钟做出相应约束,能够成功查找到Ethernet设备。

修改配置信息:

compatible = "xlnx,axi-dma-1.00.a";

compatible = "xlnx,axi-ethernet-1.00.a";

max-speed=<100000>;发现能够查找到设备,但是进一步 ip link set eht0 up没能成功启动eth设备。

后续问题:接口已启动,但物理链路未连接

9.3 调试

时间:8小时

主要内容:并行修改驱动、设备树等,实现link。

网络接口已完全就绪,eth0 网络接口现在已经完全启动并正常工作。输出信息 eth0: <BROADCAST,UP,LOWER_UP>。

但手动配置静态 IP 地址无法ping到。

9.4 ILA及示波器对数据进行探测

时间:8小时

主要内容:

在shell中添加ILA抓取一些总线的数据,同时直接利用示波器对一些开发板上的针脚进行探测,查看数据有无、频率等信息。发现PHY没有正确给MAC时钟,初始时有一个125Mhz的时钟,后续link up之后就没了。判断是PHY内部的问题。

示波器:

思路:

添加xdma读写Ethernet模块,对PHY进行配置

利用示波器探测时钟针脚(33),看看是否有625MHZ时钟。

同时添加抓取dma和Ethernet之间传输信号的ILA

后续问题:dp83867is手册 + ILA

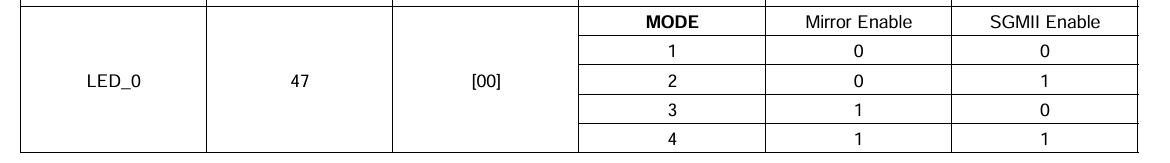

9.5 利用驱动实现了对Ethernet的读写,进一步调试

时间:8小时

主要内容:利用软件层面的驱动将sgmii_enable置1,同时也对开发板做出修改。

目前是mode1

因此Sgmii Enable没有置1

而后通过硬件上电路的修改以及上层软件的直接写入,实现设置

后续可以探测到625MHZ的时钟。

9.8 TX数据包查看

时间:8小时

主要内容:加入ila后抓取得从dma到Ethernet的数据包传输正常

TX 是数据从主机的内存(通过DMA) 移动到网卡的发送缓存,最终由以太网MAC/PHY 转换成电信号发送到网络线缆上的整个过程。

数据包:

数据包的发送流程(TX Path):

-

应用程序:应用程序通过系统调用(如

write或send)将待发送的数据写入一个 Socket 缓冲区。 -

操作系统内核:内核协议栈(TCP/IP)处理这个数据,添加协议头(TCP头、IP头、以太网MAC头),形成一个完整的以太网帧。这个帧被存放在内核内存的发送队列中。

-

驱动通知网卡:网卡驱动程序将发送队列中数据帧的内存地址和长度写入网卡的 TX DMA 环状描述符队列。这相当于告诉网卡:“去这些地方把数据取走”。

-

DMA 操作 (TX):网卡的 DMA 控制器 根据描述符队列中的信息,发起 DMA 读取操作。它不需要CPU的参与,直接通过主板上的总线(如PCIe)从主机的内存中读取完整的以太网帧数据。

-

数据到网卡:通过DMA读取的数据被传输到网卡上的内部发送缓存(FIFO) 中。

-

方向:主机内存 → 网卡芯片

-

这是最关键的一步,明确了TX DMA的方向是从主机到网卡。

-

-

MAC/PHY 发送:网卡的 MAC(媒体访问控制) 单元从发送缓存中取出数据帧,添加帧起始定界符(SFD)、CRC校验码等,然后交给 PHY(物理层) 芯片。

-

Ethernet 接口:PHY 芯片将数字信号转换成模拟电信号(遵循曼彻斯特编码或PAM4等),并通过 RJ-45 以太网接口 发送到网络线缆上。

总结与对比

| 方向 | 路径 | DMA 操作 | 数据流向 |

|---|---|---|---|

| TX (Transmit) | DMA -> Ethernet | DMA Read | 主机内存 -> 网卡内部缓存 -> 网络线缆 |

| RX (Receive) | Ethernet -> DMA | DMA Write | 网络线缆 -> 网卡内部缓存 -> 主机内存 |

地址解析协议(Address Resolution Protocol,缩写ARP)是一个通过解析网络层地址来找寻数据链路层地址的网络传输协议,它在IPv4中极其重要。

9.9 调试

时间:8小时

主要内容:修改设备树、

PCIe(Peripheral Component Interconnect Express)体系结构中的核心概念,它们代表了 PCIe 拓扑中的不同角色。

这是一个 “问-答” 或 “请求-响应” 的关系:

-

RC:系统的大脑和管理者,发起请求。

-

EP:系统的执行者,提供功能,响应请求。

-

RP:是 RC 的组成部分,作为端口或接口,用于连接 EP。

9.10 vcu128上添加Ethernet

时间:8小时

主要内容:编写tcl脚本,在vcu128的shell中添加Ethernet模块

9.11 vcu128上添加Ethernet

时间:8小时

主要内容:继续进行设计、综合

9.12 vcu128 上板调试

时间:8小时

主要内容:

359

359

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?