PS:word的多级标题转到csdn就乱了,不过不影响阅读,只是让我强迫症犯了。

结构图是简图,主要看文字理解吧。

基于MIPS指令系统的处理器设计

- MIPS指令系统介绍

1.1 MIPS概述

MIPS(Microprocessor without Interlocked Pipeline Stages,无互锁流水线微处理器)是一种精简指令集(RISC)架构,在1981年由斯坦福大学的研究小组开发,其设计初衷是为了克服传统复杂指令集计算机(CISC)架构中的性能瓶颈,提供一种更加高效、简洁的处理器架构。

MIPS指令集采用精简指令集架构(RISC),相对于传统的复杂指令集(CISC),RISC指令集更加简洁、高效。因此MIPS指令集中只包含少量简单的指令,使指令执行速度更快,同时简化了处理器的设计和实现。MIPS架构具有32个32位的通用寄存器。寄存器作为CPU内部的数据存储单元,其数量和位宽对处理器的性能有着重要影响。MIPS的32位寄存器能够满足大多数应用场景的需求,同时保证了较高的执行效率,同时尽可能地减少了指令的数量。MIPS处理器采用流水线架构,将指令执行分为多个阶段,使得多条指令可以同时执行,提高了处理器的吞吐量,进一步提升了性能。MIPS的流水线架构经过优化,能够充分利用处理器的资源,实现高效的数据处理。

MIPS指令系统以其精简的指令集、通用的多个寄存器、高效的流水线架构等优势,成为了一种高效、可靠的处理器架构,被广泛应用于个人电脑、嵌入式系统、游戏控制台、网络设备和超级计算机等多个领域。

1.2 MIPS指令格式

MIPS指令集的所有指令均为固定字长,长度为32位(4字节),被分为三类:R类指令、I类指令和J类指令。

R类指令包含6位操作码(op)、两个源寄存器(rs、rt)、一个目的寄存器(rd)、一个6位功能码(func)以及(对于某些指令)一个5位移位量字段(shamt)。用于执行各种算术、逻辑、比较以及数据处理操作,R类指令的操作通常涉及三个寄存器之间的交互。

| Bit# | 31…26 | 25…21 | 20…16 | 15…11 | 10…6 | 5…0 |

| R类指令 | op | rs | rt | rd | shamt | func |

表1.2.1 R类指令格式

I类指令包含6位操作码(op)、源寄存器(rs)、目的寄存器(rt)以及一个16位的立即数(immediate)。常用于执行算术逻辑运算、加载/存储操作以及其他直接使用立即数的操作。

| Bit# | 31…26 | 25…21 | 20…16 | 15…0 |

| I类指令 | op | rs | rt | immediate |

表1.2.2 I类指令格式

J类指令包含6位操作码(op)和一个26位的目标地址(target)。专用于实现无条件跳转和分支操作,如函数调用、循环控制等。

| Bit# | 31…26 | 25…0 |

| J类指令 | op | address |

表1.2.3 J类指令格式

1.3 MIPS寄存器

MIPS架构的处理器共有32个通用寄存器,均为32位。不同寄存器硬件上完全相同,功能上各不相同。

| 寄存器编号 | 别名 | 功能 |

| $0 | $zero | Constant 0 |

| $1 | $at | Assembly Temporary |

| $2,$3 | $v0,$v1 | Function Result |

| $4—$7 | $a0—$a3 | Argument 1 to 4 |

| $8—$15 | $t0—$t7 | Unsaved Temporary |

| $16—$23 | $s0—$s7 | Saved Temporary |

| $24,$25 | $t8,$t9 | Unsaved Temporary |

| $26,$27 | $k0,$k1 | Reserved for EXCEPTION |

| $28 | $gp | Pointer to Global Data |

| $29 | $sp | Stack Pointer |

| $30 | $fp | Frame Pointer |

| $31 | $ra | Return Address |

表1.3.1 MIPS寄存器

本文选择具有代表性的lw,sw,j,add,sub这五条指令进行设计。

lw指令是取数指令,属于I类指令,其汇编格式为lw rt, offset(rs),其功能为rt ← memory[rs + (sign-extend) offset],即将offset进行位拓展后与rs寄存器中数据相加获得访存地址,然后从该地址中取出数据并存到rt寄存器中。

| Bit# | 31…26 | 25…21 | 20…16 | 15…0 |

| lw指令 | 100011 | rs | rt | offset |

表2.1.1 lw指令格式

sw指令是存数指令,属于I类指令,其汇编格式为sw rt, offset(rs),其功能为memory[rs + (sign-extend) offset] ← rt,即将offset进行位拓展后与rs寄存器中数据相加获得访存地址,然后从rt寄存器中取出数据存到该地址中。

| Bit# | 31…26 | 25…21 | 20…16 | 15…0 |

| sw指令 | 101011 | rs | rt | offset |

表2.1.2 sw指令格式

j指令是无条件跳转指令,属于J类指令,其汇编格式为j address,其功能为PC ← (PC+4)[31..28],address/4,0,0,即将顺序指令地址PC+4的高4位作为高地址部分(31…28位),并与指令字中的 26 位立即数address左移两位得到的28位数据进行拼接,生成一个32位的无条件跳转目标地址,将该地址送入PC实现跳转。

| Bit# | 31…26 | 25…0 |

| j指令 | 000010 | address |

表2.1.3 j指令格式

add指令是加法指令,属于R类指令,其汇编格式为add rd, rs, rt,其功能为rd ← rs + rt,即将rs中的加数与rt中的加数送入ALU中运算,得到和,将结果送到rd中,完成32位整数加法运算。

| Bit# | 31…26 | 25…21 | 20…16 | 15…11 | 10…6 | 5…0 |

| add指令 | 000000 | rs | rt | rd | 00000 | 100000 |

表2.1.4 add指令格式

sub指令是减法指令,属于R类指令,其汇编格式为sub rd, rs, rt,其功能为rd ← rs - rt,即将rs中的被减数与rt中的减数送入ALU中运算,得到差,将结果送到rd中,完成32位整数减法运算。

| Bit# | 31…26 | 25…21 | 20…16 | 15…11 | 10…6 | 5…0 |

| sub指令 | 000000 | rs | rt | rd | 00000 | 100010 |

表2.1.5 sub指令格式

2.2 微操作定义

一条指令的指令周期一般被分为取指周期、间址周期、执行周期和中断周期。本文选取的5个指令的指令周期只需要考虑取指周期和执行周期,又可以细分为取指,取数,执行,访存,写回五个阶段。根据这五个阶段的划分,考虑单总线CPU结构和MIPS架构的32个通用寄存器来进行这5个指令的微操作的定义。

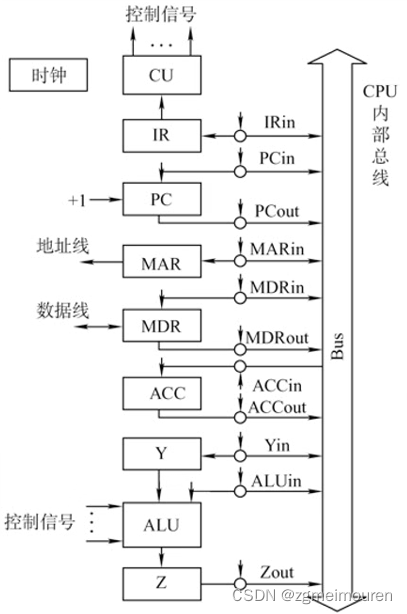

图2.2.1 单总线CPU内部结构

2.2.1 lw指令

汇编格式为lw rt, offset(rs)。指令字长32位,其中0…15位为offset,16…20位为寄存器rt,21…25位为寄存器rs,26…31位为操作码。

取指阶段:

| 微操作 | 微操作命令 | 含义 |

| PC→MAR | PCout,MARin | 将PC中指令地址通过Bus送入MAR |

| 1→R | MemR=1 | 读主存有效 |

| M(MAR)→MDR | MARout,MDRin | 从主存的MAR地址读取指令送入MDR |

| MDR→IR | MDRout,IRin | 将MDR中的指令送入IR |

| OP(IR)→CU | IRout | 将IR中指令的操作码送入CU |

| (PC)+4→PC | +4 | PC+4 |

表2.2.1.1 lw指令取指微操作序列

取数阶段:

| 微操作 | 微操作命令 | 含义 |

| R(IR[21…25])→Y | R(IR[21…25])out,Yin | 将寄存器rs内的地址送入Y |

表2.2.1.2 lw指令取数微操作序列

执行阶段:

| 微操作 | 微操作命令 | 含义 |

| Y+Extended(IR[0…15])→Z | Yout,ALU+,Zin | 将Y与位扩展的offset求和送入Z |

表2.2.1.3 lw指令执行微操作序列

访存阶段:

| 微操作 | 微操作命令 | 含义 |

| Z→MAR | Zout,MARin | 将Z中的运算后的地址送入MAR |

| 1→R | MemR=1 | 读主存有效 |

| M(MAR)→MDR | MARout,MDRin | 从主存中MAR地址读取指令送入MDR |

表2.2.1.4 lw指令访存微操作序列

写回阶段:

| 微操作 | 微操作命令 | 含义 |

| MDR→R(IR[16…20]) | MDRout, R(IR[16…20])in | 将MDR中的数据送入寄存器rt |

表2.2.1.5 lw指令写回微操作序列

2.2.2 sw指令

汇编格式为sw rt, offset(rs)。指令字长32位,其中0…15位为offset,16…20位为寄存器rt,21…25位为寄存器rs,26…31位为操作码。sw指令没用写回阶段。

取指阶段:

| 微操作 | 微操作命令 | 含义 |

| PC→MAR | PCout,MARin | 将PC中指令地址通过Bus送入MAR |

| 1→R | MemR=1 | 读主存有效 |

| M(MAR)→MDR | MARout,MDRin | 从主存的MAR地址读取指令送入MDR |

| MDR→IR | MDRout,IRin | 将MDR中的指令送入IR |

| OP(IR)→CU | IRout | 将IR中指令的操作码送入CU |

| (PC)+4→PC | +4 | PC+4 |

表2.2.2.1 sw指令取指微操作序列

取数阶段:

| 微操作 | 微操作命令 | 含义 |

| R(IR[21…25])→Y | R(IR[21…25])out,Yin | 将寄存器rs内的地址送入Y |

表2.2.2.2 sw指令取数微操作序列

执行阶段:

| 微操作 | 微操作命令 | 含义 |

| Y+Extended(IR[0…15])→Z | Yout,ALU+,Zin | 将Y与位扩展的offset求和送入Z |

表2.2.2.3 sw指令执行微操作序列

访存阶段:

| 微操作 | 微操作命令 | 含义 |

| Z→MAR | Zout,MARin | 将Z中的运算后的地址送入MAR |

| R(IR[16…20])→MDR | R(IR[16…20])out, MDRin | 将寄存器rt中的数据送入MDR |

| 1→W | MemW=1 | 写主存有效 |

| MDR→M(MAR) | MDRout,MARout | 将MDR数据写入主存中MAR地址位置 |

表2.2.2.4 sw指令访存微操作序列

2.2.3 j指令

汇编格式为j address。指令字长32位,其中0…25位为跳转目标地址,26…31位为操作码。

取指阶段:

| 微操作 | 微操作命令 | 含义 |

| PC→MAR | PCout,MARin | 将PC中指令地址通过Bus送入MAR |

| 1→R | MemR=1 | 读主存有效 |

| M(MAR)→MDR | MARout,MDRin | 从主存的MAR地址读取指令送入MDR |

| MDR→IR | MDRout,IRin | 将MDR中的指令送入IR |

| OP(IR)→CU | IRout | 将IR中指令的操作码送入CU |

| (PC)+4→PC | +4 | PC+4 |

表2.2.3.1 j指令取指微操作序列

执行阶段:

| 微操作 | 微操作命令 | 含义 |

| {PC,IR[0…25],0,0}→PC | PCin | 将生成的跳转目标地址送入PC |

表2.2.3.2 j指令执行微操作序列

2.2.4 add指令

汇编格式为add rd, rs, rt。指令字长32位,其中0…5位为func,6…10位为shamt,11…15位为寄存器rd,16…20位为寄存器rt,21…25位为寄存器rs,26…31位为操作码。6…10位的shamt为00000。

取指阶段:

| 微操作 | 微操作命令 | 含义 |

| PC→MAR | PCout,MARin | 将PC中指令地址通过Bus送入MAR |

| 1→R | MemR=1 | 读主存有效 |

| M(MAR)→MDR | MARout,MDRin | 从主存的MAR地址读取指令送入MDR |

| MDR→IR | MDRout,IRin | 将MDR中的指令送入IR |

| OP(IR)→CU | IRout | 将IR中指令的操作码送入CU |

| (PC)+4→PC | +4 | PC+4 |

表2.2.4.1 add指令取指微操作序列

取数阶段:

| 微操作 | 微操作命令 | 含义 |

| R(IR[21…25])→Y | R(IR[21…25])out,Yin | 将寄存器rs内的加数送入Y |

表2.2.4.2 add指令取数微操作序列

执行阶段:

| 微操作 | 微操作命令 | 含义 |

| Y+R(IR[16…20])→Z | Yout, R(IR[16…20])out,Zin | 将Y与寄存器rt中的加数求和送入Z |

表2.2.4.3 add指令执行微操作序列

写回阶段:

| 微操作 | 微操作命令 | 含义 |

| Z→R(IR[11…15]) | Zout,R(IR[11…15])in | 将Z中的和送入寄存器rd |

表2.2.4.4 add指令写回微操作序列

2.2.5 sub指令

汇编格式为sub rd, rs, rt。指令字长32位,其中0…5位为func,6…10位为shamt,11…15位为寄存器rd,16…20位为寄存器rt,21…25位为寄存器rs,26…31位为操作码。6…10位的shamt为00000。

取指阶段:

| 微操作 | 微操作命令 | 含义 |

| PC→MAR | PCout,MARin | 将PC中指令地址通过Bus送入MAR |

| 1→R | MemR=1 | 读主存有效 |

| M(MAR)→MDR | MARout,MDRin | 从主存的MAR地址读取指令送入MDR |

| MDR→IR | MDRout,IRin | 将MDR中的指令送入IR |

| OP(IR)→CU | IRout | 将IR中指令的操作码送入CU |

| (PC)+4→PC | +4 | PC+4 |

表2.2.5.1 sub指令取指微操作序列

取数阶段:

| 微操作 | 微操作命令 | 含义 |

| R(IR[21…25])→Y | R(IR[21…25])out,Yin | 将寄存器rs内的被减数送入Y |

表2.2.5.2 sub指令取数微操作序列

执行阶段:

| 微操作 | 微操作命令 | 含义 |

| Y-R(IR[16…20])→Z | Yout, R(IR[16…20])out,Zin | 将Y与寄存器rt中的减数作差送入Z |

表2.2.5.3 sub指令执行微操作序列

写回阶段:

| 微操作 | 微操作命令 | 含义 |

| Z→R(IR[11…15]) | Zout,R(IR[11…15])in | 将Z中的差送入寄存器rd |

表2.2.5.4 sub指令写回微操作序列

2.3 节拍划分

节拍划分应当遵循三项原则:原则一,微操作的先后顺序不得随意更改;原则二,被控对象不同的微操作尽量安排在一个节拍内完成;原则三,占用时间较短的微操作尽量安排在一个节拍内完成,并允许有先后顺序。

2.3.1 取指阶段

5条指令取指阶段的微操作序列相同,进行统一的节拍划分。

| 节拍 | 微操作 |

| T0 | PC→MAR,1→R |

| T1 | M(MAR)→MDR,(PC)+4→PC |

| T2 | MDR→IR,OP(IR)→ID |

表2.3.1.1 取指阶段节拍划分

2.3.2 取数阶段

lw指令,sw指令,add指令,sub指令具有取数阶段,且4条指令取数阶段的微操作序列相同。

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | R(IR[21…25])→Y |

表2.3.2.1 取数阶段节拍划分

2.3.3 执行阶段

5条指令执行阶段不完全相同,分别进行节拍划分。

lw指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | Y+Extended(IR[0…15])→Z |

表2.3.3.1 lw指令执行阶段节拍划分

sw指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | Y+Extended(IR[0…15])→Z |

表2.3.3.2 sw指令执行阶段节拍划分

j指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | {PC,IR[0…25],0,0}→PC |

表2.3.3.3 j指令执行阶段节拍划分

add指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | Y+R(IR[16…20])→Z |

表2.3.3.4 add指令执行阶段节拍划分

sub指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | Y-R(IR[16…20])→Z |

表2.3.3.5 sub指令执行阶段节拍划分

2.3.4 访存阶段

lw指令,sw指令具有访存阶段,访存阶段各有不同,分别进行节拍划分。

lw指令:

| 节拍 | 微操作 |

| T0 | Z→MAR,1→R |

| T1 | M(MAR)→MDR |

| T2 |

表2.3.4.1 lw指令访存阶段节拍划分

sw指令:

| 节拍 | 微操作 |

| T0 | Z→MAR,1→W |

| T1 | R(IR[16…20])→MDR |

| T2 | MDR→M(MAR) |

表2.3.4.2 sw指令访存阶段节拍划分

2.3.5 写回阶段

lw指令,add指令,sub指令具有写回阶段,add指令与sub指令写回阶段相同。

lw指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | MDR→R(IR[16…20]) |

表2.3.5.1 lw指令写回阶段节拍划分

add指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | Z→R(IR[11…15]) |

表2.3.5.2 add指令写回阶段节拍划分

sub指令:

| 节拍 | 微操作 |

| T0 | |

| T1 | |

| T2 | Z→R(IR[11…15]) |

表2.3.5.3 sub指令写回阶段节拍划分

2.4 控制器设计

本文控制器设计采用组合逻辑设计,这是由于本文只实现5条简单指令,指令数目较少,指令形式简单,适用于硬布线的组合逻辑设计,且组合逻辑设计思路清晰,简单明了,控制器运行速度快。

2.4.1 操作时间表

设计采用组合逻辑设计的控制器,首先需要列出各阶段的操作时间表。

取指阶段:

| 工作阶段 | 节拍 | 微操作命令 | lw | sw | j | add | sub |

| IF取指 | T0 | PC→MAR | 1 | 1 | 1 | 1 | 1 |

| 1→R | 1 | 1 | 1 | 1 | 1 | ||

| T1 | M(MAR)→MDR | 1 | 1 | 1 | 1 | 1 | |

| (PC)+4→PC | 1 | 1 | 1 | 1 | 1 | ||

| T2 | MDR→IR | 1 | 1 | 1 | 1 | 1 | |

| OP(IR)→ID | 1 | 1 | 1 | 1 | 1 |

表2.4.1.1 取指阶段操作时间表

取数阶段:

| 工作阶段 | 节拍 | 微操作命令 | lw | sw | j | add | sub |

| ID取数 | T0 | ||||||

| T1 | |||||||

| T2 | R(IR[21…25])→Y | 1 | 1 | 1 | 1 |

表2.4.1.2 取数阶段操作时间表

执行阶段:

| 工作阶段 | 节拍 | 微操作命令 | lw | sw | j | add | sub |

| EX执行 | T0 | ||||||

| T1 | |||||||

| T2 | Y+Extended(IR[0…15])→Z | 1 | 1 | ||||

| {PC,IR[0…25],0,0}→PC | 1 | ||||||

| Y+R(IR[16…20])→Z | 1 | ||||||

| Y-R(IR[16…20])→Z | 1 |

表2.4.1.3 执行阶段操作时间表

访存阶段:

| 工作阶段 | 节拍 | 微操作命令 | lw | sw | j | add | sub |

| MEM访存 | T0 | Z→MAR | 1 | 1 | |||

| 1→W | 1 | ||||||

| 1→R | 1 | ||||||

| T1 | M(MAR)→MDR | 1 | |||||

| R(IR[16…20])→MDR | 1 | ||||||

| T2 | MDR→M(MAR) | 1 |

表2.4.1.4 访存阶段操作时间表

写回阶段:

| 工作阶段 | 节拍 | 微操作命令 | lw | sw | j | add | sub |

| WB写回 | T0 | ||||||

| T1 | |||||||

| T2 | MDR→R(IR[16…20]) | 1 | |||||

| Z→R(IR[11…15]) | 1 | 1 |

表2.4.1.5 写回阶段操作时间表

2.4.2 最简表达式

根据列出的操作时间表,可以写出微操作命令的最简表达式。共17条不同的微操作命令,最简表达式分别为:

(1)PC→MAR

= IF*T0

(2)1→R

= IF*T0 + MEM*T0*(lw)

(3)M(MAR)→MDR

= IF*T1 + MEM*T1*(lw)

(4)(PC)+4→PC

= IF*T1

(5)MDR→IR

= IF*T2

(6)OP(IR)→ID

= IF*T2

(7)R(IR[21…25])→Y

= ID*T2*(lw + sw + add + sub)

(8)Y+Extended(IR[0…15])→Z

= EX*T2*(lw + sw)

(9){PC,IR[0…25],0,0}→PC

= EX*T2*(j)

(10)Y+R(IR[16…20])→Z

= EX*T2*(add)

(11)Y-R(IR[16…20])→Z

= EX*T2*(sub)

(12)Z→MAR

= MEM*T0*(lw + sw)

(13)1→W

= MEM*T0*(sw)

(14)R(IR[16…20])→MDR

= MEM*T1*(sw)

(15)MDR→M(MAR)

= MEM*T2*(sw)

(16)MDR→R(IR[16…20])

= WB*T2*(lw)

(17)Z→R(IR[11…15])

= WB*T2*(add + sub)

2.5 处理器结构及功能

2.5.1 处理器结构框图

针对所选取的5条经典指令,本文设计了一个简单处理器模型来实现这5条指令。

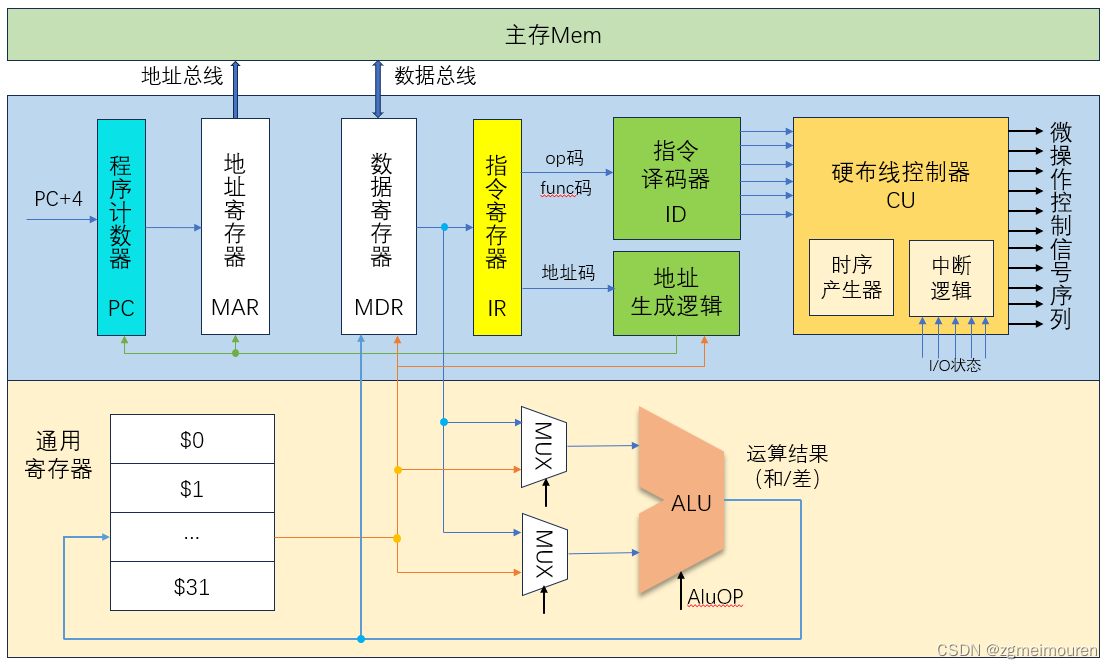

图2.5.1.1 针对5条指令的处理器模型结构框图

2.5.2 处理器各结构功能

程序计数器(PC):

保存将要执行的指令的地址。CPU在执行程序时,需要按照指令的顺序依次执行每个指令,PC中保存将要执行的指令的地址来确保CPU执行完一条指令后能够顺利调取下一条指令并执行。

对于本文的处理器而言,指令字长均为4字节,因此每执行完一条指令需要PC+4来得到下一条指令的地址,PC+4由单独的运算器实现。同时,PC能够接收到地址生成逻辑发出的跳转地址,以此来实现j指令的无条件跳转。

地址寄存器(MAR):

保存CPU访问主存的地址。在CPU需要访问主存时,地址都要先传入MAR,MAR通过地址总线与主存相连,CPU经过MAR与地址总线来访问主存。

数据寄存器(MDR):

保存从主存储器中读取的数据或准备写入主存储器的数据。MDR与CPU的数据总线和主存储器的数据总线相连,负责在CPU和主存储器之间传输数据。当CPU需要从主存储器读取数据时,MDR会接收这些数据;当CPU需要向主存储器写入数据时,MDR会发送这些数据。

指令寄存器(IR):

暂存当前正在执行的指令。每个周期IR会从内存中读取当前要执行的指令,供CPU进行解析和执行。

指令译码器(ID):

对从指令寄存器IR中获取的指令op码和func码进行分析译码,得到译码信号传入根据2.4中组合逻辑设计的硬布线控制器产生微操作控制信号序列。

地址生成逻辑:

负责lw,sw,j指令的地址运算,其中应包括一个运算器来执行加法运算实现lw和sw的地址偏移,还应有一个位扩展单元进行j指令需要的位扩展以及左移两位的逻辑电路从而实现j指令的地址运算。

硬布线控制器(CU):

接收ID发送的译码信号,通过设计好的逻辑电路得到微操作控制信号序列,实现对各个通路控制开关的控制,进而完成指令的执行。

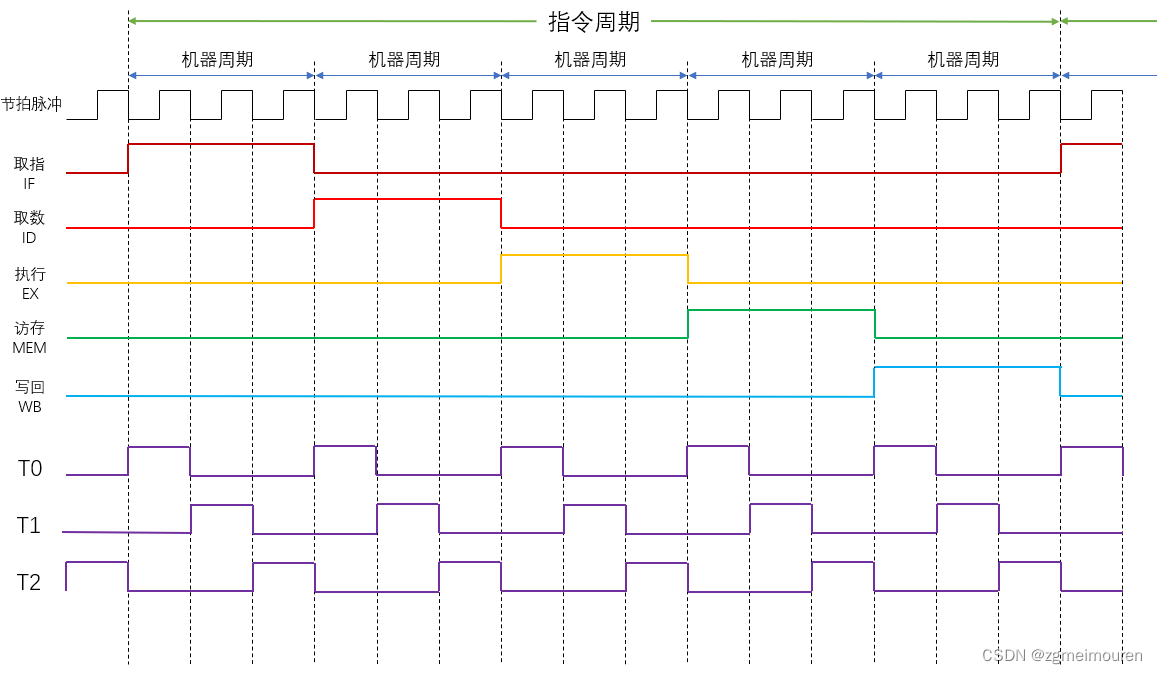

其中的时序产生器负责节拍信号以及阶段信号的产生。一个指令周期共有取指,取数,执行,访存,写回五个阶段,每个阶段由三个节拍构成,共十五个节拍。

图2.5.2.1 时序产生器输出

由5条指令得到5种译码信号lw,sw,j,add,sub,结合时序产生器的输出经由逻辑电路得到2.4中17种微操作命令对应的微操作控制信号序列。

通用寄存器(GR):

能够存储数据,来实现多种功能。本文基于MIPS架构,共有32个通用寄存器($0~$31),每个寄存器具有各自的功能,在表1.3.1中介绍了各个寄存器的具体功能。

算术逻辑单元(ALU):

执行基本的算术和逻辑运算,支持实现二进制加减乘除以及取模等算术运算,与或非异或等逻辑运算,还有二进制的位移操作。本文设计的ALU只需要有加减移位功能即可满足5条指令的实现要求。

以微操作最多的lw指令为例,结合图2.5.1.1的处理器简单模型和图2.5.2.1的时序图,展示lw rt, offset(rs)实现的过程。

第一个时钟周期,时序产生器发出IF信号与T0信号,信号通过控制器中的逻辑电路输出PC→MAR,1→R的信号,信号使得PCout与MARin打开,R置为1。PC中的指令地址被送入MAR和一个加法运算器中,主存处于可读状态。

第二个时钟周期,时序产生器发出IF信号与T1信号,信号通过控制器中的逻辑电路输出M(MAR)→MDR,(PC)+4→PC的信号,信号使得MDRin和PCin打开。主存中的指令被送入MDR,PC中的指令地址更新为PC+4。

第三个时钟周期,时序产生器发出IF信号与T2信号,信号通过控制器中的逻辑电路输出MDR→IR,OP(IR)→ID的信号,信号使得MDRout,IRin和OP(IR)out打开。MDR中的指令被送入IR,IR中的指令的op码和func码被送入指令译码器得到lw信号,地址码被送入地址生成逻辑。

第四个时钟周期,没有微操作需要执行。

第五个时钟周期,没有微操作需要执行。

第六个时钟周期,时序产生器发出ID信号与T2信号,与lw信号一起通过控制器中的逻辑电路输出R(IR[21…25])→Y的信号,信号使得源寄存器rs的out和Yin打开。源寄存器rs中的地址信息被送入地址生成逻辑的运算器中。

第七个时钟周期,没有微操作需要执行。

第八个时钟周期,没有微操作需要执行。

第九个时钟周期,时序产生器发出EX信号与T2信号,与lw信号一起通过控制器中的逻辑电路输出Y+Extended(IR[0…15])→Z的信号,信号使得Yout和Zin打开,运算器做加法运算。偏移后的地址被送入到Z暂存。

第十个时钟周期,时序产生器发出MEM信号与T0信号,与lw信号一起通过控制器中的逻辑电路输出1→R,Z→MAR的信号,信号使得R置为1,Zout和MARin打开。偏移后的地址被送入到MAR中。

第十一个时钟周期,时序产生器发出MEM信号与T1信号,与lw信号一起通过控制器中的逻辑电路输出M(MAR)→MDR的信号,信号使得MDRin打开。主存中的数据被送入MDR中。

第十二个时钟周期,没有微操作需要执行。

第十三个时钟周期,没有微操作需要执行。

第十四个时钟周期,没有微操作需要执行。

第十五个时钟周期,时序产生器发出WB信号与T2信号,与lw信号一起通过控制器中的逻辑电路输出MDR→R(IR[16…20])的信号,信号使得目标寄存器rt的in 和MDRout打开。MDR中的数据被送入目标寄存器rt。

其余四条指令的实现过程与lw相同。首先时序产生器产生时序信号,控制器根据时序信号完成取指,译码后得到指令信号,在之后的阶段中指令信号与时序信号一起产生控制信号,完成指令的执行过程。

3658

3658

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?