本文由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。

烧写JIC的过程实际分为两步

第一步,使用JTAG模式烧写一个FLASH Loader固件到FPGA中;

第二步,使用该FLASH Loader固件将JTAG传输的FPGA的配置文件写入到EPCS FLASH中。

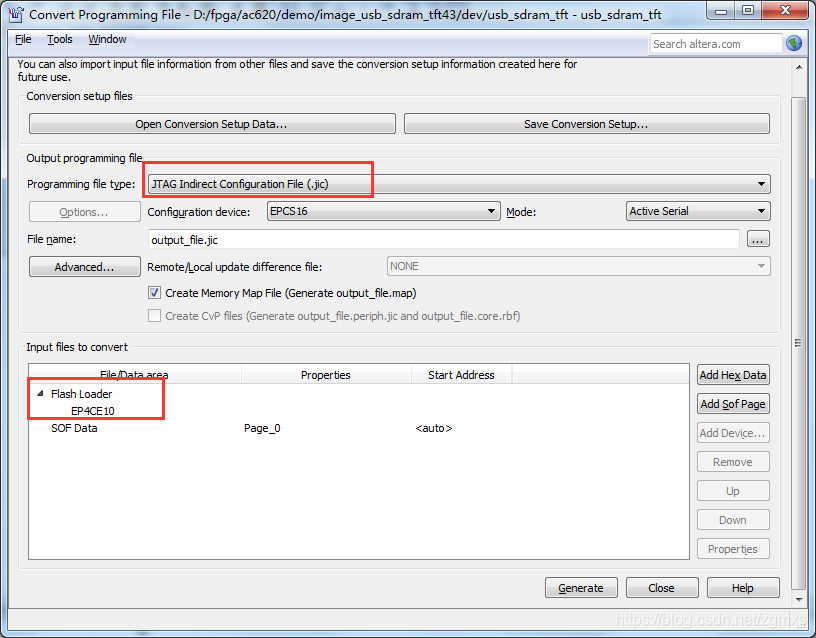

要想通过JTAG直接将数据写入到EPCS FLASH中是不那么方便的,所以Altera采用了FPGA转发的方式,在生成JIC文件时,有一个设置是在Flash Loader选项下选择被配置的FPGA器件,然后才是添加一个SOF Data,如下图所示。那么这个Flash Loader,通俗一点理解,就是Altera预先设计好的一段逻辑,从效果上等同于用户自己设计一个接受JTAG的数据并写入SPI FLASH的逻辑。所以,合成JIC文件时,就在JIC文件的某个位置插入了该逻辑的配置文件(相当于sof),然后,才是加上了用户自己设计好的逻辑的配置文件。

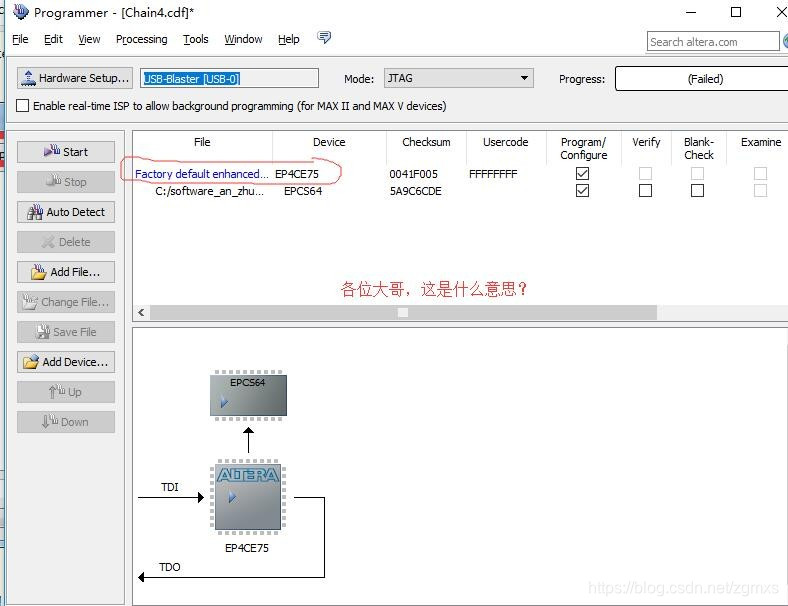

所以,当用户希望将自己的FPGA配置文件固化到EPCS存储器中时,当转换得到JIC文件后,在Quartus Programmer软件中添加好该JIC文件之后,可以看到软件检测出来了两个文件,第一个文件名为Factory default enhanced SFL image,第二个才是用户自己的设计文件,如下图所示:

所以烧写的时候大家应该也能够看到,实际上烧写一般会有三次进度条,第一次速度最快,那就是在下载这个FLASH Loader文件,当该文件下载进入FPGA之后,FPGA就变成可一个能够接受JTAG数据并按照SPI FLASH的接口协议将数据写入到FLASH中的烧写器。第二次更新进度条,则是对EPCS FLASH进行擦除操作,当EPCS FLASH擦除之后,最后才是耗时最长的一次进度条更新,这一次才是将用户设计烧写到EPCS FLASH中。

所以,有用户希望直接使用JIC文件来,通过其他方式,如FLASH离线烧录器等方式来批量烧写FPGA固件到EPCS中是行不通的。因为这个文件不纯洁,要纯洁的文件,可以考虑rbf文件。

1959

1959

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?