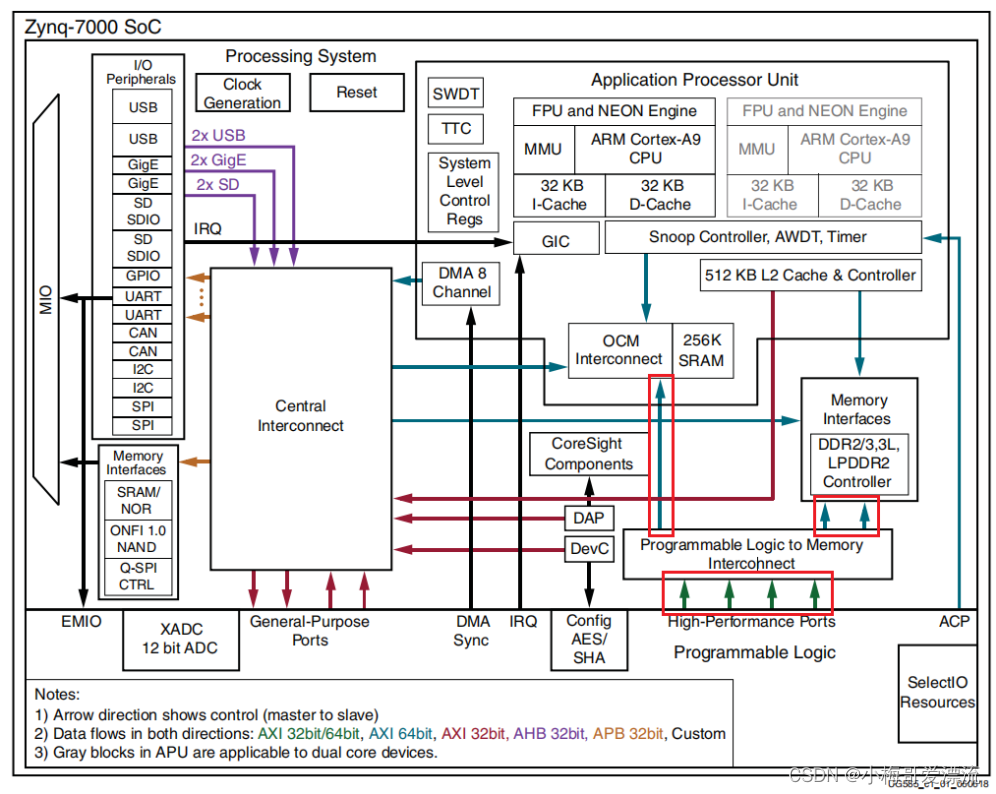

首先来说,Xilinx的ZYNQ7000系列器件是一个包含了通用可编程逻辑(FPGA,我们常称为PL),以及基于ARM处理器的系统(我们常称之为PS)

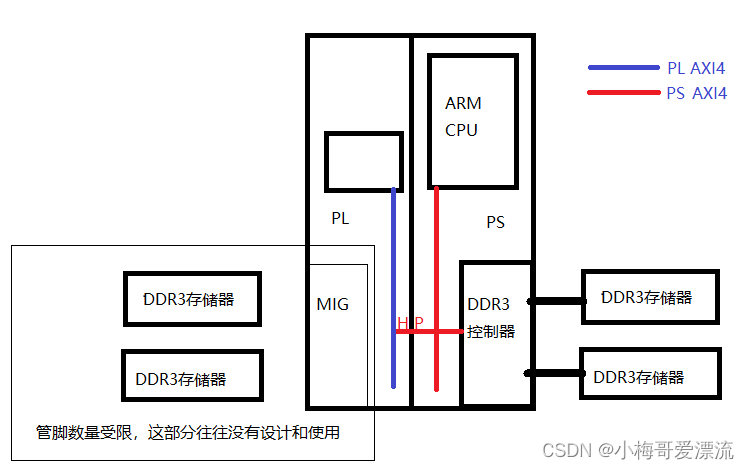

其次来讲,PL和PS部分都支持DDR3存储器。PS部分是集成了一个DDR3硬核控制器,PL部分也提供DDR3硬核控制器

PS部分的DDR3主要用作ARM CPU的内存系统,ARM CPU的程序可以在该DDR3中运行

PL部分如果要使用DDR3存储器,则需要通过在IP Catlog中调用MIG IP来创建DDR3控制器。

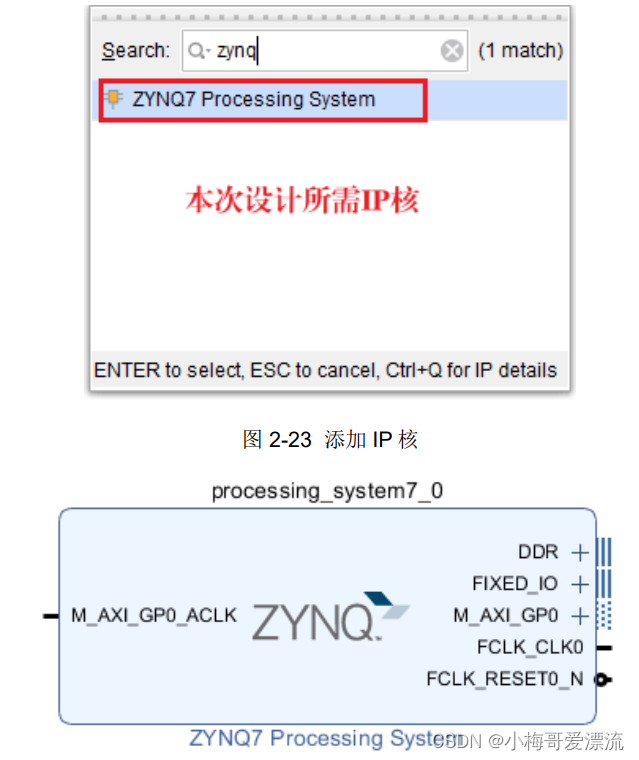

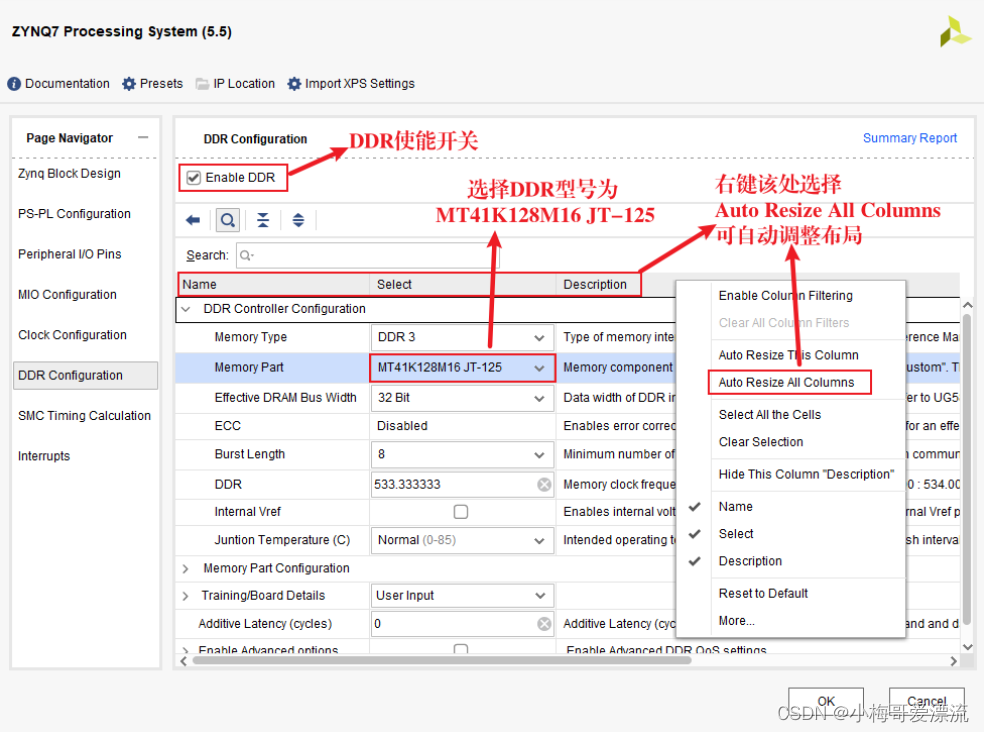

PS部分的DDR3存储器使用,不需要,也不能调用MIG IP来控制,只需要在设计中添加ZYNQ7 Processing System 组件,并配置好DDR相关的参数,即可使用。例如,ACZ702开发板的DDR3型号为MT41K128M16 JT-125,而ACZ7015开发板的DDR型号为MT41K256M16 RE-125。

PS部分的DDR3管脚位置是绝对固定的,不能通过XDC中管脚约束的方式进行指定和修改,也不需要通过XDC的方式进行指定和修改。

如果PL部分没有设计外部DDR3存储器,则无法使用PL自己的DDR3存储器,当然也就更不存在调用MIG IP的操作了。

如果PL部分想用DDR3存储器,但是PL部分又没有设计该部分电路怎么办呢,可以使用PS侧底DDR3存储器。

PS引出了4个高性能数据交互端口,以使PL能够通过AXI4接口直接访问PS侧的DDR3存储器空间。

回到ACZ702开发板本身,该开发板PS侧设计了32位的DDR3存储器模组,但PL侧没有再设计独立的DDR3存储器,PL侧不设计独立的DDR3存储器主要是因为PL侧总共也就100或125个管脚,而一片16位的DDR存储器就要使用40多个FPGA管脚,所以在不是特别必要的情况下,就没有在PL侧设计独立DDR3存储器。

对于学习者,当大家当学习我们ACX720的DDR3部分的课程时候,就无法在ACZ702开发板上进行实验,因为你找不到DDR3存储器对应对管脚约束信息(因为就没设计DDR3存储器)。

对于开发者,当希望PL部分也能够使用大容量的DDR3存储器时,可以直接参考我们提供的基于HDL的逻辑设计案例中的摄像头相关的案例源码。这些案例我们就是使用PL来读写PS侧底DDR3存储器,从而实现大容量数据高速缓存的。我们设计了专门的图像写入和图像读出逻辑,以AXI4总线读写PS提供的HP端口,从而访问PS的DDR3。

这种架构还有一个巨大的优势,就是PL通过HP端口写入到PS侧DDR3中的数据,不仅PL可以再读回来,同时PS侧的ARM CPU也可以读写这些数据。

相同的道理,PS侧在某些区域写入的数据,PL侧也可以从该区域读出来使用。

关于该DDR3双端口读写控制器的详细介绍可参考该帖:

【ZYNQ逻辑】AXI接口转换模块设计-CSDN博客![]() https://blog.csdn.net/zgmxs/article/details/138669360

https://blog.csdn.net/zgmxs/article/details/138669360

8772

8772

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?