本文由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。

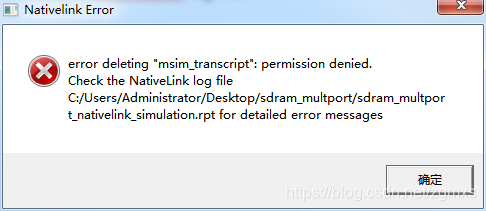

问题现象

Error deleting “msim_transcript”:permissiondenied.

Check the NativeLink log file

问题原因

同一工程Modelsim窗口多开。

解决方法

关闭正在运行的modelsim软件,再启动仿真。

本文由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。

问题现象

Error deleting “msim_transcript”:permissiondenied.

Check the NativeLink log file

问题原因

同一工程Modelsim窗口多开。

解决方法

关闭正在运行的modelsim软件,再启动仿真。

1万+

1万+

1355

1355

3481

3481

5401

5401

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?