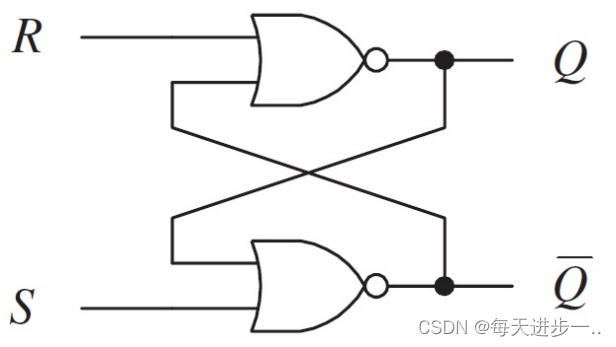

The SR flip flop is a one-bit memory device with 2 inputs. The S (set) input causes the output Q to be set to 1. The R (reset) input causes the output Q to be 0. S=1 and R =1 is invalid. The SR flip-flop can be constructed with 2 NOR gates or 2 AND gates.

SR flip-flop with 2 NOR gates

| S |

R |

Q |

Q' |

| Initial -> Final |

Initial -> final |

||

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4767

4767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?