目录

一、数的表示及乘法的范围

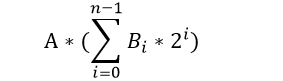

对于n比特数B,其二进制数转换为有符号十进制整数的公式如下:

当B>=0,B的第n-1比特为0,则B可用下式表示:

设n=4,“5”的二进制位为0101,则5 = 1*4 + 1*1。

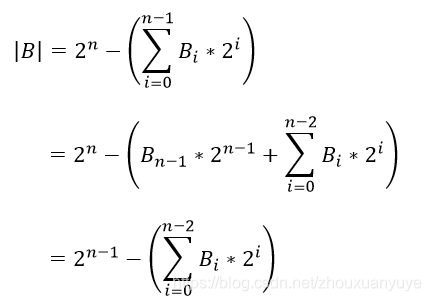

当B<0时,B的第n-1比特为1,B已为补码表示。

所以-|B|表示如下:

综上所述,有符号数与无符号与十进制的转换表示可统一为如下格式:

对于正数或0,Bn-1=0;对于负数,Bn-1=1;与上述结果一致。

对于n比特无符号数:

最小数:

![]()

最大数:

![]()

对于n比特有符号数:

最小数:

![]()

最大数:

![]()

从上式可以看出,n比特乘法,输出位宽2n比特,无论有符号数相乘还是无符号数相乘均不会产生溢出。

二、乘法竖式计算

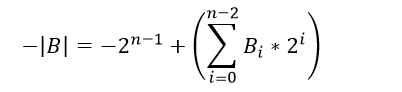

我们先来做一道小学数学题,A=5,B=12,求A*B的结果;

相信你很快就列出了乘法竖式并得出5*12=60的结果。让我们看下计算机如何计算?

5的二进制位为(0101),12的二进制位(1100),按照二进制我们列出其竖式如下:

将结果(111100)转化为10进制,结果依然为60,以上是无符号数竖式计算,有符号数乘法二进制竖式计算请参考以下思考题。

思考题:A=-5,B=12,求A*B的结果,请列出其二进制竖式。

三、乘累加乘法器

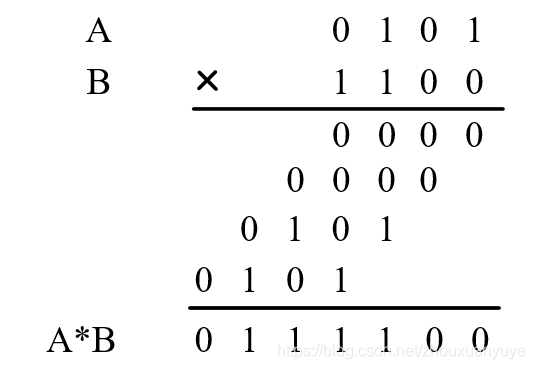

乘法器的本质为加法器的累加和。乘累加乘法器,通过乘->移位->累加的方式,通过多次加法求和的方式计算结果。从上述竖式可以看出,B的每一位比特与A相乘后进行移位,最后按列相加,结果表示如下,其中i为比特序号,n为位宽:

其展开的结构如下:

以上结构使用了n-1个n比特加法器,将耗费大量的资源;所以有使用如下串行结构的乘法器。

该串行结构乘法器使用一个加法器,由控制逻辑和输入数寄存器A,B组成,此种结构多种多样,基本原理均在于移位加。一个16位乘法器,n=16,乘累加次数为16,由Sum作为中间数暂存,Bi作为控制A是否被加入到Sum中,且每次A向左移位1比特,A*B输出比特位宽32。

串行乘法器时间延迟大,但面积消耗小。

在Verilog设计中,直接使用“*”即可以,用好signed和unsigned关键字。

或者根据上述原理,也可以设计自己的“*”符号。

下期预告:阵列乘法器

欢迎批评指正,更多阅读,关注“纸上谈芯”,不定期更新,共同学习:

1023

1023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?