目录

减法器可由基础的半减器和全减器模块组成,或者基于加法器和控制信号搭建。

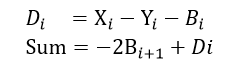

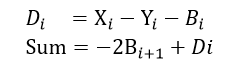

定义N比特被减数X,减数Y,差为D(difference);

来自低比特借位Bi,向高比特借位Bi+1,i为比特序号;

所以,有以下结论:

一、半减器

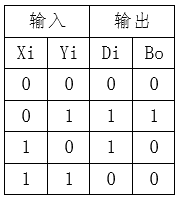

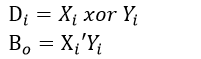

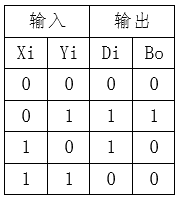

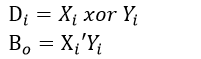

半减器用于计算两比特Xi和Yi的减法,输出结果Di和向高位的借位Bo(Borrow output)。其真值表、逻辑表达式、Verilog描述和门电路图如下:

真值表

逻辑表达式

xor表示异或。

Verilog设计

目录

减法器可由基础的半减器和全减器模块组成,或者基于加法器和控制信号搭建。

定义N比特被减数X,减数Y,差为D(difference);

来自低比特借位Bi,向高比特借位Bi+1,i为比特序号;

所以,有以下结论:

半减器用于计算两比特Xi和Yi的减法,输出结果Di和向高位的借位Bo(Borrow output)。其真值表、逻辑表达式、Verilog描述和门电路图如下:

真值表

逻辑表达式

xor表示异或。

Verilog设计

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?