一 名词解释: DLL, AMBA ,STA,CRC(还有几个记不清了,因为别的不知道)

DLL:延时锁相环

AMBA:高速微控置总线,

STA: 静态时序分析

CRC: 循环冗余校验

二 数字前端设计的基本流程以及主要工具:

前端设计的流程及使用的EDA工具如下:

1、架构的设计与验证:按照要求,对整体的设计划分模块。

架构模型的仿真可以使用Synopsys公司的CoCentric软件,它是基于System C的仿真工具。

2、HDL设计输入:设计输入方法有:HDL语言(Verilog或VHDL)输入、电路图输入、状态转移图输入。

使用的工具有:Active-HDL,而RTL分析检查工具有Synopsys的LEDA。

3、前仿真工具(功能仿真):初步验证设计是否满足规格要求。

使用的工具有:Synopsys的VCS,Mentor的ModelSim,Cadence的Verilog-XL,Cadence的NC-Verilog。

4、逻辑综合:将HDL语言转换成门级网表Netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准;逻辑综合需要指定基于的库,使用不同的综合库,在时序和面积上会有差异。逻辑综合之前的仿真为前仿真,之后的仿真为后仿真。

使用的工具有:Synopsys的Design Compiler,Cadence的 PKS,Synplicity的Synplify等。

5、静态时序分析工具(STA):在时序上,检查电路的建立时间(Setuptime)和保持时间(Hold time)是否有违例(Violation)。

使用的工具有:Synopsys的Prime Time。

6、形式验证工具:在功能上,对综合后的网表进行验证。常用的就是等价性检查(Equivalence Check)方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。

使用的工具有:Synopsys的Formality

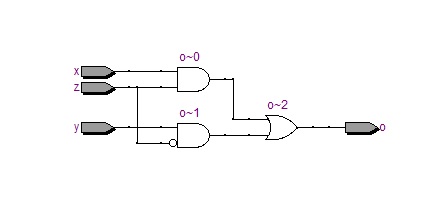

三,画出xz+y(~z)的cmos图,我似乎也没有做正确。

还要把这个图转换成cmos的实现。

四,静态时序分析与动态时序分析的区别和联系:

动态时序验证是在验证功能的同时验证时序,需要输入向量作为激励。随着规模增大,所需要的向量数量以指数增长,验证所需时间占到整个设计周期的50,且这种方法难以保证足够的覆盖率,因而对片上系统芯片设计已成为设计流程的瓶颈,所以必须有更有效的时序验证技术取代之。

动态时序仿真的优点是比较精确,而且同静态时序相比较,它适用于更多的设计类型。 但是它也存在着比较明显的缺点: 首先是分析的速度比较慢;

其次是它需要使用输入矢量,这使得它在分析的过程中有可能会遗漏一些关键路径(critical paths),因为输入矢量未必是对所有相关的路径都敏感的。

静态时序分析技术是一种穷尽分析方法,用以衡量电路性能。它提取整个电路的所有时序路径,通过计算信号沿在路径上的延迟传播找出违背时序约束的错误,主要是检查建立时间和保持时间是否满足要求,而它们又分别通过对最大路径延迟和最小路径延迟的分析得到。静态时序分析的方法不依赖于激励,且可以穷尽所有路径,运行速度很快,占用内存很少。它完全克服了动态时序验证的缺陷,适合进行超大规模的片上系统电路的验证,可以节省多达20的设计时间。因此,静态时序分析器在功能和性能上满足了全片分析的目的。

五,建立时间和保持时间的概念。(这个很基础)它们与时钟频率以及输入电压的关系(这个不懂!!希望高手指点)

具体问题,如果建立(保持)时间发生违规,提高和较低频率有什么作用?提高降低输入电压有什么作用?

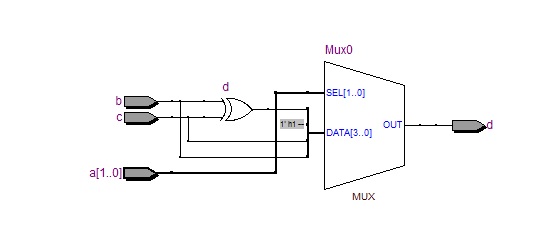

六,给出Verilog代码要求只用与、非、或门实现功能:(a是双输入的)

case(a) begin

2'd0: d<=b;

2'd1:d<=c;

2'd2:d<=1'b1;

2'd3: d<=b^c;

end

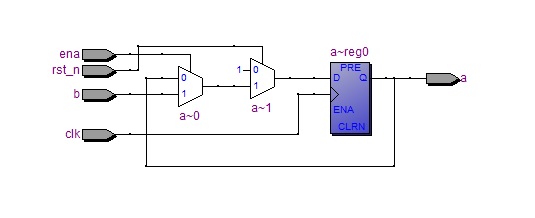

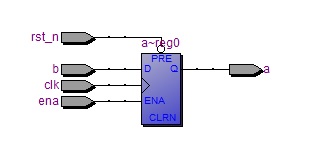

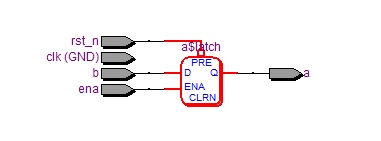

七:也是Verilog代码:主要考察同步复位,异步复位的实现,也要求只用与、非、或门和寄存器实现。

always @(posedge clk or negedge rst_n)

if(!rst_n) a<=1'b0;

else if(ena)

a<=b;

always @(posedge clk )

if(!rst_n) a<=1'b0;

else if(ena)

a<=b;

always @(ena or b or rst_n)

if(!rst_n) a<=1'b0;

else if(ena)

a<=b;

module test(clk,rst_n,x,y,z);

input clk,rst_n;

input[15:0] x,y;

output reg [31:0] z;

reg [31:0]z_r;

reg [2:0] num;

reg [7:0] r1,r2;

reg [15:0] temp;

//output z=x*y

always @ (posedge clk or negedge rst_n)

if(!rst_n) begin

num<=3'd0;

z<=32'd0;

end

else begin

num<=num+1'b1;

if(num==3'd5) begin

z<={temp[15:0],16'd0}+z_r;

num<=3'd0;

end

case(num)

3'd0:begin

r1<=x[7:0];

r2<=y[7:0];

end

3'd1:begin

temp<=r1*r2;

r2<=y[15:8];

end

3'd2:begin

z_r<=temp;

temp<=r1*r2;

r2<=y[7:0];

end

3'd3:begin

z_r<={16'd0,temp[15:0]}+z_r;

temp<=r1*r2;

r1<=x[15:8];

end

3'd4:begin

z_r<={16'd0,temp[15:0]}+z_r;

temp<=r1*r2;

end

endcase

end

endmodule

题目整体上不是特别难,但是好久不接触有些生疏了,希望造福下一届!!

990

990

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?