这几天在搞VIVADO开发环境下的PCIE学习,一点心得小结。

1、首先建立对应的PCIE工程,流程都差不多,进行相应的IP核配置后就可以生成工程。网上有很多资料可参考,在此不赘述;

详细可参考:

https://blog.csdn.net/wordwarwordwar/article/details/72590295?locationNum=7&fps=1

本人选择的是Standard Bus Interface下的PCI Express-7 Series Integrated Block,如图1;

2、生成PIO example;

如图2所示,右击生成的(IP核名)pcie_7x_0(pcie_7x_0.xcl) IP核,选择图中标记的“Open IP Example Design”即可生成并在一个新窗口中打开对应的example工程。

3、仿真;

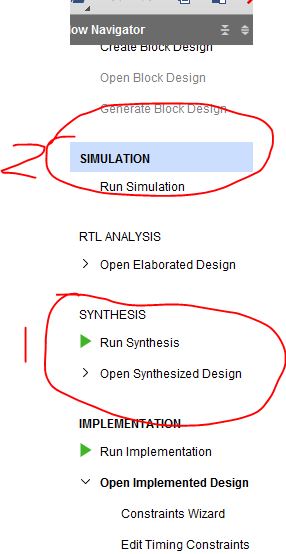

1)先进行综合,点击项目管理中的Run Synthesis,如图3中的1。Vivado中是生成的项目同时生成自带仿真的,这点比ISE方便多了。

2)综合完后进入仿真,如图4所示。标记1,打开Simulation Sources文件夹,选中board,然后选择2中的Run Simulation运行,即可进行仿真。

3)添加想要观察的信号。Vivado进入仿真在波形窗口中会显示部分默认信号波形,我们需要额外添加想要观察的信号。在《VIVADO 入门之仿真与逻辑分析仪使用》http://www.cnblogs.com/mouou/p/6413133.html文章中提供了一种添加信号的方法。

该文通过添加断点运行后添加更多观测信号,具体见文中9.7.3行为级仿真中Step6:断点观察更多信号及后续的仿真步骤。

本人感觉这种方法稍有欠佳,经过摸索发现,在simulation中包含source和scope两个栏,点开scope栏可以发现和modelsim中的仿真工作栏组织架构基本一致,包含仿真源文件的库和glbl库。如图5,点开scope中board目录,可以看到各模块列表,任意点击选择一模块(如PIO_RX_ENGINE),可以发现在右边的Objects中就会出现该模块中的所有可添加到仿真波形观察窗中的信号,右击要观察的信号选择第一个操作选项“Add to Wave Window”添加到观测窗中。

选择添加好全部要观察信号后,点击图6中三角形即可运行仿真,同时可以设置仿真运行时间,如10ms。

4)仿真结果。根据vivado上的仿真显示时间大概64us(实际可能5分钟左右)左右的时候lnk_up信号跳变为1。如图7所示。但是本人有些疑惑还未解决。

软件生成的PIO example只需对时钟和复位的信号引脚进行约束修改就可以烧录到开发板上运行的。

本人只关注于当前项目,可能不全面,欢迎交流。

Vivado2017.4中PCIE仿真学习

最新推荐文章于 2024-04-29 08:02:01 发布

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?