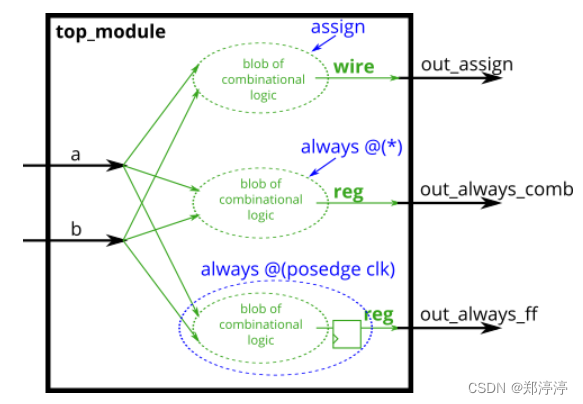

Verilog 中有三种类型的作业:

- 连续赋值(赋值 x = y;)。仅当不在过程内部时使用(“始终阻止”)。

- 过程阻塞分配:(x = y;)。只能在过程中使用。

- 过程非阻塞赋值:(x <= y;)。只能在过程中使用。

在组合始终块中,使用块分配。在“计时始终”块中,使用非阻塞分配。

练习:用以下三种方式构建XOR门

// synthesis verilog_input_version verilog_2001

module top_module(

input clk,

input a,

input b,

output wire out_assign,

output reg out_always_comb,

output reg out_always_ff );

assign out_assign = a^b; //assgin组合逻辑 = 阻塞赋值

always@(*)

begin

out_always_comb = a ^ b; //always组合逻辑 = 阻塞赋值

end

always@(posedge clk)

begin

out_always_ff <= a ^ b; //always时序逻辑 <= 非阻塞赋值

end

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?