笔记重点:

1、双边沿触发的触发器(重要内容)。

2、为什么我的方法会出现毛刺。

3、竞争冒险现象。

题目:

构建一个在功能上表现得像双边沿触发触发器的电路:在时钟的两个边沿触发。但是,FPGA没有双边触发触发器,并且@(posedge clk或negedge clk)始终不被接受为合法的敏感度列表。

方法一:

分析过程:

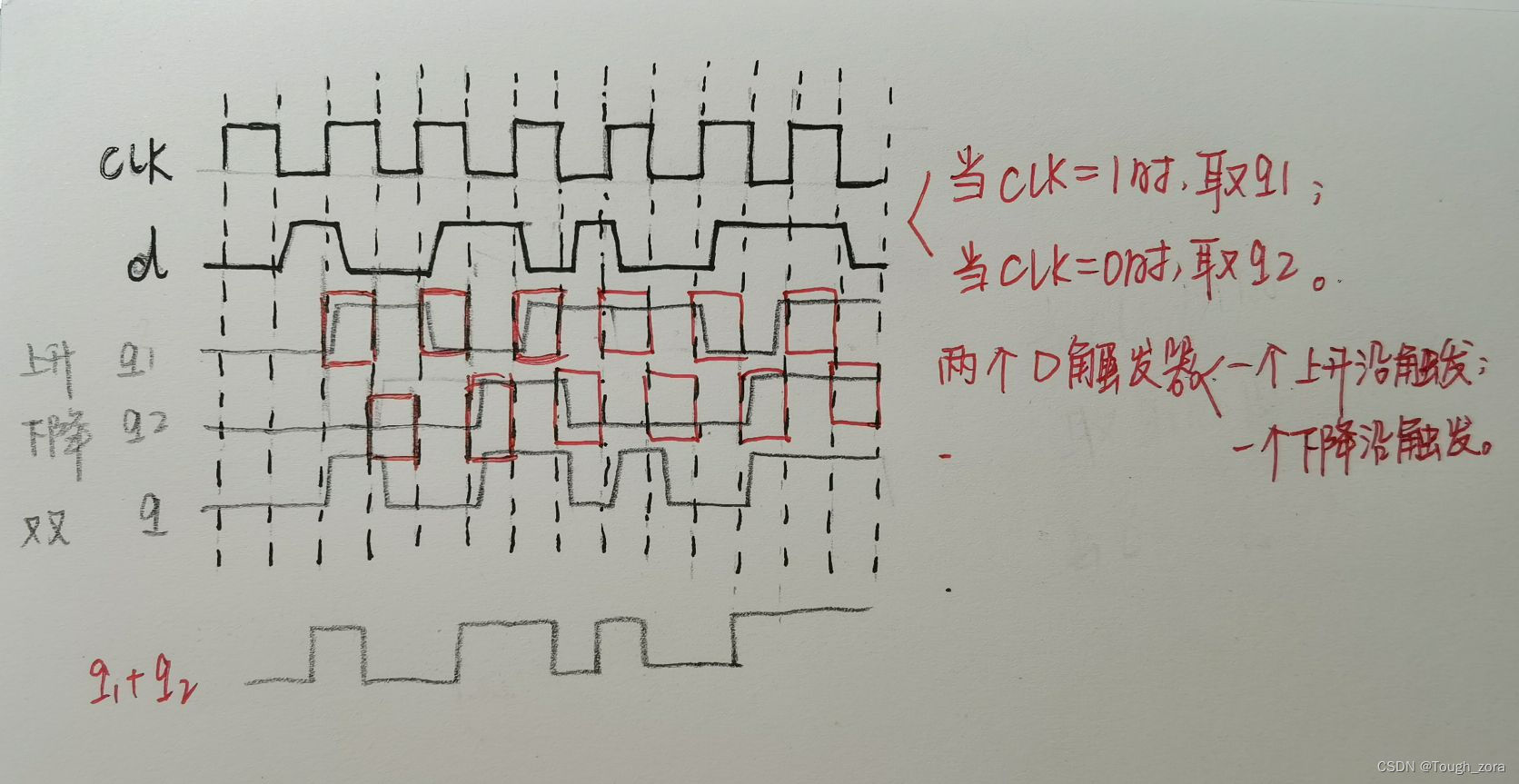

- 分析上升沿触发波形图、下降沿触发的波形图;

- 观察上述情况与双边触发的波形图的关系。

- 构建电路图,写代码。

module top_module (

input clk,

input d,

output q

);

wire q1,q2;

always@(posedge clk)begin

q1 <= d;

end

always@(negedge clk)begin

q2 <= d;

end

assign q = (clk==1'b1)?q1:q2;

endmodule方法二:

module top_module (

input clk,

input d,

output q

);

reg q_d1;

reg q_d2;

always@(posedge clk)begin

q_d1 <= d ^ q_d2;

end

always@(negedge clk)begin

q_d2 <= d ^ q_d1;

end

assign q = q_d1 ^ q_d2;

endmodule

对于双沿检测,一定不能使用always@(posedge clk or negedge clk)begin这种方式,这种方式是不可综合的,应该用图中的方法二。对于第一种方法,虽然这道题是正确的,但是有博主测试过在modelsim和vivado中仿真会产生毛刺,不建议使用。

1.为什么方法二可以呢?

首先,在上升沿的时候,q_d1变成了d ^ q_d2,那么q = q_d1 ^ q_d2 = d ^ q_d2 ^ q_d2 = d;

接着,在下降沿的时候,q_d2变成了d ^ q_d1,那么q = q_d1 ^ q_d2 = q_d1 ^ d ^ q_d1 = d;

在每个正负沿,q_d1和q_d2交替出现,因此q总会输出最新的值。

2.毛刺产生的原因:(来自其他博主和评论)

wangkai_2019:

大家可以想象,在上升沿和下降沿采到d信号以后,q_d1和q_d2会立即变化,同时时钟也会立即变化,时钟和q_d1、q_d2的变化的延迟是不一致的,这就导致了毛刺的出现,这时候的时钟相当于是一个组合逻辑了,由于路径延时的不同,导致组合逻辑到达的时间存在差异,从而会产生毛刺,如下图所示。

为什么方法一不会产生毛刺呢?大家看看代码,方法一的结果是两个寄存器直接异或,没有涉及到时钟信号,方法二的结果需要时钟信号进行判断,而时钟信号时钟的上升沿和下降沿又是触发器的输出,即q_d1、q_d2,因此会产生毛刺。

岁往长鲸:我的理解是在由于采用clk信号作为sel信号,因此clk信号必定比q_d1/1_d2信号先到达MUX,因为q_d1/1_d2信号还需要经过一级寄存器才能到达,因此如果在上一个周期采到1,这个周期采到0的话,由于clk信号先到达,误以为q_d1/1_d2信号仍为1,因此输出1,在经过一个极短的Tpd后,0信号到达,因此MUX又输出了0信号,导致了一个tpd时间的1信号(也就是毛刺)的出现,简单点讲就是q_d1/1_d2信号未满足建立时间,产生了竞争冒险,不知我这样理解对不对?

3.竞争冒险现象

- 竞争:当信号通过导线和门电路时,将产生时间延迟。因此,同一个门的一组输入信号,由于它们在此前通过不同数目的门,经过不同长度导线的传输,到达门输入端的时间会有先有后,这种现象称为竞争。竞争可以分为两类。

a. 同一个输入信号,经过不同路径到达输入端,产生竞争。

b. 多个信号同时变化,因为多个输入信号同时变化的瞬间或路径导致到达输入端时间不一致,产生竞争。

- 冒险:逻辑门因输入端的竞争而导致输出产生不应有的尖峰干扰脉冲的现象,称为冒险。

409

409

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?