一、背景

在进行时序分析时,工具默认对所有的时序路径进行分析,在实际的设计中,存在一些路径不属于逻辑功能的,或者不需要进行时序分析的路径,使用set_false_path对该路径进行约束,时序分析时工具将会直接忽略路径不进行分析。

1.1 设置false path的场景

可以设置为false path的路径包括

a)跨时钟域中添加的进行两次同步的逻辑单元

b) 只在FPGA通电启动时的寄存器

c)复位或测试的逻辑模块

d)异步的分布式RAM中读时钟和写时钟之间的路径

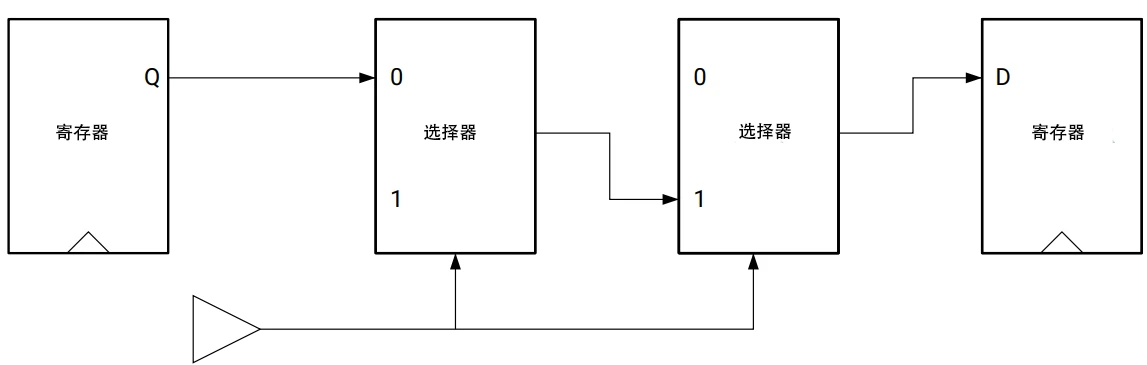

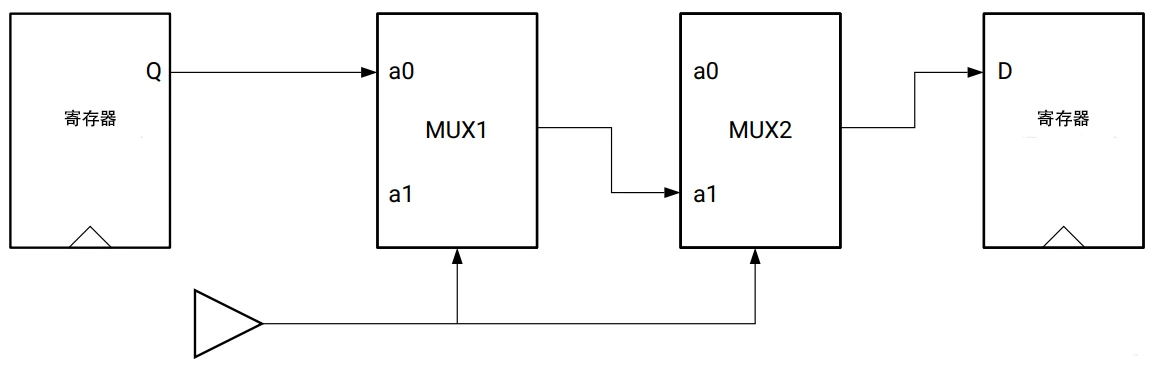

下面,展示一个对于上面提到的非功能单元的路径,在两个触发器中级联了两个选择器,选择器的选项信号相同。

1.2 set_false_path的优势

a)减少运行时间:将一些路径设置为false path后,时序分析工具无需耗费时间对该路径进行分析,也不需要对非功能模块路径进行优化,可以节省时间

b)提高QOR(quality of results):将路径设置为false path可以极大地提高QOR,综合,布局后的质量,优化设计也会极大地受工具尝试解决的时序问题影响。

因为如果非功能模块的路径存在时序违例时,工具可能尝试去修复这些违例,这不仅会导致设计因为逻辑复制而变大,也可能因为非功能模块有更大的违例而忽略了实际功能模块的违例问题。只有正确的设置约束才能获取最好的结果。

二、set_false_path

2.1 设置说明

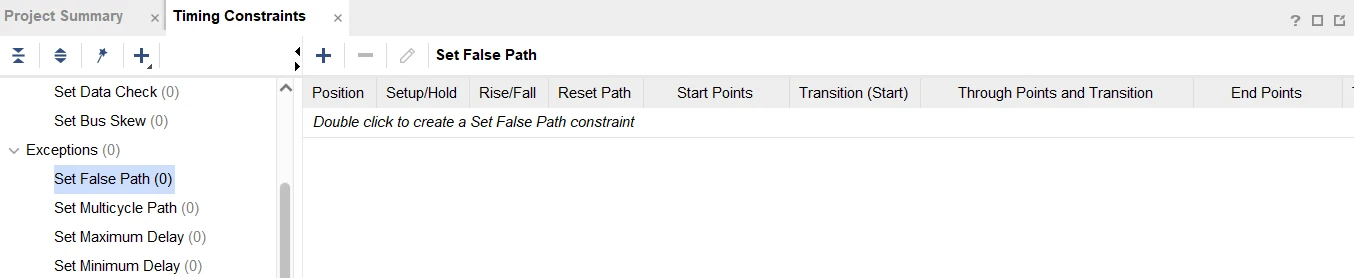

进入Timing Constraints,选择Exceptions中Set False Path

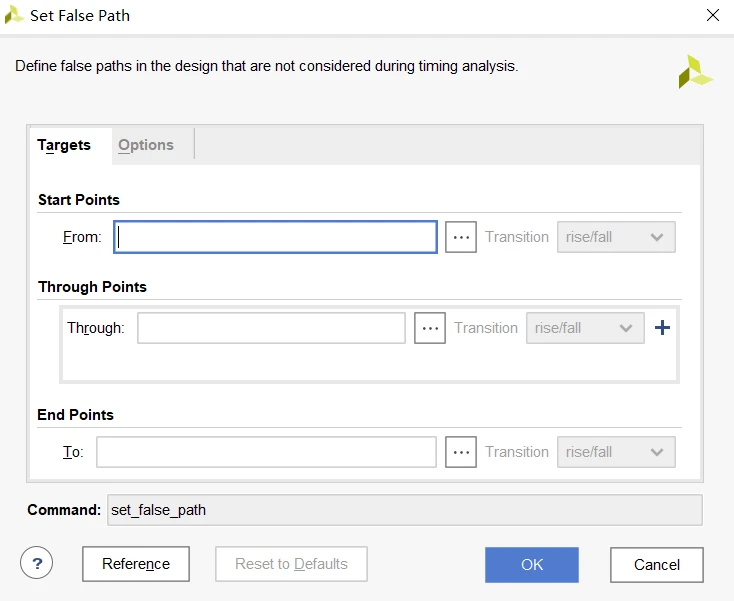

Set False Path设置界面如下

Start Point:设置false path的起点,可以为Cell pins,clocks,cells,I/O ports;

Through Points:设置false path经过的中间路径,可以为Nets,cells,cell pins;

End Points:设置false path的终点,可以为Cell pins,clocks,cells,I/O ports;

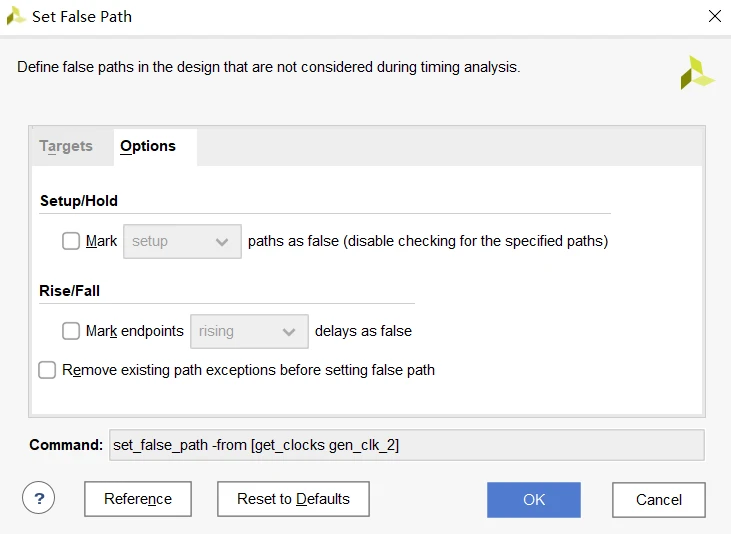

Setup/Hold:设置False path的路径的分析类型为Setup 或hold,不勾选时,两者都会为False Path

Rise/Fall:设置False path的路径中生效的边沿,不勾选时,不会进行边沿区分

Remove existing path exceptions before setting false path:勾选后,如果设置的路径上已存在其他exceptions约束,则会将其覆盖,不勾选则保留原有的约束。

备注:当使用through时没有设置-from和-to参数时需注意,所有经过through设置的线路都会被视为false path。

2.2 细节区分

a)多个-through时,顺序不同结果不同,下面两条约束不是等价的,第一条表示先通过cell1/pin1,再通过cell2/pin2的路径,第二条约束则相反

set_false_path -through cell1/pin1 -through cell2/pin2

set_false_path -through cell2/pin2 -through cell1/pin1b)get_cells连接多个单元时,表示从复位端口reset到多个cells(ff1_reg,ff2_reg,ff3_reg)中的路径都将设为false path

set_false_path -from [get_ports reset] -to [get_cells {ff1_reg ff2_reg ff3_reg}]c)不对两个异步时钟clk1,clk2间的路径进行分析,只会将从clk1到clk2间的路径设置为false path

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]d)如果要对clk1到clk2,clk2到clk1的路径都设置为false path,则需要两条约束命令

set_false_path -from [get_clocks clk1] -to [get_clocks clk2]

set_false_path -from [get_clocks clk2] -to [get_clocks clk1]e)当需要对多个异步时钟间都不进行时序分析时,对异步时钟两两间设置false path则太繁琐,此时可使用set_clock_groups代替

set_clock_groups -name clk_group -asynchronous -group [get_clocks clk1] -group [get_clocks clk2] -group [get_clocks clk3]f)在两个寄存器间的非正常逻辑功能路径中,设置false path可以只使用两个through,而不用指定start point和end point

命令中MUX1/a0和MUX2/a1位置不能换,交换后则表示先经过MUX2/a1再经过MUX1/a0

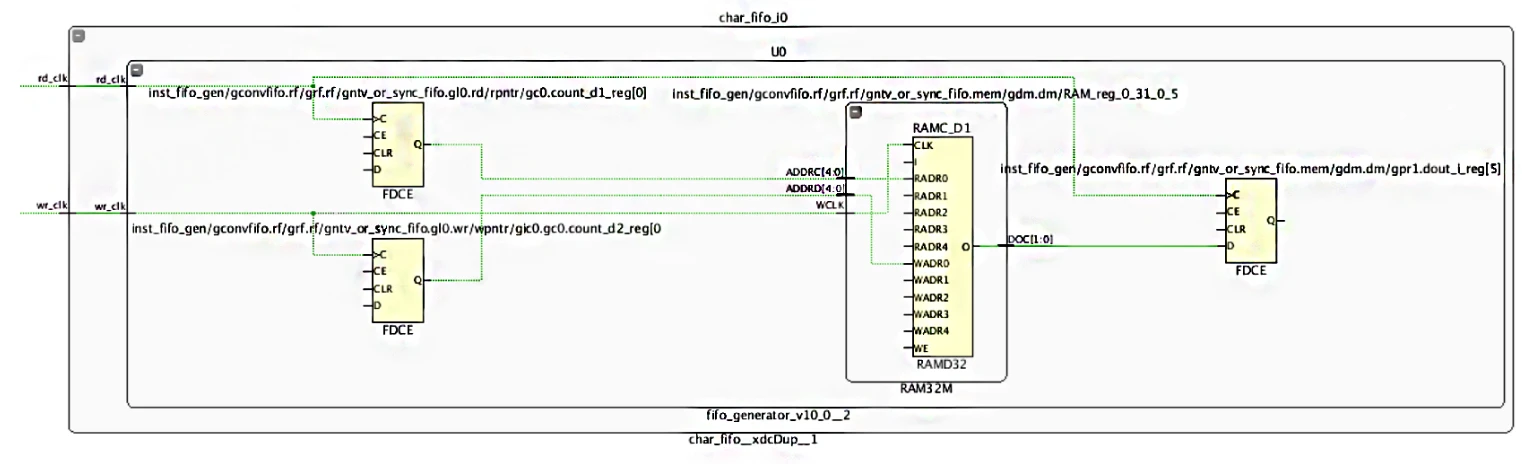

set_false_path -through [get_pins MUX1/a0] -through [get_pins MUX2/a1]f)对于异步双端口分布式RAM,写操作和RAM的时钟是同步的,读操作可以不同步,因此,在写时钟和读时钟间设置false path符合设计需求,rd_clk为读时钟,wr_clk为写时钟,有两种约束方式可以实现

方法一、设置从写寄存器到读寄存器的false path

set_false_path -from [get_cells <write_registers>] -to [get_cells <read_registers>]方法二、设置从写使能端口WE到RAM的路径

set_false_path -from [get_cells -hier -filter {REF_NAME =~ RAM* && IS_SEQUENTIAL && NAME =~ <PATTERN_FOR_DISTRIBUTED_RAMS>}]三、工程示例

工程代码

module timing(clk1,clk2,clk3,clk4,ce,d1,d2,out,ff1_2,ff4 );

input clk1,clk2,clk3,clk4,ce,d1,d2;

output out,ff1_2,ff4;

reg ff1,ff1_2,ff2,ff3,ff4;

wire comb,comb4;

always@(posedge clk1,negedge ce)

begin

if(!ce)

begin

ff1<=0;

ff1_2<=0;

end

else begin

ff1<=d1;

ff1_2<=ff1;

end

end

always@(posedge clk2,negedge ce)

begin

if(!ce)

ff2<=0;

else begin

ff2<=d2;

end

end

assign comb=ff1*ff2;

always@(posedge clk3,negedge ce)

begin

if(!ce)

ff3<=0;

else begin

ff3<=comb;

end

end

assign out=ff3;

assign comb4=ff1_2*out;

always@(posedge clk4,negedge ce)

begin

if(!ce)

ff4<=0;

else begin

ff4<=comb4;

end

end

endmodule主时钟和生成时钟约束

create_clock -period 10.000 -name create_clk1 -waveform {0.000 5.000} [get_ports clk1]

create_generated_clock -name gen_clk_2 -source [get_pins ff1_reg/C] -divide_by 4 -add -master_clock create_clk1 [get_pins ff2_reg/C]

create_generated_clock -name gen_clk_3 -source [get_pins ff1_reg/C] -multiply_by 4 -add -master_clock create_clk1 [list [get_pins ff2_reg/C] [get_pins ff3_reg/C]]

create_generated_clock -name gen_clk_4 -source [get_pins ff1_reg/C] -edges {1 4 5} -edge_shift {0.000 1.000 0.000} -add -master_clock create_clk1 [get_pins ff4_reg/C]

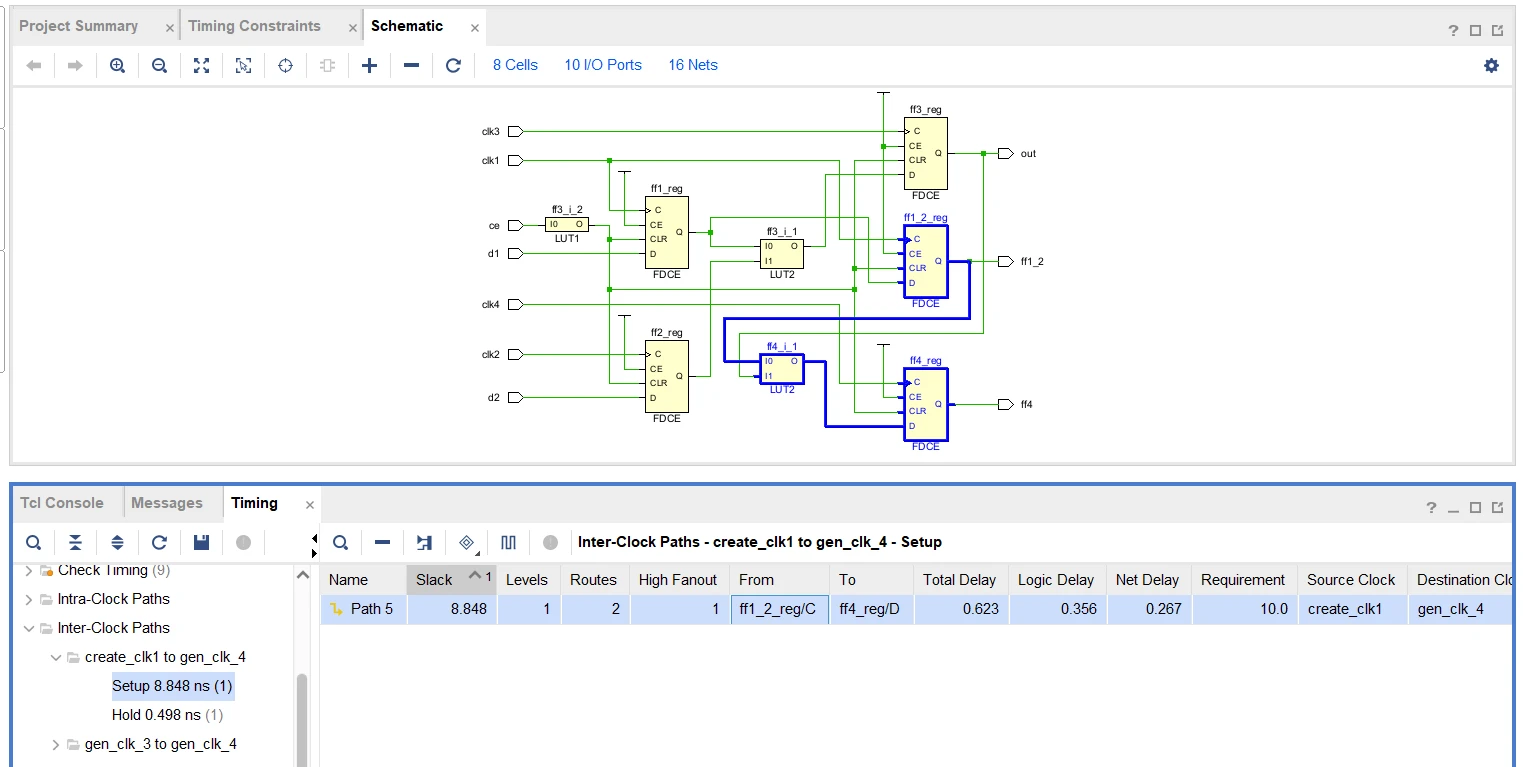

未设置set_false_path时,异步时钟路径create_clk1存在到gen_clk_4的路径,下图蓝色线所示路径

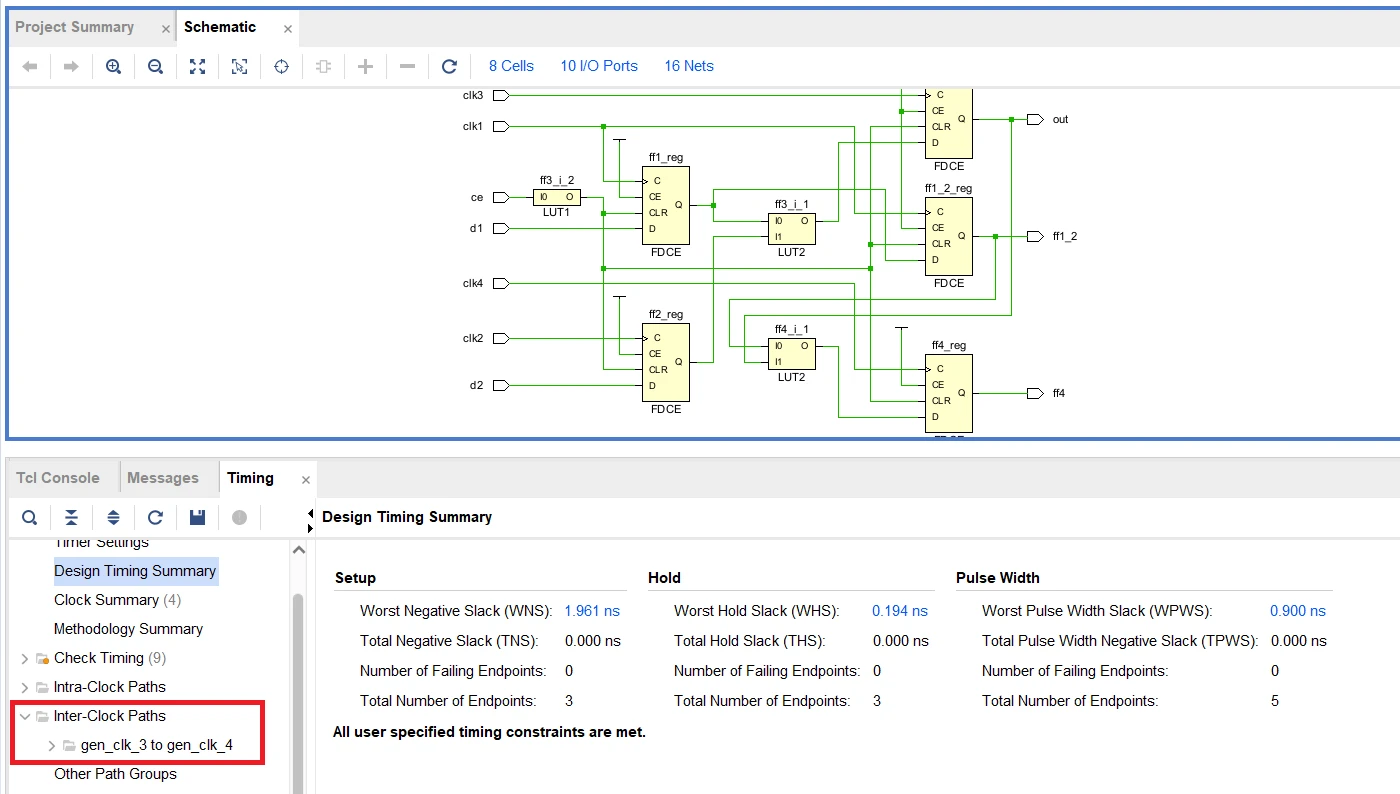

设置create_clk1到gen_clk_4的false path约束,inter-clock paths中只剩gen_clk_3到gen_clk_4的路径,无create_clk1到gen_clk_4的路径

set_false_path -from [get_clocks create_clk1] -to [get_clocks gen_clk_4]

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt

本文详细介绍了如何在Vivado工具中使用set_false_path来约束时序分析,避免对非功能路径进行分析,从而节省时间并提高设计质量。通过设置falsepath,可以排除跨时钟域、启动时寄存器、复位逻辑和异步RAM等场景中的无效路径,提升综合和布局优化效果。

本文详细介绍了如何在Vivado工具中使用set_false_path来约束时序分析,避免对非功能路径进行分析,从而节省时间并提高设计质量。通过设置falsepath,可以排除跨时钟域、启动时寄存器、复位逻辑和异步RAM等场景中的无效路径,提升综合和布局优化效果。

2454

2454

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?