FPGA 从零开始学习

第一章 工欲善其事必先利其器–各类工具安装

- FPGA开发工具安装

- 软件配置和可能遇到的问题

第二章 系统搭建和硬件编程语言的学习

- FPGA硬件系统搭建

- 设计思想与方法

- VIVADO创建一个完整的工程流程

- 硬件编程语言的学习

- Verilog基础知识

硬件编程语言学习--Verilog基础知识

前言

近期工作比较忙,学习时间较少,后续还是根据自己学习的进度,定期总结和分享,也是对自己学习过程的一个梳理。

Verilog基础知识

1. Verilog 和 C 的区别

Verilog 是硬件描述语言,在编译下载到 FPGA 之后, FPGA 会生成电路,所以 Verilog 全部是并行处理与运行的;C 语言是软件语言,编译下载到单片机/CPU 之后,还是软件指令,而单片机/CPU 处理软件指令需要取址、译码、执行, 是串行运行的。

在VIVADO里,RTL级分析原理图就可以查看到你的Verilog代码的功能框图,综合后的原理图可以查看到代码利用FPGA资源实现后的框图(包括使用了哪些逻辑资源或者BUFFER等),布局布线后就相当于利用PCB上的实物已经实际实现的情况(包括了管脚分配和线路时延等)。

2. Verilog 基础知识

A. 逻辑电路的4种状态:0(GND,低电平)、1(VCC,高电平)、X(不确定,可高可低)、Z(高阻,悬空状态)

B. 数据类型:总结了一个图,如下

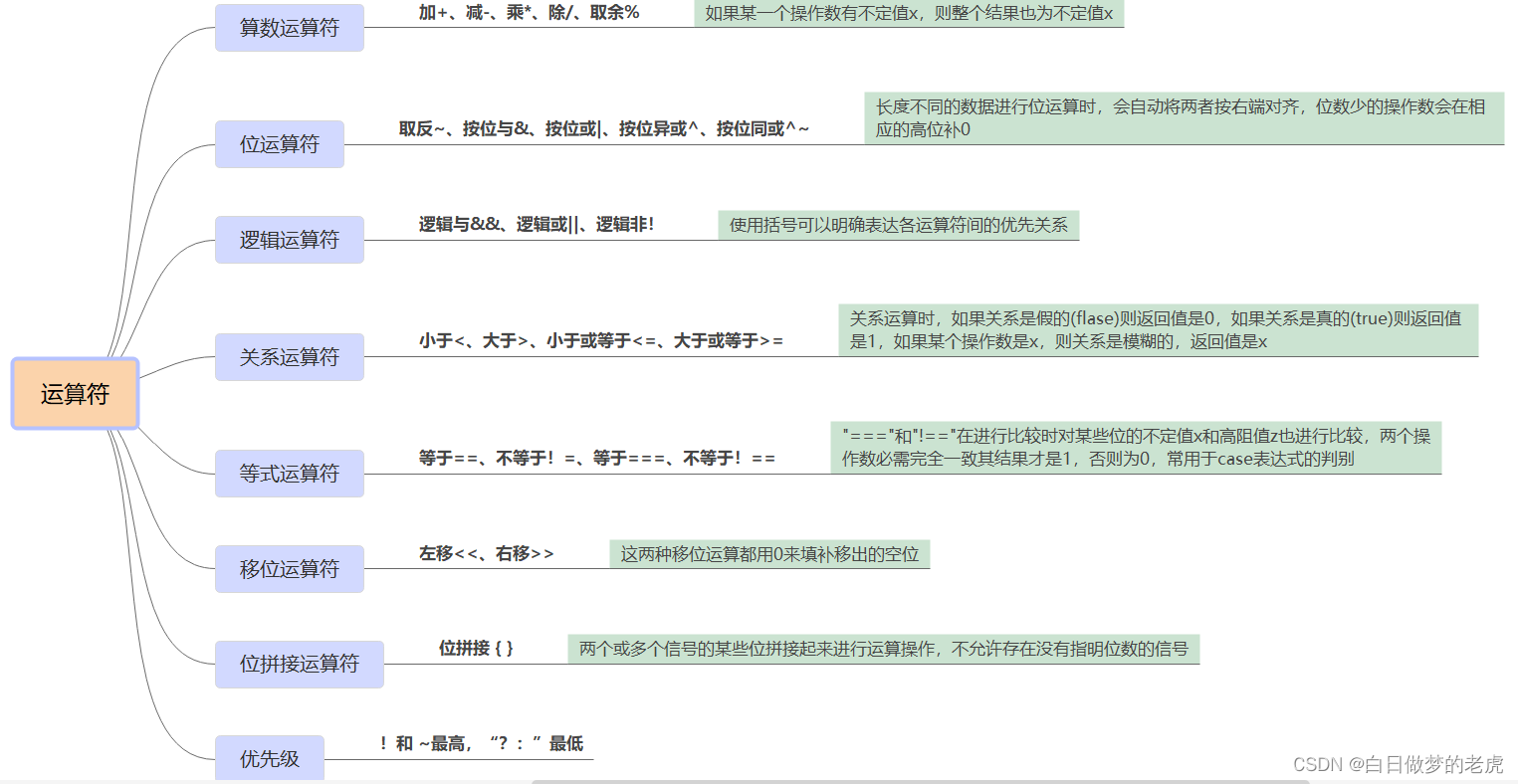

C. 运算符:总结如下图

运算符是有优先级的,可以看下面这个图

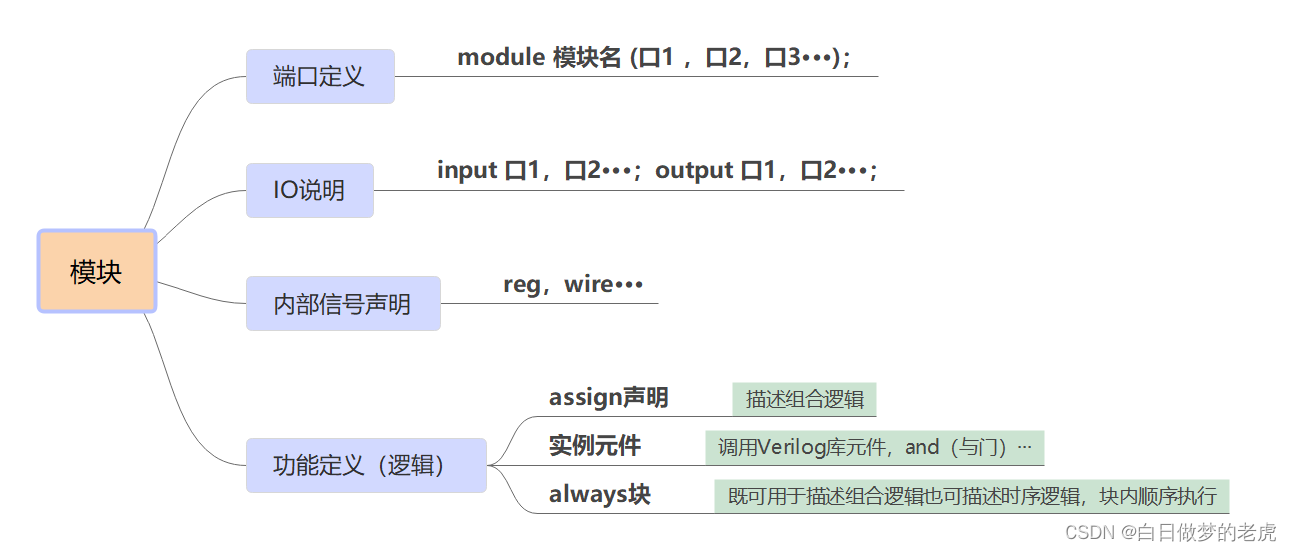

D. 模块代码基本格式(module基本内容)

3. 补充知识点

阻塞赋值(=)与非阻塞赋值(<=)

看名字就比较好理解,同一个always 中,一条阻塞赋值语句如果没有执行结束,那么该语句后面的语句就不能被执行,在always内顺序执行;非阻塞赋值是由时钟节拍决定,在时钟上升到来时,执行赋值语句右边,并行执行,一个时钟沿执行一次。

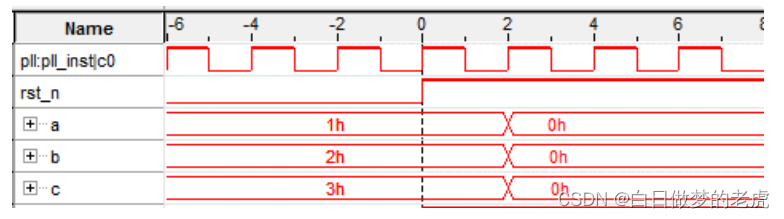

阻塞赋值如上图

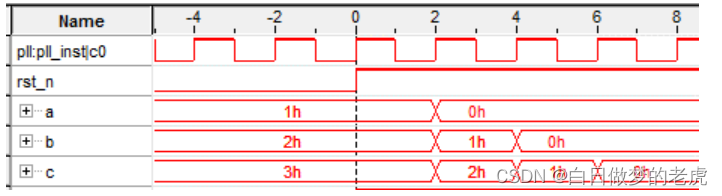

非阻塞赋值如上图

这里自己懒,没截图,借用个别人的图,能直观看出差别,比较简单可以自己测试一下。

总结

这篇主要总结了一些Verilog基础知识,后续就从简单的门电路开始,学习代码实现功能。不积跬步无以至千里,慢慢来积累。

这里安利一下比较好的教材,除了夏宇闻老师的大学教材外,还有正点原子的参考板教材,两者结合起来理解效率比较高。我用的板子是自己设计的,目前是个A7,功能比较简单。所以我的代码学习都是上板验证,后续一些复杂的功能等后面新板卡(K7)设计完成再验证(最近比较忙的原因)。

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?