CC2530学习笔记(3)—— IO端口中断机制

通用I / O中断

配置为输入的通用I / O引脚可用于产生中断。 中断可以配置为在外部信号的上升沿或下降沿触发。 每个P0,P1和P2端口具有端口中断使能位,位于IEN1-IEN2寄存器中的端口内的所有位都是公共的,如下所示:

•IEN1.P0IE:P0中断使能•IEN2.P1IE:P1中断使能

•IEN2.P2IE:P2中断使能

除了这些通用中断使能之外,每个端口内的位还具有独立中断使能位,例如SFR寄存器P0IEN,P1IEN和P2IEN,即使配置为外设I / O或通用输出的I / O引脚在启用时也会产生中断。

当其中一个I / O引脚发生中断情况时,相应的P0-P2中断标志寄存器P0IFG,P1IFG或P2IFG中的中断状态标志被置为1.不管引脚有其中断使能设置。 当一个中断被服务时,通过向该标志写入0来清除中断状态标志。 该标志必须在清除CPU端口中断标志(PxIF)之前清零。

寄存器总结如下:

•P0IEN:P0中断使能

•P1IEN:P1中断使能

•P2IEN:P2中断使能

•PICTL:P0,P1和P2触发边沿配置

•P0IFG:P0中断标志

•P1IFG:P1中断标志

•P2IFG:P2中断标志

通用IO中断寄存器说明

1、端口位中断使能/失能寄存器——PxIEN

2、外设中断使能/失能寄存器——IENx

P0组的中断使能控制在IEN1寄存器的第5位,P1组和P2组的中断使能控制分别在IEN2的第4位和第1位。

IENx寄存器控制整组IO端口中断是使能,PxIEN控制某一组的某一个IO端口的中断使能。

3、中断触发边沿设置寄存器——PICTL

PICTL寄存器的第0位设置触发第0组IO口中断的电平值,第1位设置触发第1组中第0位至第3位中断的电平值,第2位设置第1组中第,4位至第7位中断的电平值,第3位设置触发第2组中第0位至第4位中断的电平值。

4、端口中断状态标志寄存器——PxIFG

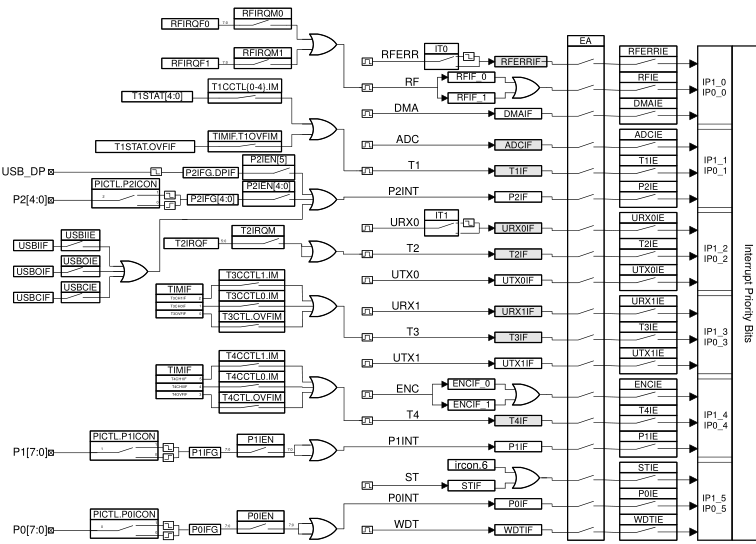

CC2530中断源示意图

431

431

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?