频率相同,相位不同,建议用RAM 或FIFO进行多比特数据同步,没有同步使能的数据垮时钟域处理,使用fifo更简单,不然RAM处理更合理。 频率不同 ,建议选择异步FIFO做时钟域切换。

关于fifo:

同步FIFO:写时钟和读时钟为同一个时钟

异步FIFO:写时钟和读时钟为独立时钟

跨时钟域的数据信号需要用到异步FIFO,隔离时钟域,匹配读写速度

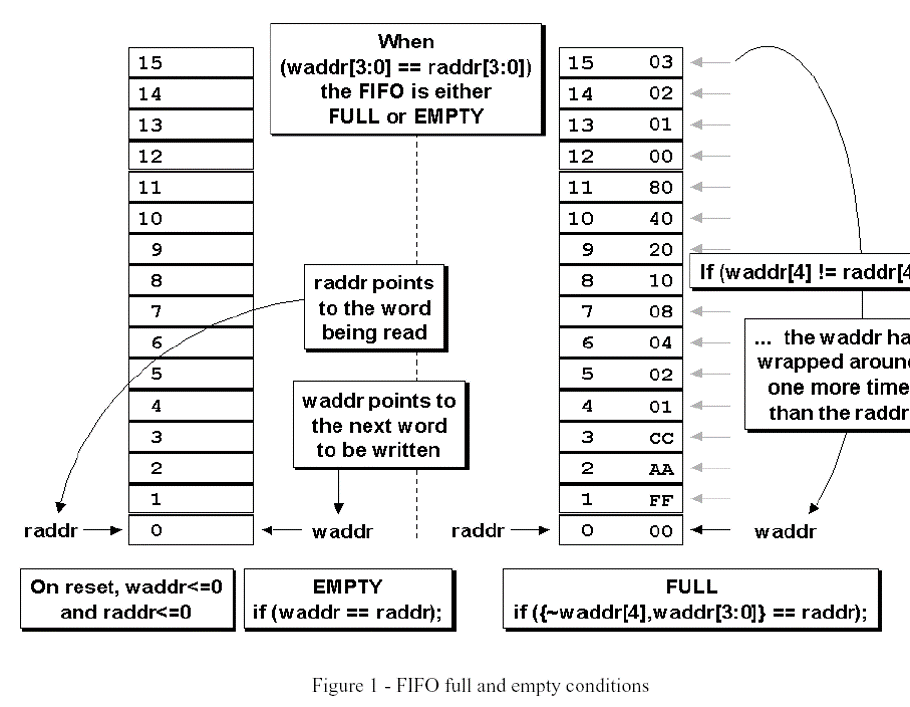

FIFO写满和读空标志的产生:

同步FIFO直接把读写时钟比较或运算产生

异步FIFO由于读写指针不同时钟域,比较前指针必须同步化

由于二进制的指针会出现多位同时跳变,直接由同步器进行同步化会有问题

参考设计: 千兆以太网跨时钟域切换

源时钟是PHY传输给FPGA 的RX_CLK(125M);

目标时钟FPGA内部经过PLL分倍频的125M时钟;

频率相同,相位不同,这里使用RAM进行同步

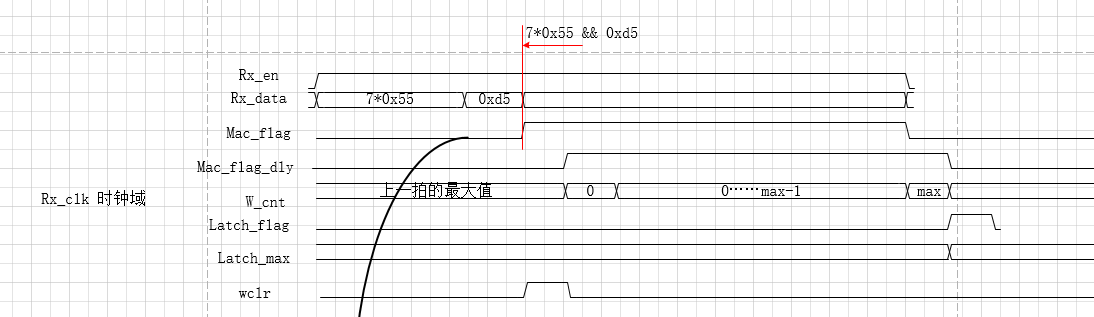

时序:

代码

省略….待完善

898

898

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?