1.ZYNQ启动流程

ZYNQ是一个可扩展处理平台,可以看成一个有FPGA外设的A9核处理器。它的启动流程自然也和传统的ARM处理器类似。

ZYNQ支持从多种设备启动,包括JTAG,NAND,parallel NOR,Serial NOR (Quad-SPI),以及SD卡。通过几个特殊的MIO引脚的状态来确定启动设备。

ZYNQ的启动流程如下:

- 在器件上电运行后,处理器自动开始Stage-0 Boot,也就是执行片内BootROM中的代码。

- BootROM会初始化CPU和一些外设,以便读取下一个启动阶段所需的程序代码。将选定设备的头192Kbyte内容,也就是FSBL(First Stage Bootloader),复制到OCM(On Chip Memory)中,并将控制器交给FSBL。

- FSBL启动时可以使用整块256Kb的OCM,然后初始PS,下载bit文件(也可以以后加载),将动用的SSBL(Second Stage Bootloader),或者裸奔程序,复制到内存中。

- 运行SSBL。

- 运行Uboot,启动Linux。

2.FSBL生成

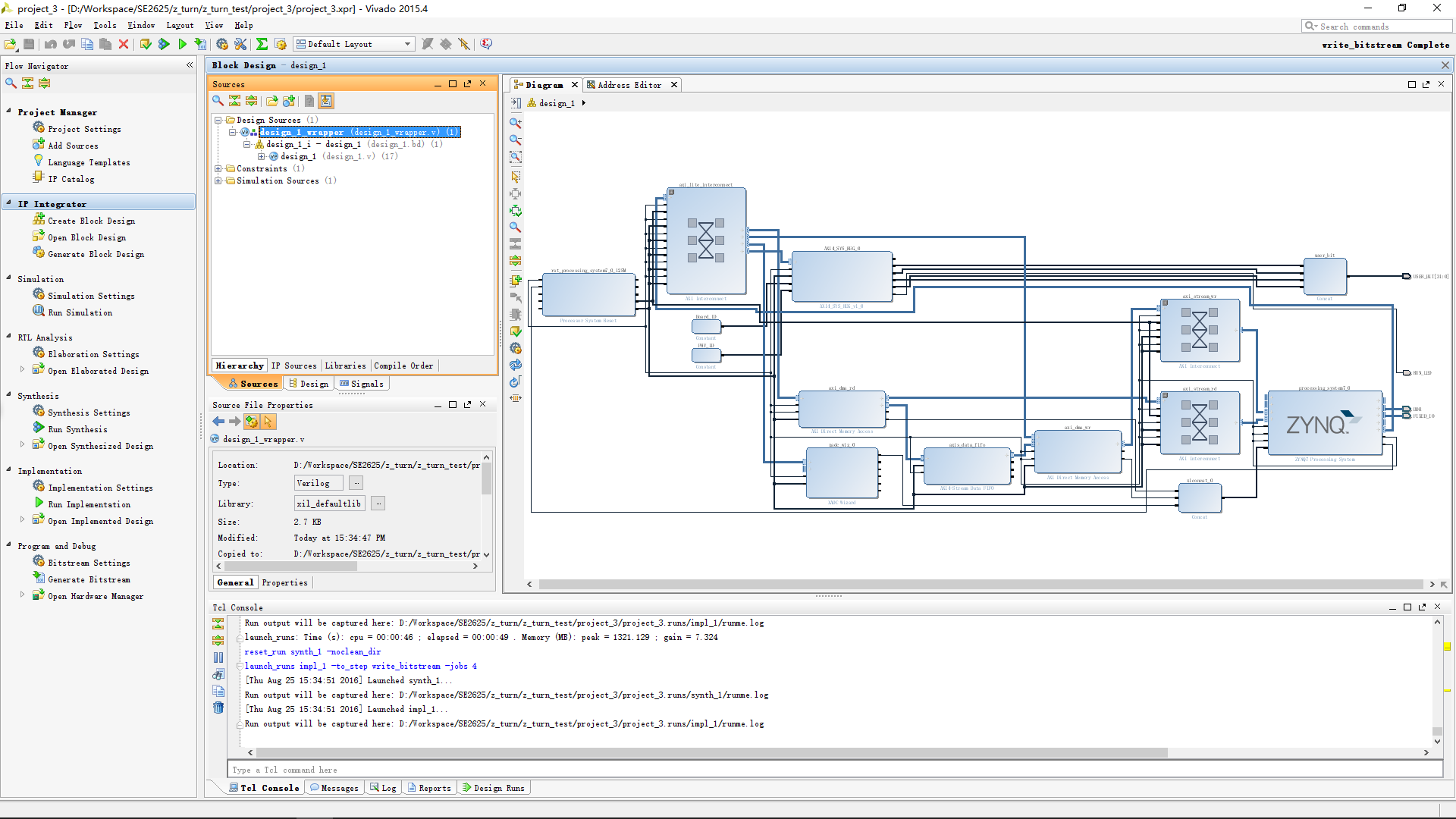

打开一个vivado工程,进行编译和综合,生产bit文件。然后打开Diagram,并在当前界面显示,如图1所示。

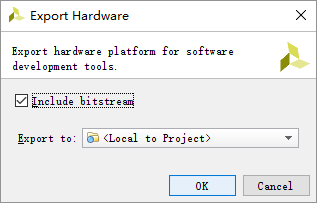

点击File-Export-Export Hardware...。勾选Include bitstream,使用默认路径,点击OK,如图2所示。

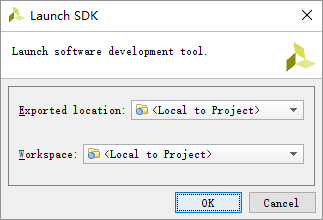

点击File-Launch SDK,使用默认路径,点击点击OK,启动SDK,如图3所示。

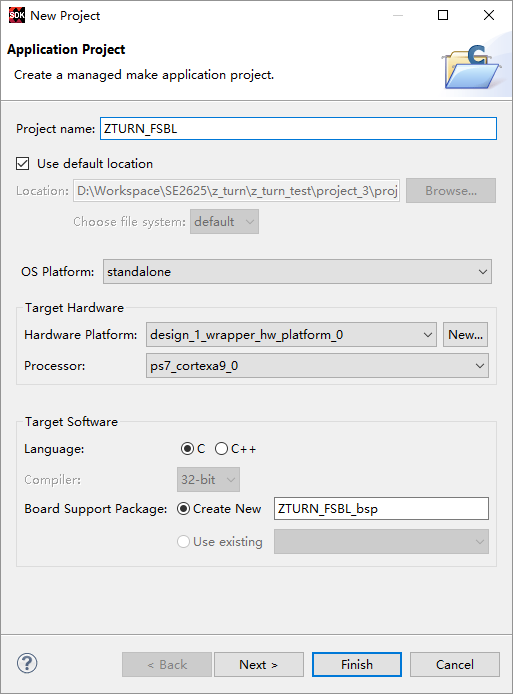

进入SDK后,点击File-New-Application Project,弹出项目新建向导,输入项目名,点击Next,如图4所示。

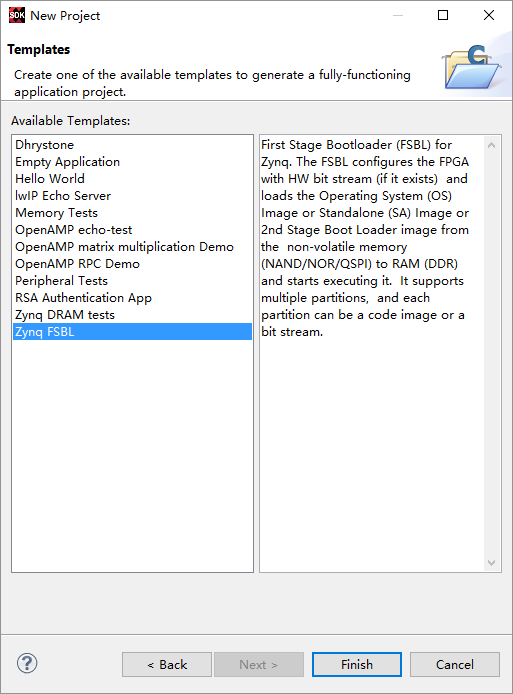

在项目模板中选择Zynq FSBL,点击Finish,如图5所示。然后SDK就会生产对应的项目。

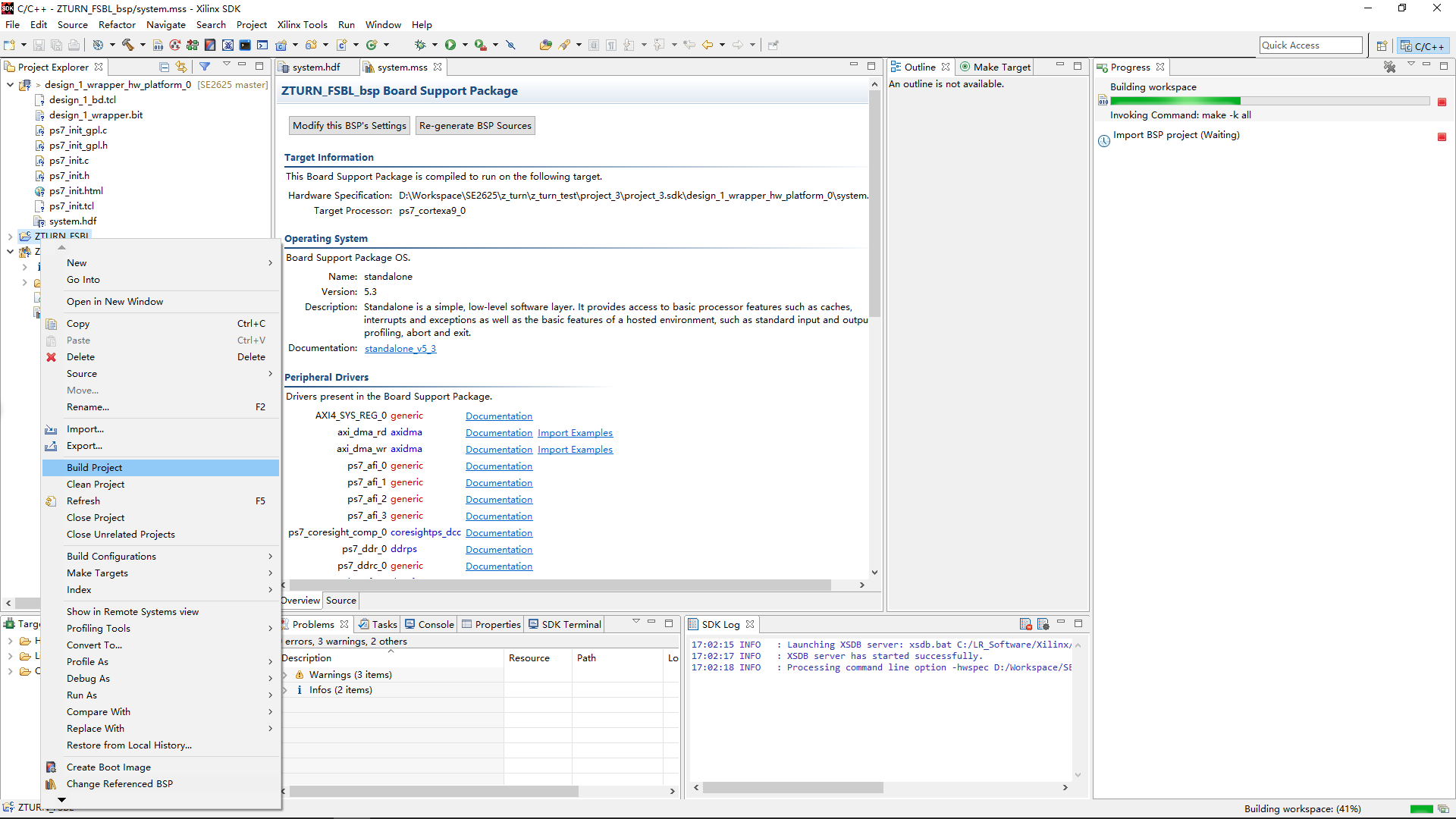

在Project Explorer窗口中,选择FSBL项目,点击右键,在弹出菜单中选择Build Project,对项目进行编译,如图6所示。

编译完成后,会在Debug文件夹中生成ELF文件,该文件既为FSBL文件。

3.FSBL打印调试信息

为了方便调试,查找问题,需要在启动的过程中,打印一些调试信息。FSBL已经提供了很多调试信息,需要进行设置后,才能打印出来。

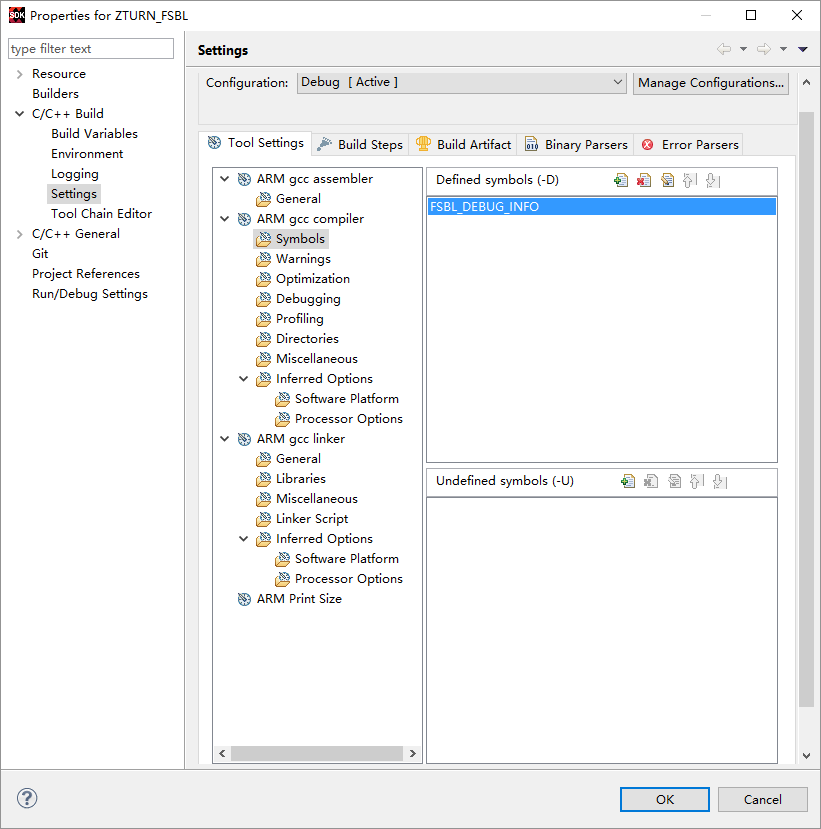

在Project Explorer窗口中,选择FSBL项目,点击右键,在弹出菜单中选择C/C++ Build Settings,弹出设置菜单。

在窗口的左边选择C/C++ Build-Settings,然后选择Tool Settings子窗口,在子窗口中选择ARM gcc compiler-Symbol,添加FSBL_DEBUG_INFO这个预编译选项。如图7所示,然后点击OK。

然后重新编译,生产ELF文件。

在BSP中,默认使用UART0输出调试信息。如果想要从UART1输出调试信号,需要需改system.mss文件。

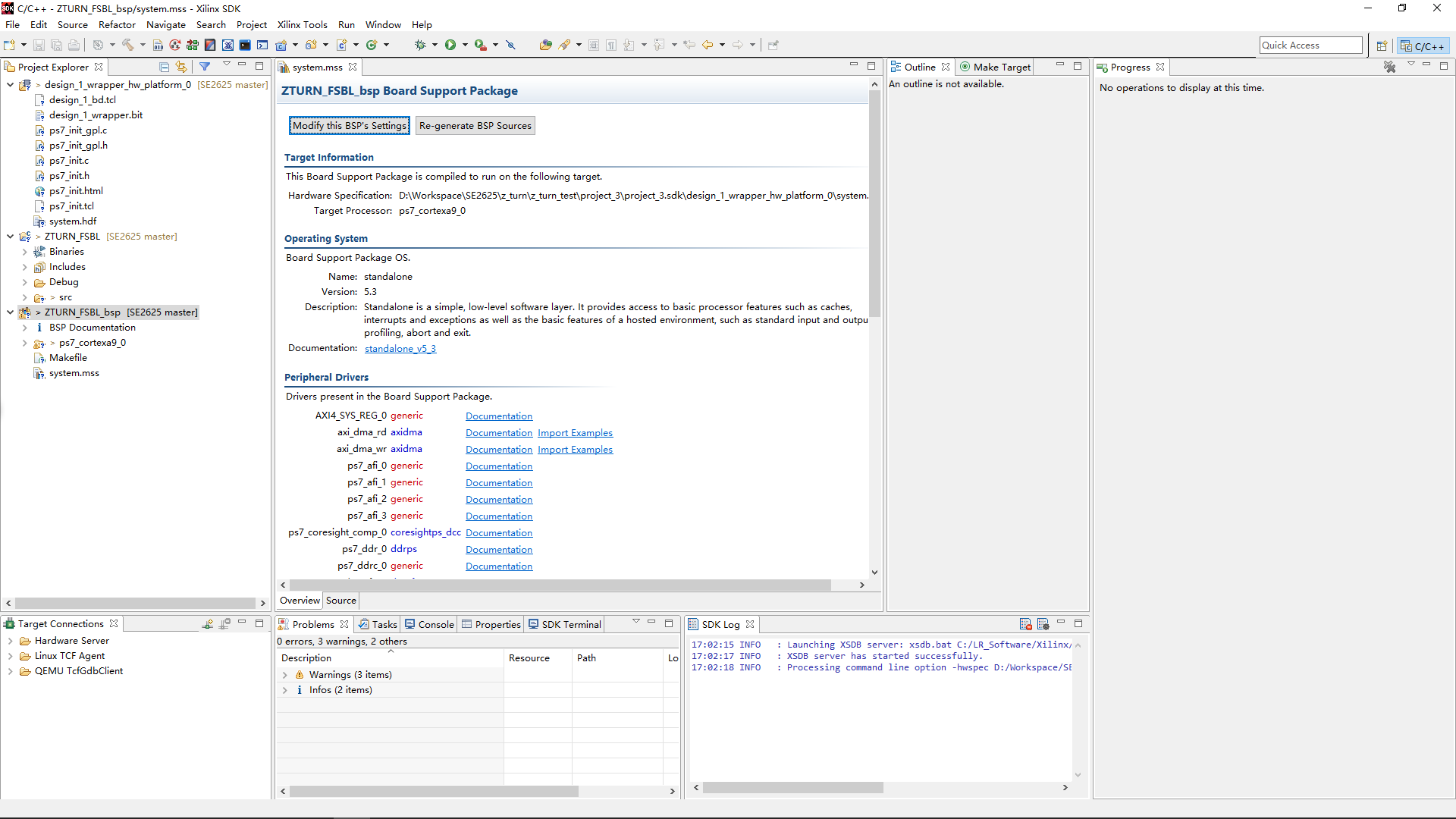

在Project Explorer窗口中,选择FSBL项目的BSP,双击system.mss,打开文件,如图8所示。

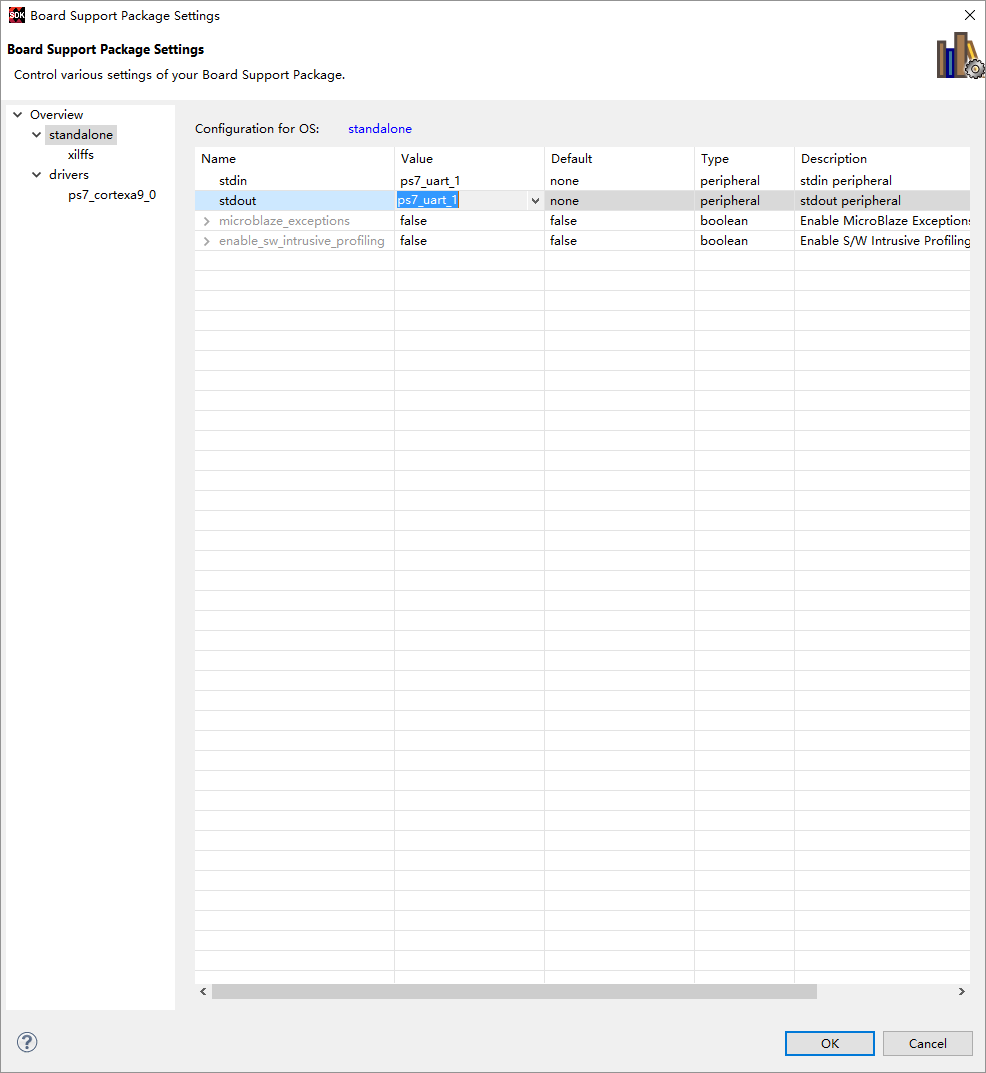

点击Modify this BSP's Settings,弹出配置菜单。然后配置菜单中选择Overview-standalone,将stdin和stdout的值都改为ps7_uart_1。如图9所示。

然在system.mss上点击Re-generate BSP Sources,重新编译FSBL项目,生产ELF文件。

3417

3417

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?