UART(UniversalAsynchronous ReceiverTransmitter,通用异步收发器)是一种广泛使用的异步串行数据通信协议。目前大多数MCU、串口通信IC等芯片或模块均支持UART通信,随着CPLD/FPGA应用得越来越广泛,用CPLD/FPGA来设计UART等接口已是数字电路设计的常见应用之一。

由于UART是异步传输,没有传输同步时钟。在CPLD/FPGA的UART接口设计中,为了能保证数据接收的正确性,数据帧接收时需采用比数据波特率至少高2倍的采样时钟对数据进行采样,才能保证对数据采样不失真或误码,实际波特率时钟采样比最好大于10倍。简单起见,可以取中间时钟的采样值作为数据真实值,采样时钟从系统时钟(晶振)分频得到。虽然理论上照此设计便可保证UART数据传送和接收时不发生误码,但由于在实际设计UART数据通信时,存在采样时钟偏差、数据帧格式、传输波特率及设计的舍入误差等因素的影响,对确定数据波特率传输的UART数据收发器,如何选择恰当的系统时钟(晶振)来保证UART通信的正常或者换句话说,对确定系统时钟(晶振)的UART数据收发器能支持多大的数据通信波特率?这是一个值得探讨的问题。本文对采用CPLD或FPGA进行UART数据收发器设计时,上述提到的问题作个简单的讨论,错误之处还请大家包涵。

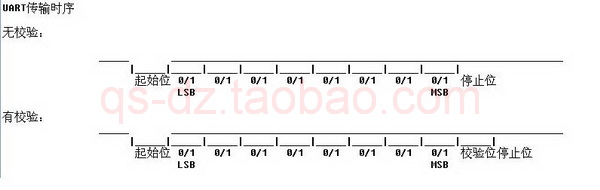

下面简单介绍一下UART时序及其发送接收过程。

发送数据帧过程:空闲状态,线路处于高电平。当开始发送时,先发送起始位(线路保持1个数据位的低电平时间),接着按低位到高位的顺序发送数据位、奇偶校验位(如果需要校验的话)及停止位(停止位为高电平)。

接收数据帧过程:空闲状态,线路处于高电平。当检测到线路的下降沿(线路电平由高变低)时说明线路接收到数据传输的起始位,这时可按照指定的波特率从低位到高位接收数据位、奇偶校验位(如果需要校验的话)及停止位,并完成数据校验,根据校验情况决定数据的处理。

基于上面提到的设计模型,当数据接收发生误码时,上述各影响因素本质上是影响到数据采样时钟的采样位置,使得采样时钟与正常数据采样位置发生了偏差而导致误码,因此计算出采样时钟的采样位置偏差,并保证其不偏离数据位宽范围即可保证数据接收时不发生误码。由于从起始位开始接收时,采样位置偏差即开始累计,所以数据帧最后一位的采样位置偏差应为最大,故若能保证接收数据帧最后一位的采样位置累计偏差的绝对值小于指定波特率对应传输位宽的一半就能保证UART通信时数据接收不发生误码。可以得到下面(1)式:

ETS(W-0.5)<0.5/P -------(1)

其中:

E---计算波特率采样时钟时的系统时钟分频数的最大舍入误差,其值为0.5。

T---晶振周期。

S---波特率时钟采样比=波特率采样时钟频率/数据波特率。

W---传输位数。

P---数据波特率。

根据(1)式可以计算(2)式

f>2PES(W-0.5) -------(2)

其中:f为晶振频率。

举例来说,若CPLD或FPGA采用10MHz外部晶振作为系统时钟时,对于常用的串口数据通信设置“?,N,8,1---?,无校验位,8个数据位,1个停止位”,(2)式中晶振频率f为10000000,传输位数W为10,波特率时钟采样比S若取为16,则支持的数据通信波特率应小于65789.5bps。同样对常用的“115200,N,8,1---115200波特率,无校验位,8个数据位,1个停止位”,可计算出系统时钟(晶振)频率应大于17510400Hz才可保证UART通信不发生误码。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?