提到中断就必须了解到GIC,下面先了解一下GIC

一、GIC概念

GIC(Generic Interrupt Controller)是ARM公司提供的一个通用的中断控制器。GIC通过AMBA(Advanced Microcontroller Bus Architecture)这样的片上总线连接到一个或者多个ARM processor上。

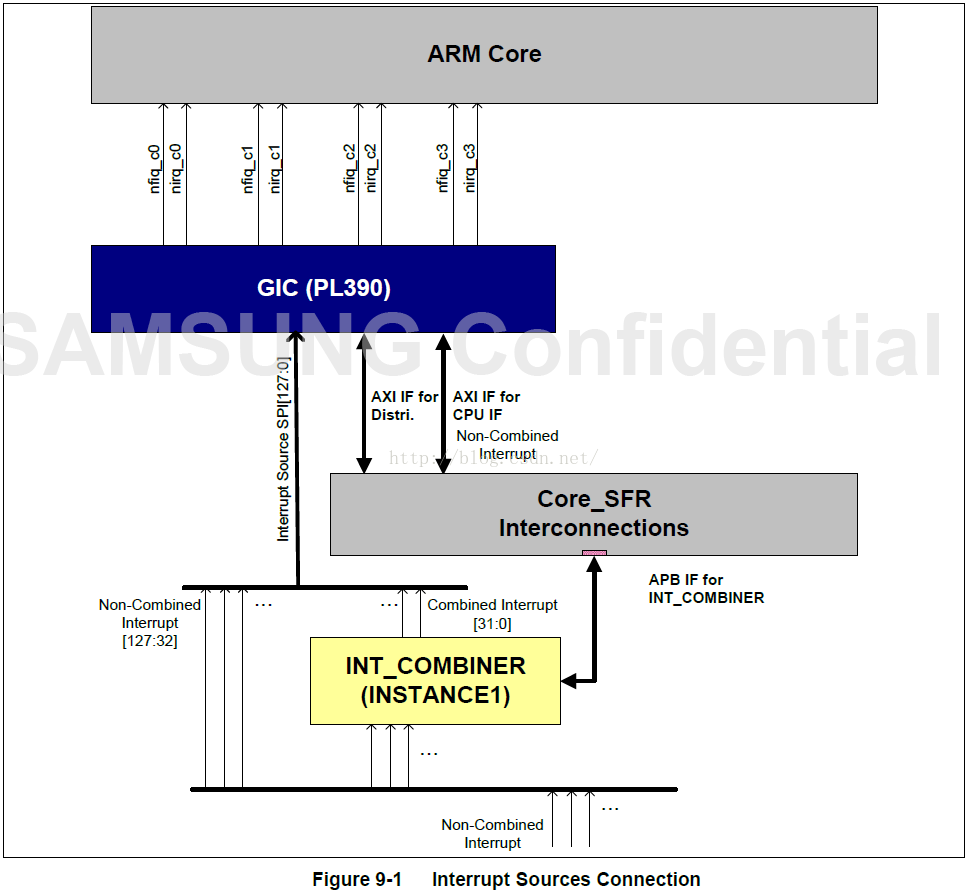

下面是Exynos4412-fs4412 开发板(内核版本为 Linux 3.14)的中断源连线:

二、设备树中中断如何工作

与遵循树的自然结构而进行的地址转换不同,机器上的任何设备都可以发起和终止中断信号。另外地址的编址也不同于中断信号,前者是设备树的自然表示,而后者者表现为独立于设备树结构的节点之间的链接。描述中断连接需要四个属性:

■ interrupt-controller - 一个空的属性定义该节点作为一个接收中断信号的设备。

■ #interrupt-cells - 这是一个中断控制器节点的属性。它声明了该中断控制器的中断指示符中 cell 的个数(类似于 #address-cells 和 #size-cells)。

■ interrupt-parent - 这是一个设备节点的属性,包含一个指向该设备连接的中断控制器的 phandle。那些没有 interrupt-parent 的节点则从它们的父节点中继承该属性。

■ interrupts - 一个设备节点属性,包含一个中断指示符的列表,对应于该设备上的每个中断输出信号。

中断指示符是一个或多个 cell 的数据(由 #interrupt-cells 指定),这些数据指定了该设备连接至哪些输入中断。在以下的例子中,大部分设备都只有一个输出中断,但也有可能在一个设备上有多个输出中断。一个中断指示符的意义完全取决于与中断控制器设备的 binding。每个中断控制器可以决定使用几个 cell 来唯一的定义一个输入中断。

下面的代码为我们 Coyote's Revenge 模型机添加了中断连接:

/ {

compatible = "acme,coyotes-revenge";

#address-cells = <1>;

#size-cells = <1>;

interrupt-parent = <&intc>;

cpus {

#address-cells = <1>;

#size-cells = <0>;

cpu@0 {

compatible = "arm,cortex-a9";

reg = <0>;

};

cpu@1 {

compatible = "arm,cortex-a9";

reg = <1>;

};

};

serial@101f0000 {

compatible = "arm,pl011";

reg = <0x101f0000 0x1000 >;

interrupts = < 1 0 >;

};

serial@101f2000 {

compatible = "arm,pl011";

reg = <0x101f2000 0x1000 >;

interrupts = < 2 0 >;

};

gpio@101f3000 {

compatible = "arm,pl061";

reg = <0x101f3000 0x1000

0x101f4000 0x0010>;

interrupts = < 3 0 >;

};

intc: interrupt-controller@10140000 {

compatible = "arm,pl190";

reg = <0x10140000 0x1000 >;

interrupt-controller;

#interrupt-cells = <2>;

};

spi@10115000 {

compatible = "arm,pl022";

reg = <0x10115000 0x1000 >;

interrupts = < 4 0 >;

};

external-bus {

#address-cells = <2>

#size-cells = <1>;

ranges = <0 0 0x10100000 0x10000 // Chipselect 1, Ethernet

1 0 0x101

本文详细介绍了Exynos4412开发板上中断驱动的开发,重点讲解了GIC(Generic Interrupt Controller)的工作原理,以及设备树中中断节点的创建过程,包括interrupt-controller、#interrupt-cells、interrupt-parent和interrupts属性的使用。同时,讨论了中断系统中的processor、Interrupt Generating Device和interrupt controller的角色,并以UART3为例说明了如何在DTS中描述中断和中断控制器。

本文详细介绍了Exynos4412开发板上中断驱动的开发,重点讲解了GIC(Generic Interrupt Controller)的工作原理,以及设备树中中断节点的创建过程,包括interrupt-controller、#interrupt-cells、interrupt-parent和interrupts属性的使用。同时,讨论了中断系统中的processor、Interrupt Generating Device和interrupt controller的角色,并以UART3为例说明了如何在DTS中描述中断和中断控制器。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8028

8028

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?