(本文章免费, 若发现需要vip, 请私信联系)

一、实验目的和任务

实验目的:

学习理解数字逻辑电路中的双向移位寄存器74LS194,计数器74193以及D触发器74LS74的综合设计与应用。激发创新能力。

实验任务:

设计一个4路彩灯控制电路,要求按以下方式循环。

方式一:灯依次点亮

0000(初态)→1000→1100→11110→1111,共4秒;

方式二:灯依次熄灭

1111(初态)→1110→1100→1000→0000,共4秒;

方式三:灯全亮1秒,灯全灭1秒,再循环一次,共4秒。

0000(初态)→1111→0000→1111→0000

方式一 → 方式二 → 方式三 → 方式一....每个方式都占4个节拍

二、芯片74LS194、74LS193

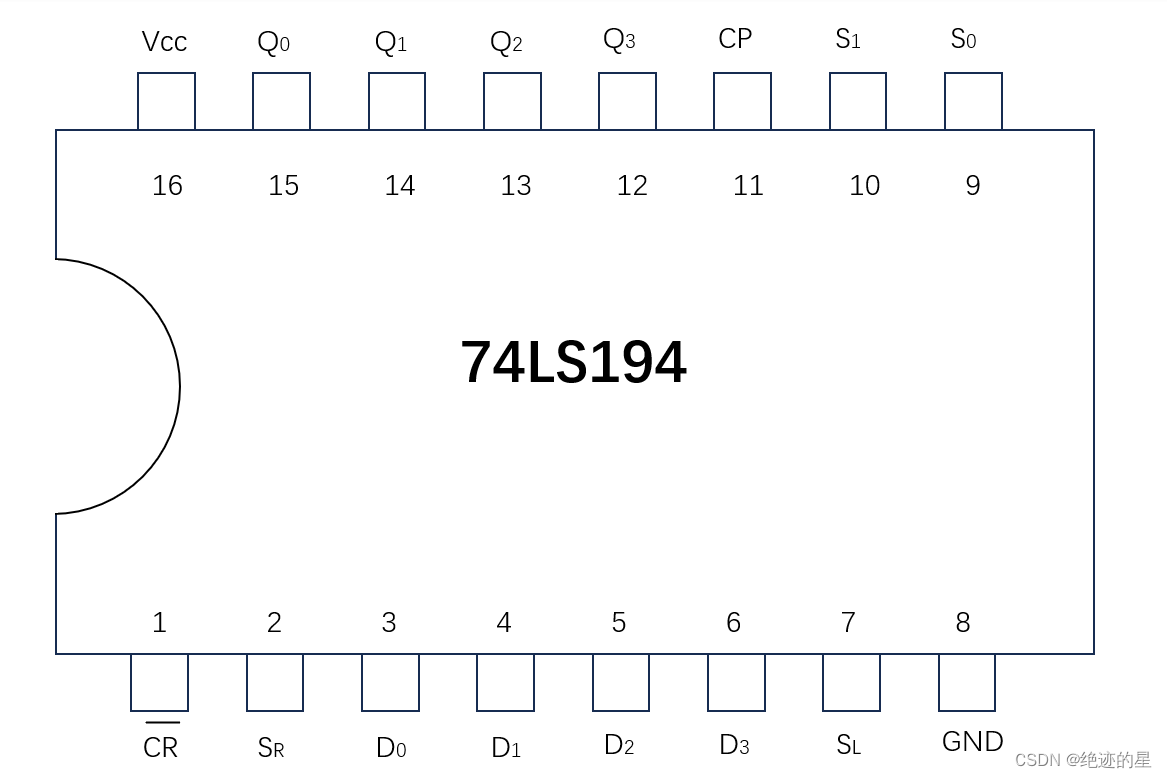

74LS194

74LS194是一个双向移位寄存器

- D0~D3为并行输入端

- Q0~Q3为并行输出端

- SL为左移串行输入端, 在S1S0=10左移状态下生效

- SR为右移串行输入端, 在S1S0=01右移状态下生效

- S1和S0为操作模式控制端

- S1S0=00为保持状态, 输出Q不变

- S1S0=01为右移状态, 将输出Q0~Q3右移, 并将SR转移到Q0

-

- S1S0=10为左移状态, 将输出Q0~Q3左移, 并将SL转移到Q3

- S1S0=11为送数状态, 将输入端D0~D3转移到输出端Q0~Q3

- CR为清零端,低电平生效,当输入低电平时,输出Q为0

- CP为时钟脉冲输入端

| 功能 | 控制信号 | 串行输入 | 并行输入 | 输出 | ||||||||

| S1 | S0 | SL | SR | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 | |

| 保持 | 0 | 0 | Q0 | Q1 | Q2 | Q3 | ||||||

| 右移 | 0 | 1 | x | x | Q0 | Q1 | Q2 | |||||

| 左移 | 1 | 0 | x | Q1 | Q2 | Q3 | x | |||||

| 送数 | 1 | 1 | a | b | c | d | a | b | c | d | ||

表格的留空处表示 不关心输入是什么, 他们对输出没有影响

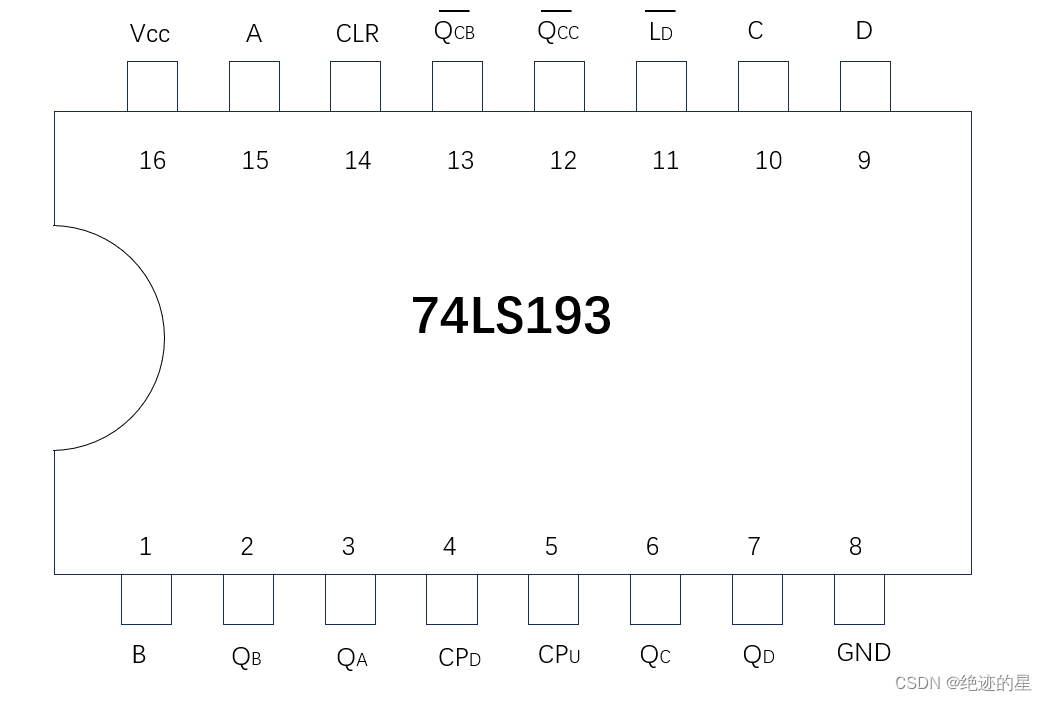

74LS193

74LS193是同步四位二进制可逆计数器, 它具有双时钟输入, 并且有异步清零和异步置数等功能

- A~D为并行数据输入端

- QA~QD为输出端

- QC-BORROW为借位输出端, QD~QA由0000减1产生负溢出后, 输出信号0, 其他时候输出1

- QC-CARRY为进位输出端, QD~QA由1111加1溢出时输出信号0,其他时候输出1

- CP-DOWN为减计数时钟输入端, CP-UP为加计数时钟输入端

- CLR为异步清零端, 高电平生效, 当输入高电平时输出Q为0

- LD为异步并行置入控制端, 低电平生效, 当输入低电平时触发送数功能, 将A~B数据转移到Q端

| 功能 | LD | 输入 | 输出(A为低位) | ||||||

| A | B | C | D | QA | QB | QC | QD | ||

| 送数 | 0 | a | b | c | d | a | b | c | d |

| 计数 | 1 | CP-UP上升沿加1计数 例如QD QC QB QA = 0101 加1计数后为0110 | |||||||

| CP-DOWN上升沿减1计数 例如QD~QA = 0101 减1计数后为0100 | |||||||||

三、子系统设计

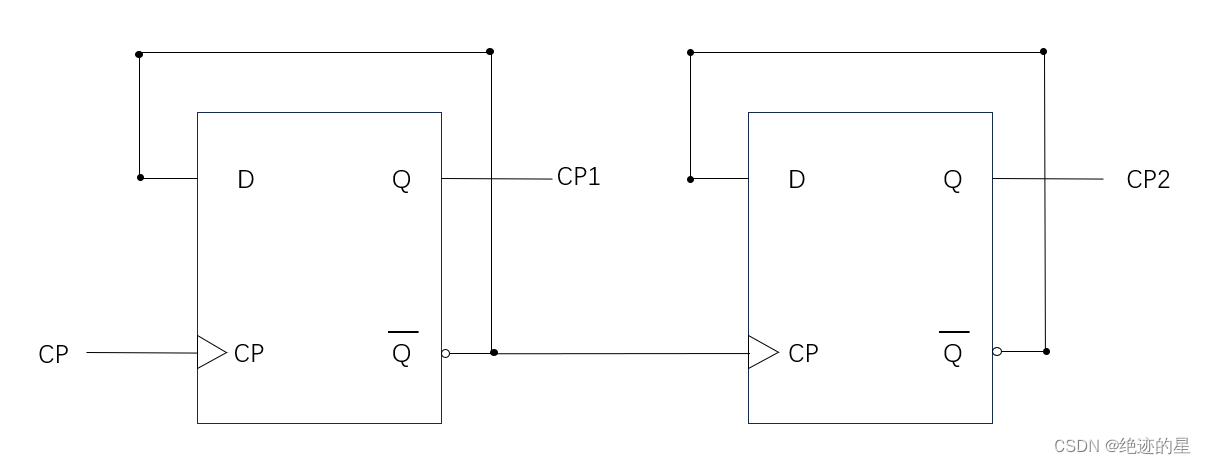

①四分频电路

彩灯控制电路每个方式都需要占4个节拍, 所以需要四分频, 将CP方波进行四分

D触发器在CP上升沿触发, 将D端数据转移到Q端

上图在CP上升沿,将Q置为D,而后的一个周期Q端数据不变,直到这个周期结束,CP上升沿再次到来,使Q=D=¬Q,实现Q的翻转, 所以,CP1为每个CP周期翻转一次, 它的周期长度是CP的2倍, 也就是二分频, 同理CP2就是4分频了

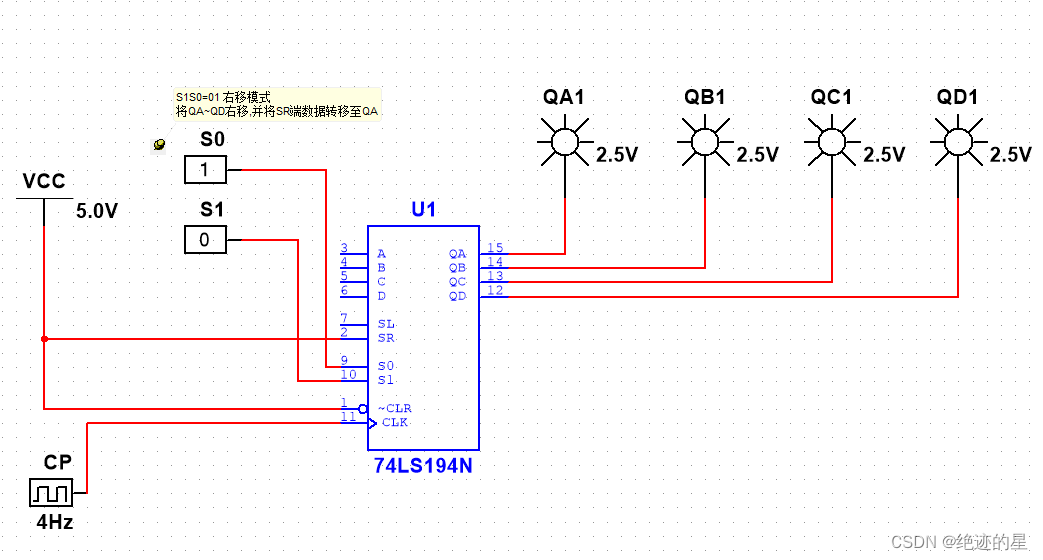

②194彩灯控制系统

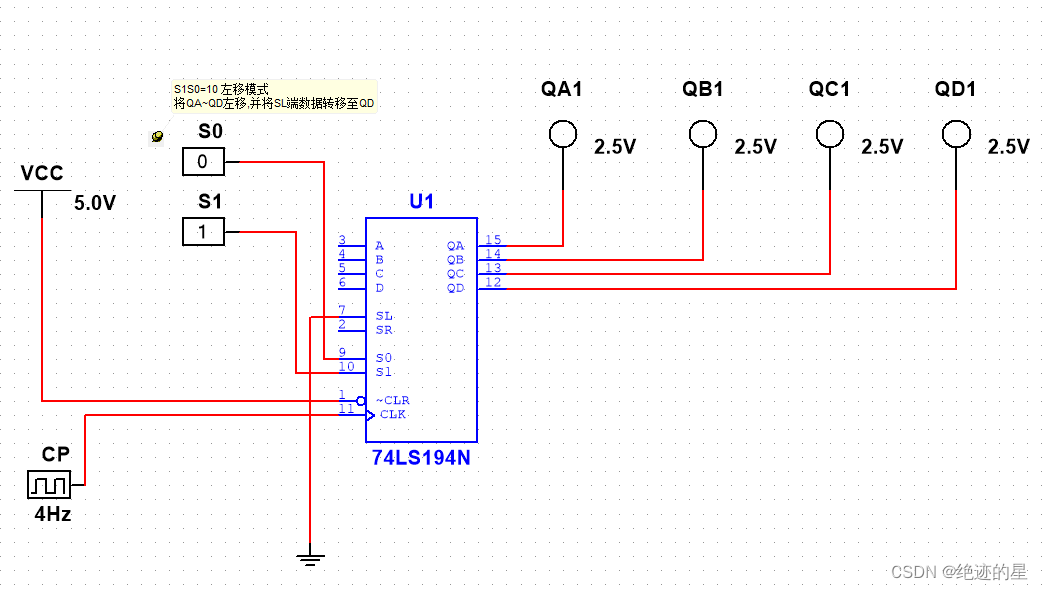

方式一

0000(初态)→1000→1100→1110→1111, QA到QD依次点亮

可以使用右移操作, 每次将QA~QD右移, 使下一个灯点亮

为保持右移后QA不熄灭, 需要将QA置1(SR=1)

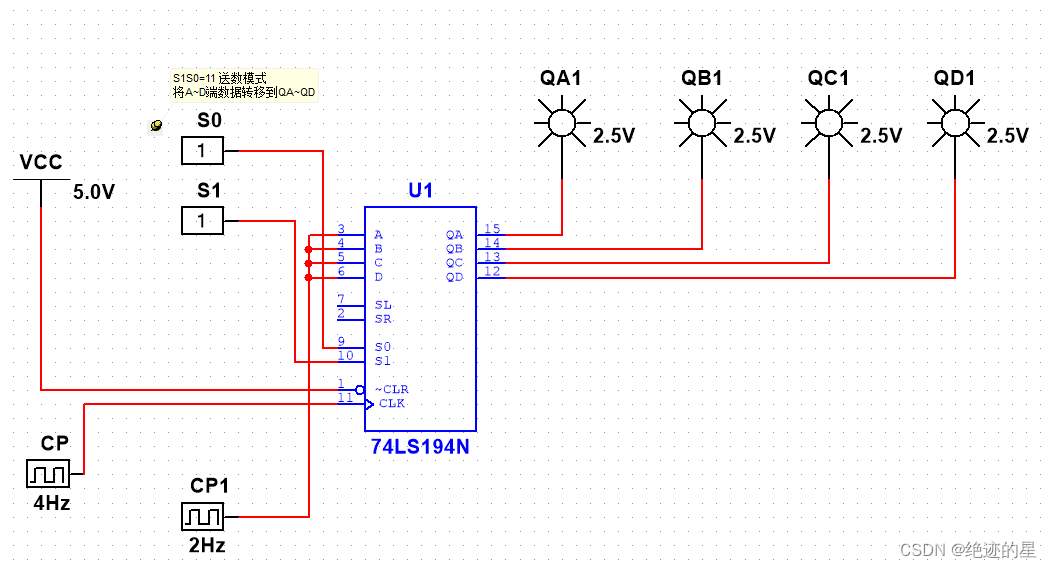

方式二

1111(初态)→1110→1100→1000→0000, QD到QA依次熄灭

可以使用左移操作, 每次将QA~QD左移, 使下一个灯熄灭

为保持左移后QD不被点亮, 需要将QD置0(SL=0)

方式三

0000(初态)→1111→0000→1111→0000, 灯在全亮和全灭间循环

可以在A~D端接入脉冲, 然后使用送数功能, 通过脉冲不断进行置0和置1, 实现全亮和全灭循环

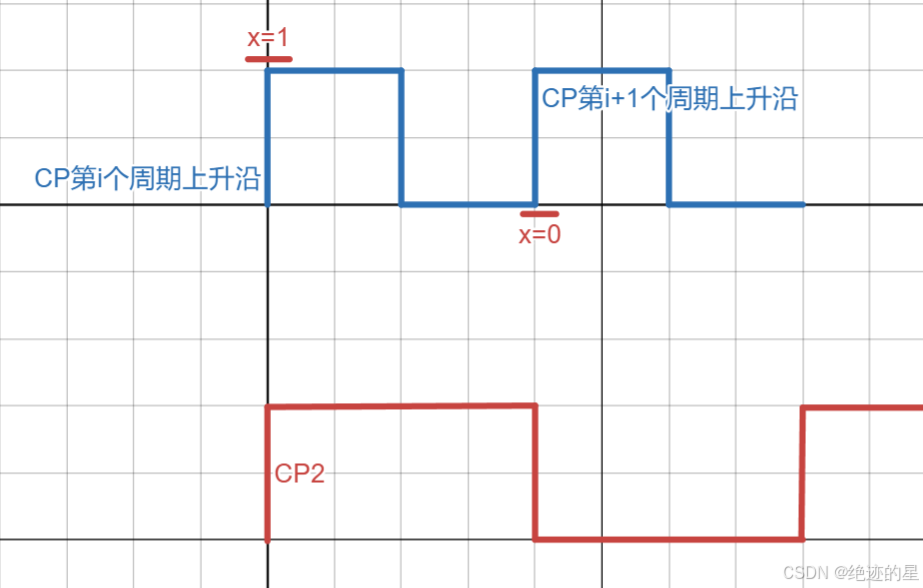

对于A~D端接入的时钟,它应当是CP的二分频, 理由如下:

对于A~D端接入的时钟,它应当是CP的二分频, 理由如下:

芯片194在CP上升沿触发, 也就是每过一个CP周期切换一次状态

如果CP的第i个周期上升沿时CP1为x, 需要CP的第i+1个周期上升沿时CP1为¬x, 可以看出每两个CP周期是CP1的一个周期, 所以CP1应该为CP的二分频(如图)

可能相位不同, 但因为周期是2倍, 也不会出错

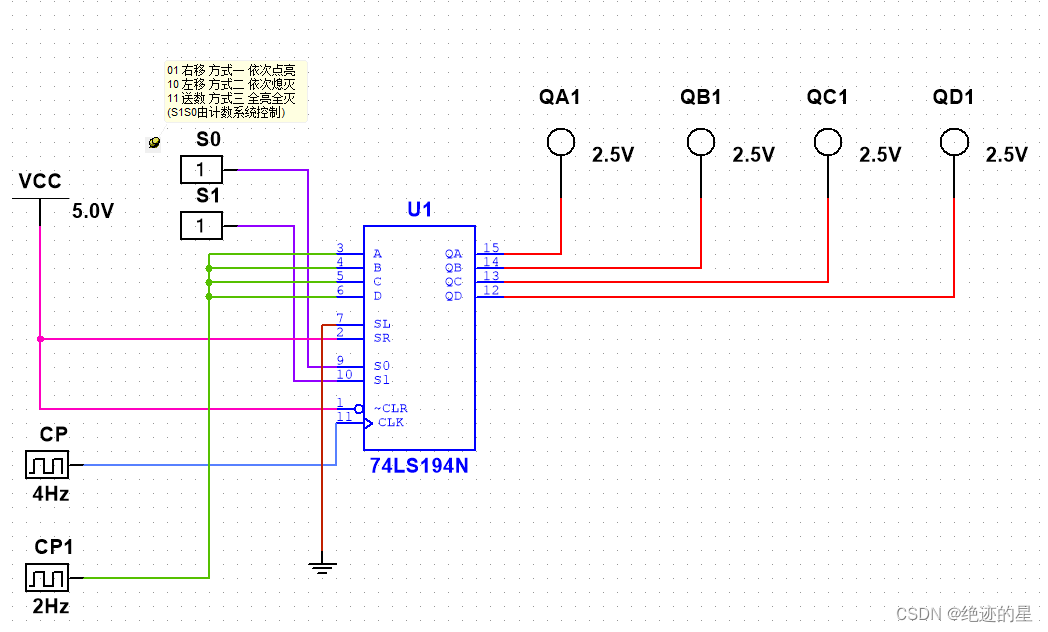

三种方式组合

最后将三种模式组合, 得到彩灯控制系统, 其中的S1S0需要由计数系统控制

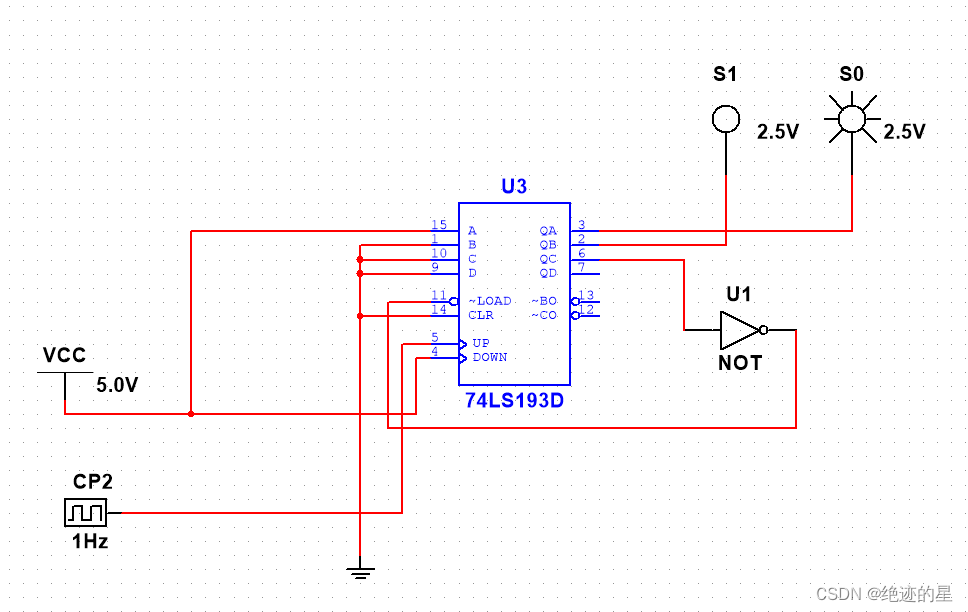

③193计数系统

根据彩灯控制系统结论, 要实现方式一→方式二→方式三的循环, 需要控制S1S0的循环

S1S0对应循环为: 01→10→11 每个计数占4个节拍

这是两位二进制计数,所以只需要使用193的4个输出中的两个即可, 令QA对应S0, QB对应S1

即QB QA: 01→10→11

初始时QA置1(接Vcc), QB置0(接地)

然后CP-UP需要接入脉冲源, 每次加1计数

当QBQA=11时, 再加1变成00, 由于00是不需要的, 所以此时需要重置计数.

重置计数: 可以使用LD端的送数功能, 将QA与QB重新赋值, 所以LD可以接入¬QC(LD端低电平生效, QC为1时说明QBQA溢出了), 也可以不使用QC=1, 使用或门LD = QA + QB, 是等效的

对于CP-UP接入的脉冲, 它应该是CP的四分频, 因为每个模式占4个节拍, 计数每加4切换一次模式

对于CP-UP接入的脉冲, 它应该是CP的四分频, 因为每个模式占4个节拍, 计数每加4切换一次模式

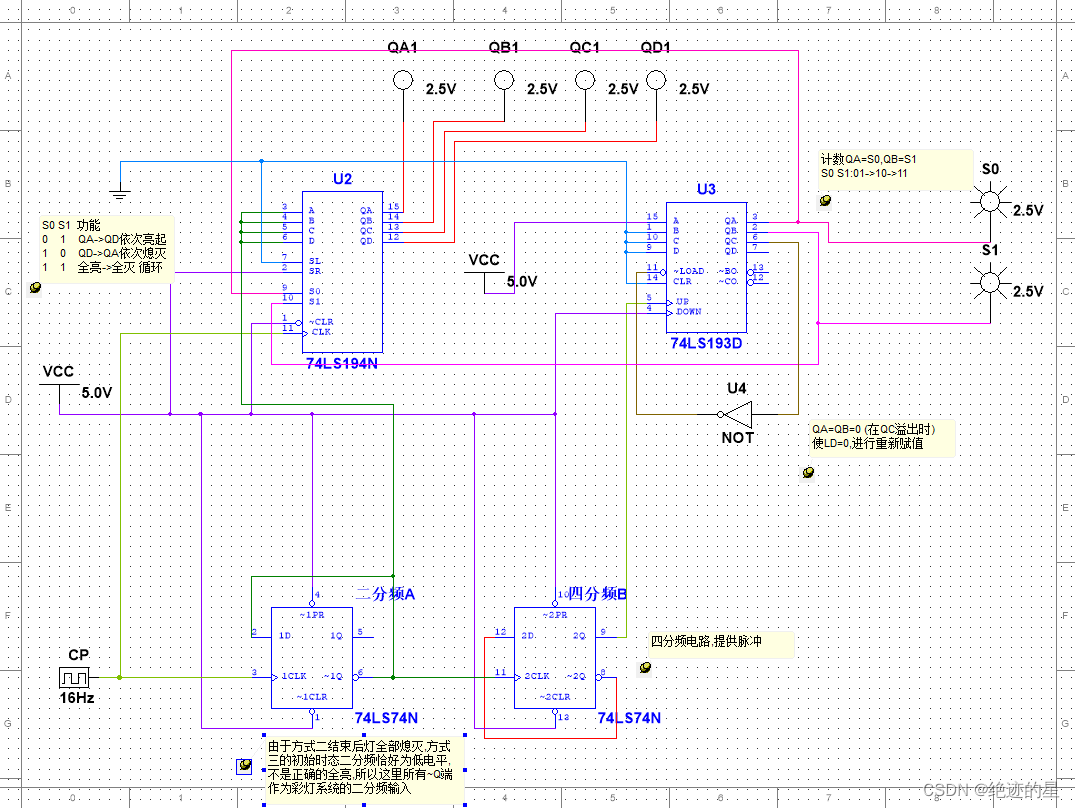

四、电路设计

电路由上面的三个子系统构成

- 四分频电路提供需要的脉冲源

- 193计数系统控制彩灯模式, 控制S1S0模式信号

- 194彩灯系统接收计数系统的S1 S0模式信号, 控制彩灯的点亮与熄灭

CP → 二分频A、四分频B

四分频B → 193计数器 → 模式信号S1S0

S1S0 → 194移位寄存器 → 彩灯QA~QD

2154

2154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?