(本文章免费, 若发现需要vip, 请私信联系)

一、实验目的和任务

实验目的:

-

掌握中规模集成数据选择器的逻辑功能及使用方法。

-

学习数据选择器153构成组合逻辑的方法。

关键词:74153

实验任务:

用74LS153和必要的与非门设计制作一个一位二进制全加器电路(设计性实验)

二、芯片引脚及其原理

74LS153

74LS153是一个双通道四输入数据选择器, 实现四选一功能

- Vcc接电源,GND接地

- G1和G2为使能端,低电平生效,当输入低电平时,芯片才允许工作

- D0~D3为输入信号

- S0和S1为选择信号, 当S1 S0=00时选择D0, 当S1S0=01选择D1......

- Y为输出信号 Y=D, 其中D为被选择信号选中的输入端电平

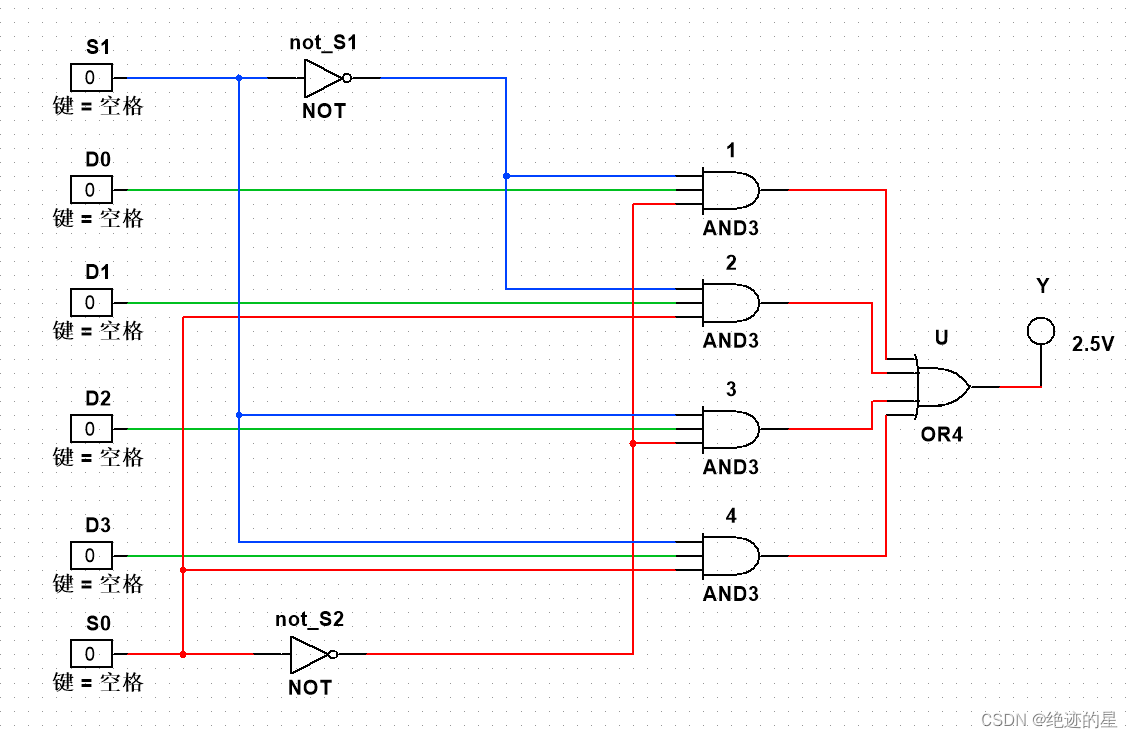

四选一原理

三、一位全加器设计

真值表

| 输入 | 输出 | |||

|---|---|---|---|---|

| C | A | B | S | Ci+1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

其中A为加数, B为被加数, C为相邻低位进位输入

S为本位和输出, Ci+1为向相邻高位的进位输出

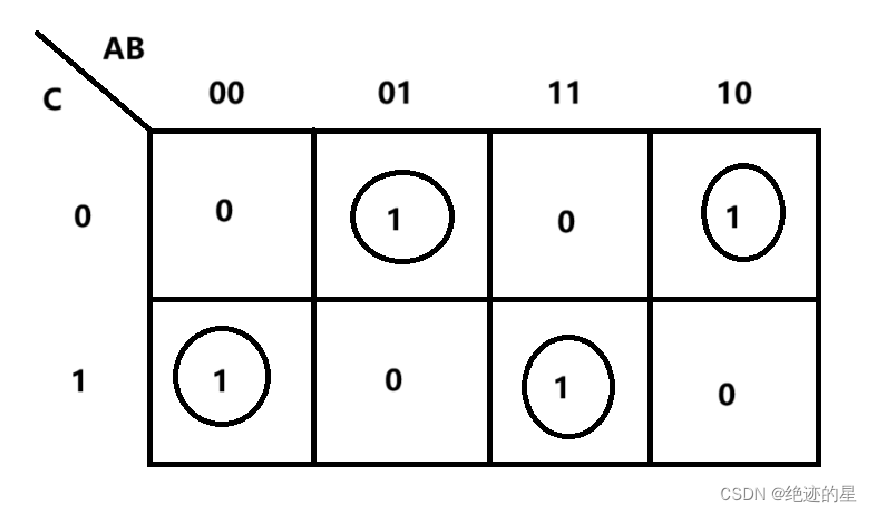

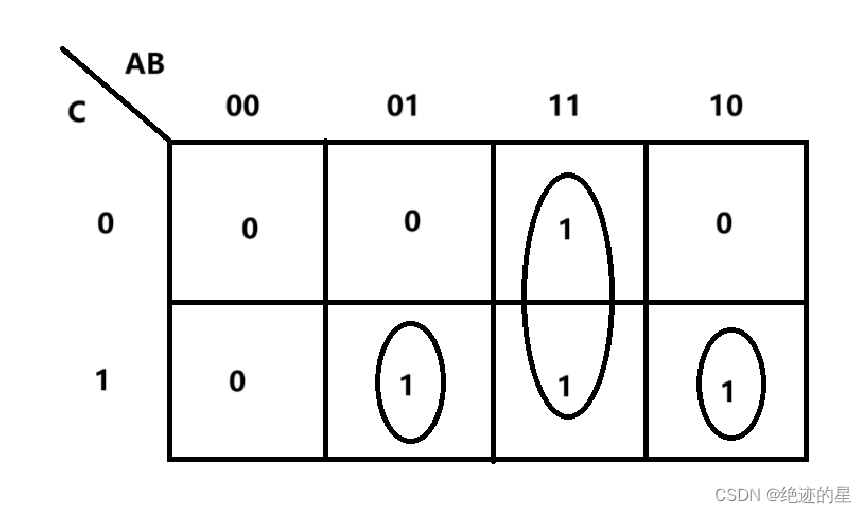

卡诺图

因为要凑成的形式,所以此处卡诺图圈法不太一样

四、电路图

根据 和

对照得:

仿真

5729

5729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?