一、实验目的

1、学习组合逻辑电路的分析方法。

2、通过设计全减加器掌握简单的设计与测试方法。

二、实验所用器件和仪表

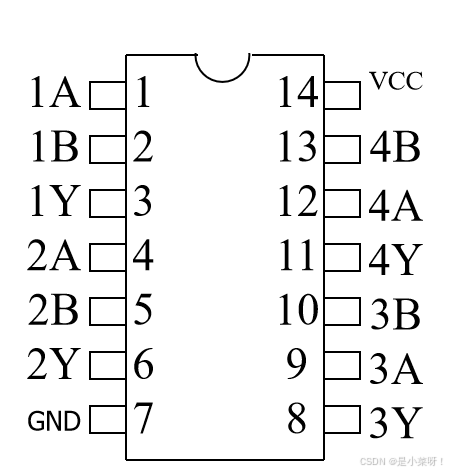

四2输入异或门74LS86 1片

四2输入正与非门74LS00 1片

实验所用芯片 74LS00、 7474ls86

注:图中A、(B)为输入脚,Y为输出脚,VCC接5V电源,GND接地

三、实验原理

1、组合逻辑电路的分析。 当我们研究给定的某一逻辑电路时,有时需要对其功能、设计思想进行研究,以便完善和改进电路。组合逻辑电路的分析,一般可按以下步骤进行:

第一步 根据给定逻辑电路图,写出逻辑函数表达式。

第二步 化简

第三步 列出真值表

第四歩 逻辑问题评述,功能说明,改进、完善(改变)的设想。

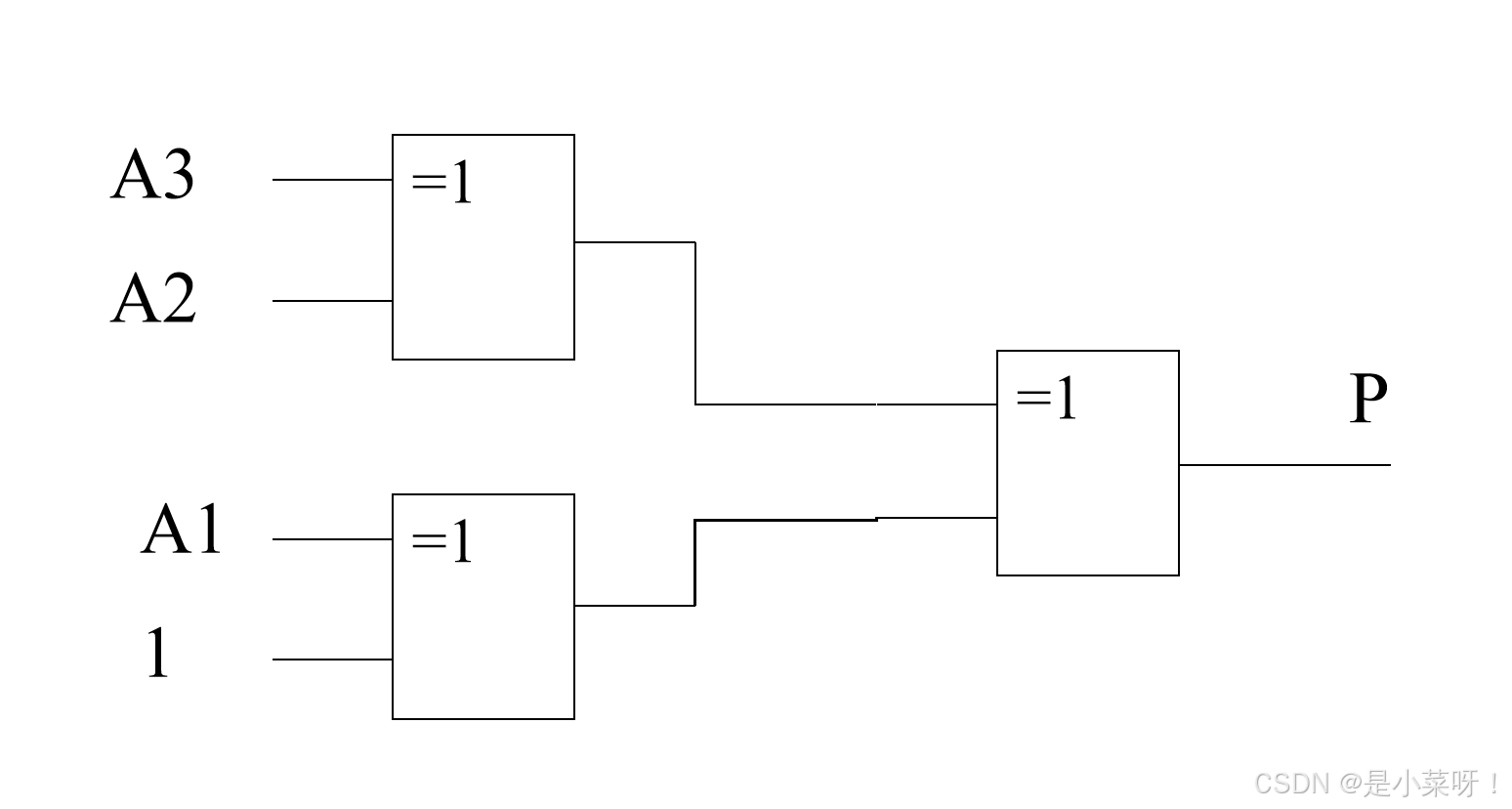

逻辑表达式: P=(A3⊕A2) ⊕(A1 ⊕1)

化简: P=(A3⊕A2) ⊕A1

列出真值表:

| A3 | A2 | A1 | P |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

功能说明:

该电路的功能是判断输入中1的个数是奇数还是偶数。是奇校验位发生器电路。

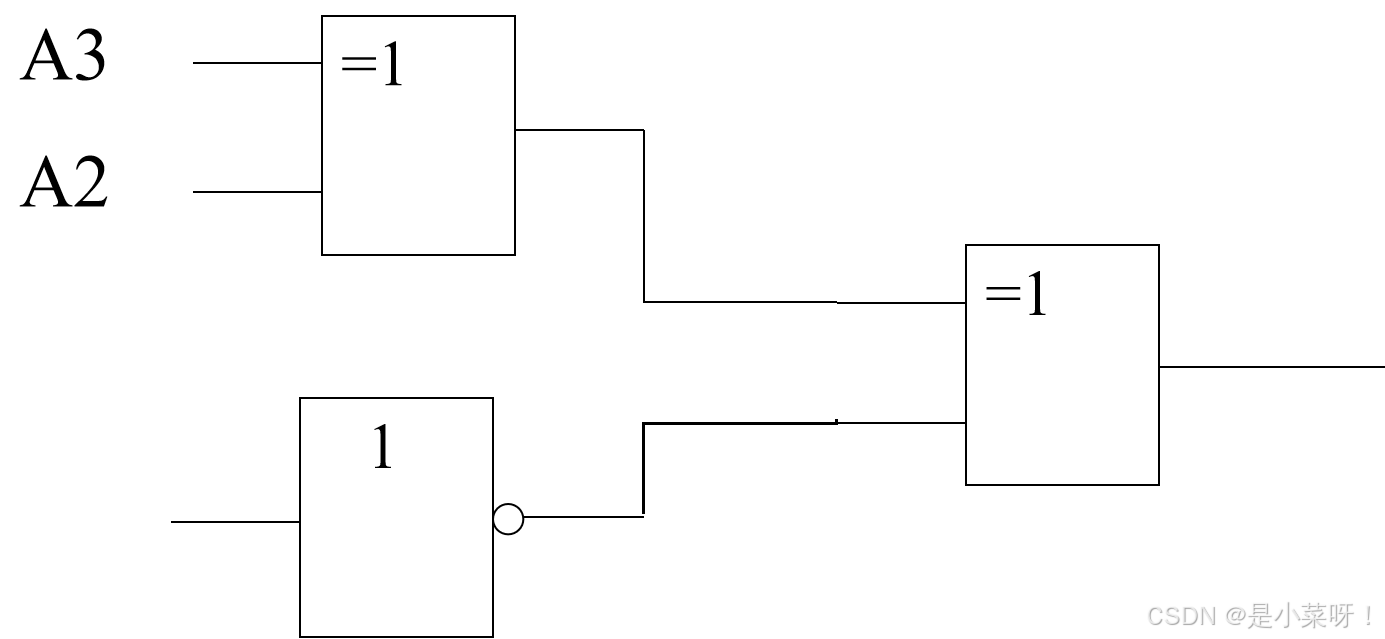

可改变为如下电路:

2、组合逻辑电路的设计

全加减器是数字逻辑中的基础逻辑部件,也是计算机的基本运算单元,在计算机领域中具有重要地位。在日常生活中我们还会遇到各种设计需求,在面对需求时我们也有固定的设计步骤。

第一步 确定功能真值表

第二步 写出逻辑表达式

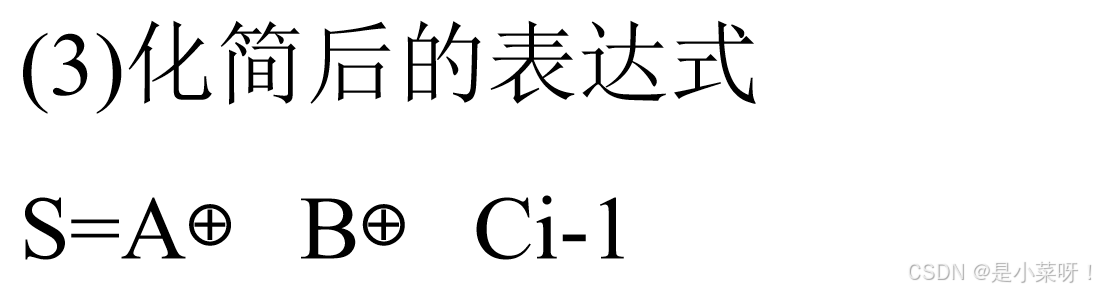

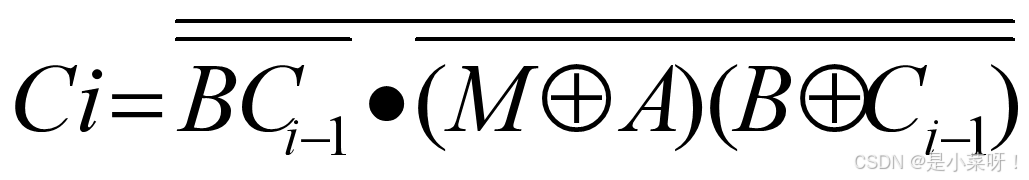

第三步 化简

第四步 根据逻辑表达式画出逻辑电路图

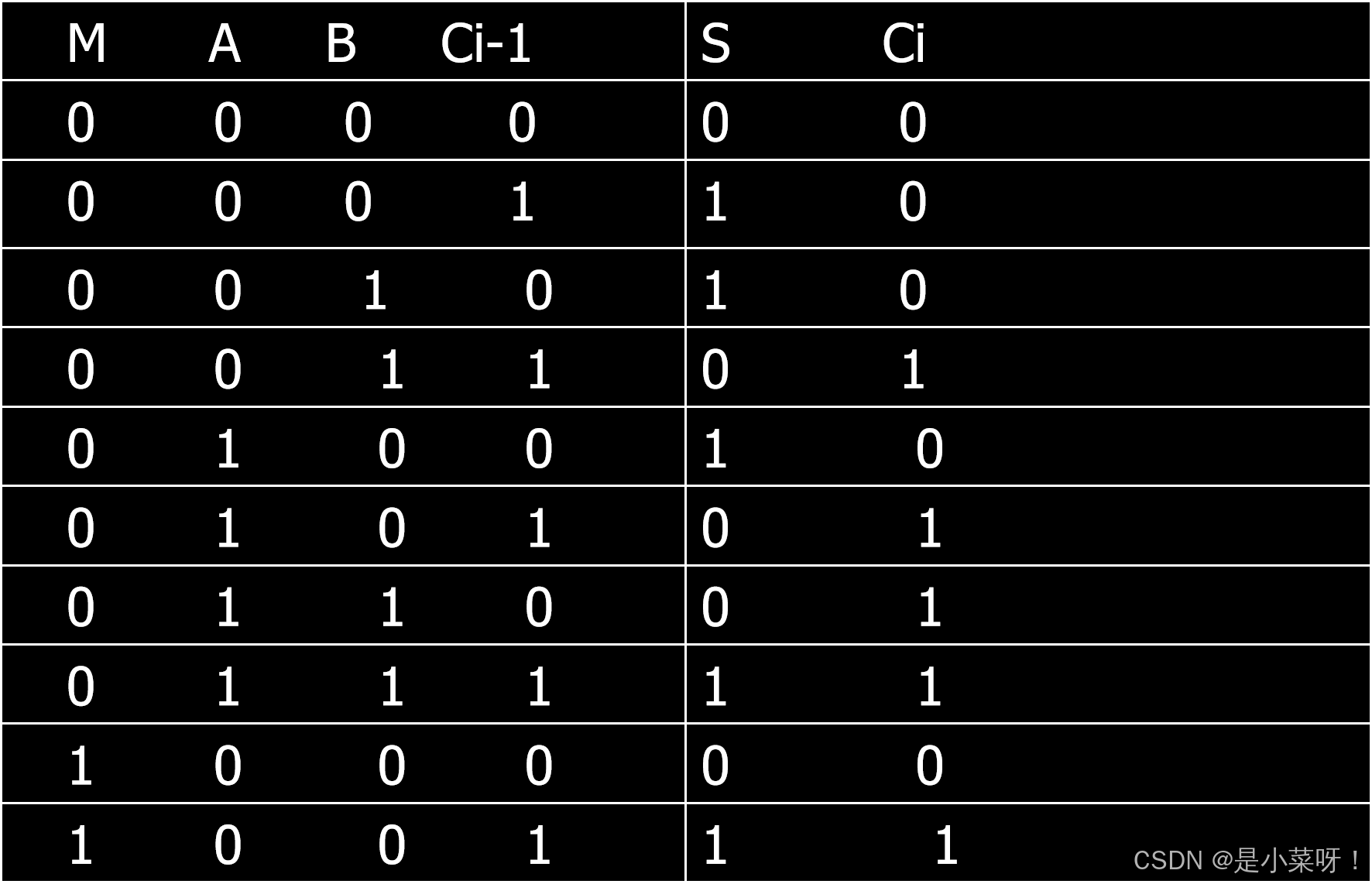

全加减器设计

全加器设计要确定真值表、写出逻辑表达式、画出逻辑电路图。要求用异或门、与非门实现,让设计的电路在M控制下进行加、减运算。当M=0时,实现全加器功能;当M=1时,实现全减器功能。

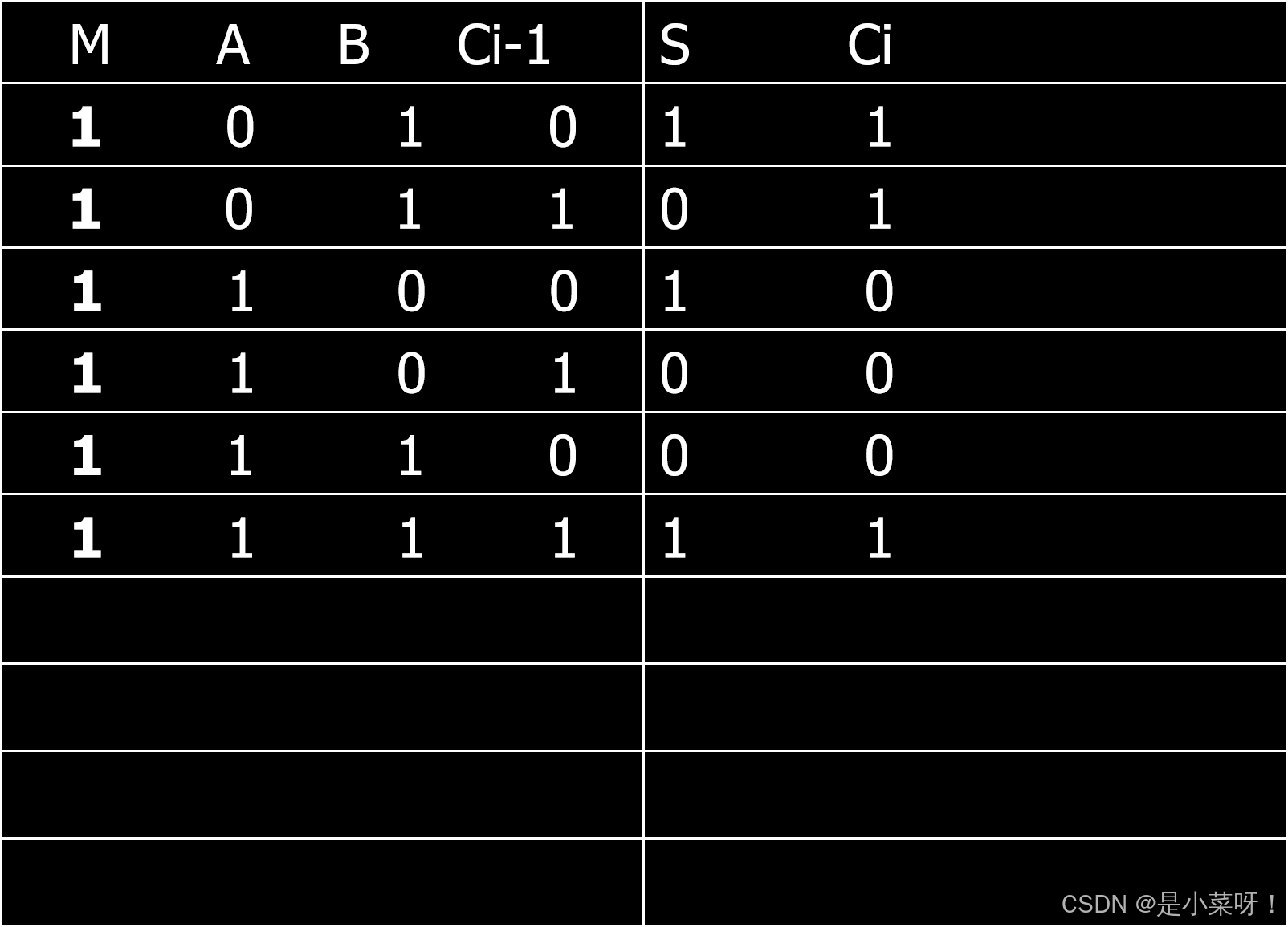

(1)加减器真值表

(2)卡诺图(略)

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?