- 实验目的:

- 熟悉7段数码管显示译码电路的设计。

- 掌握数码管显示原理及静态、动态扫描电路的设计。

- 实验任务:

- 基本任务1:利用FPGA硬件平台上的4位数码管做静态显示,用SW3-0输入BCD码,用SW7-4控制数码管位选;

- 基本任务2:利用FPGA硬件平台上的4位数码管显示模10计数结果(以1S为节拍);

- 基本任务3:利用FPGA硬件平台上的6位数码管显示模100计数结果(以1S为节拍);

- 拓展任务1:对7448译码结果中的“6”和“9”进行补段;

- 拓展任务2:用按键控制计数器从0-9计数,4位数码管显示计数结果;(注意按键消抖)

- 拓展任务3:dig_select、decoder和code_select三个模块做波形仿真。(注意输入设置)

- 任务1指导(重点掌握数码管的静态显示原理和译码电路的设计)

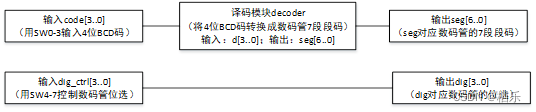

- Top-level设计

2.译码模块decoder设计

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?