领航者 ZYNQ 在线逻辑分析仪(ILA)使用问题分析与优化

本文基于《1_【正点原子】领航者 ZYNQ 之 FPGA 开发指南 V3.2》第 22 章呼吸灯实验中在线逻辑分析仪(ILA)的使用流程,对实验过程中遇到的两类典型问题展开分析,并提出优化方案。

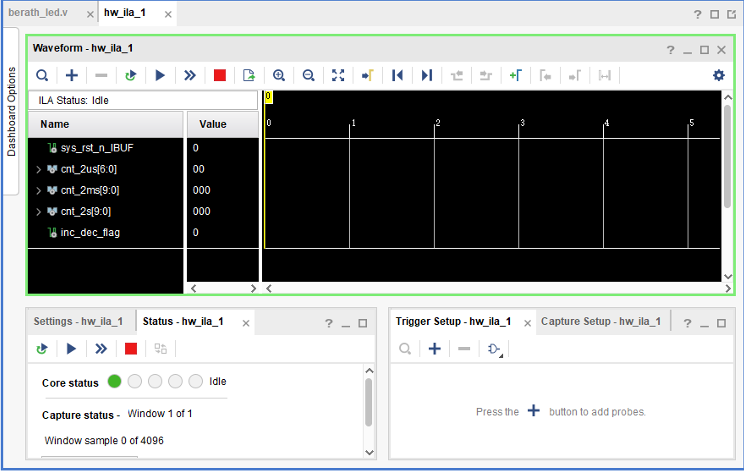

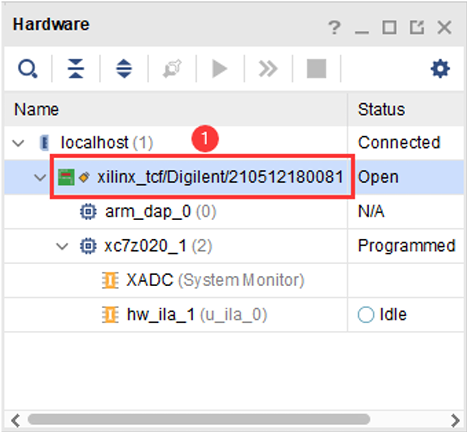

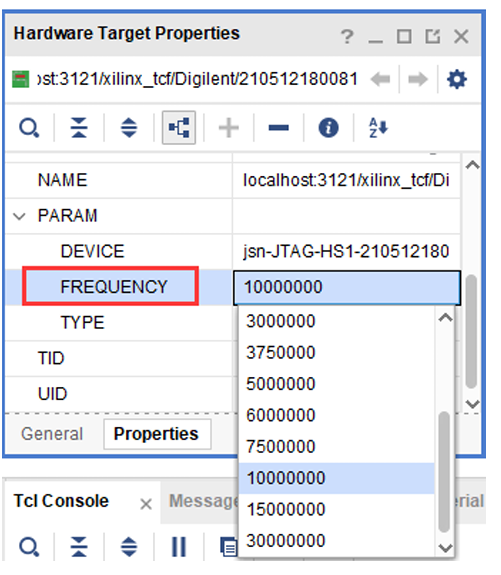

问题一:时序图无信号显示

运行实验时,ILA 界面的时序图区域未出现任何信号波形,既无高电平 “1” 也无低电平 “0” 的显示。此问题可参考开发指南 “22.7.3 对 ILA 的工作时钟频率进一步探究” 章节,其中明确指出:ILA 采样时钟频率需不低于 JTAG 下载器时钟频率的 2.5 倍 。由于默认 JTAG 频率较高,通常可通过调整下载器频率解决该问题,具体修改步骤可参照如下步骤。

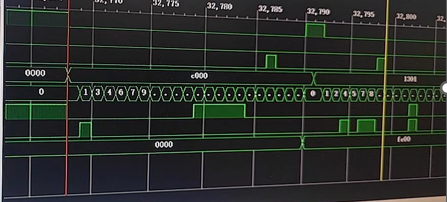

问题二:时序图信号输出异常

实验过程中,虽然 ILA 能显示部分时序图,但信号输出存在明显异常。以其中一条本应为时钟信号的线条为例(图中第二条线),其输出状态始终为 “0”,即便该信号实际存在有效数据。

问题根源分析

时序波形的观测依赖 “采样 - 存储 - 显示” 三个环节,能输出信号意味着 ILA 硬件与基本功能正常,问题大概率出在采样环节。采样过程以 clk 时钟为时间基准,以下是结合实验现象的详细分析:

- clk 信号自采样导致恒 “0” 输出:当使用 clk 信号同时作为采样时钟与被测信号时,观测结果恒为 “0”。推测原因为:采样参考时间与被测信号同源,导致每次采样均处于信号周期的同一相对位置;而输出为 “0” 而非 “1”,可能是由于信号路径延迟等因素造成采样时刻恰好落在低电平区间。

- 采样与被测信号频率差异导致波形失真:当 clk 信号频率为 15MHz、被测信号频率为 10MHz 时,虽能观测到被测信号波形,但与实际不符。这是因为采样时刻滞后于信号变化,且滞后时间因非同步关系呈现随机分布,仅因信号周期固定而表现出周期性变化趋势,从而造成波形失真。

- 特定频率比引发恒 “0” 输出:当采样频率为 30MHz、被测信号频率为 15MHz 时,再次出现被测信号恒为 “0” 的现象。该情况与第一种类似,可能因二者频率关系导致采样点始终处于低电平区域。

- 采样频率不足引发占空比异常:当采样频率为 40MHz、被测信号频率为 15MHz 时,波形基本可见,但偶发方波占空比变化。此问题本质与第二种情况相同,仍是由于采样频率不足,导致无法精准捕捉信号变化,致使占空比出现偏差。

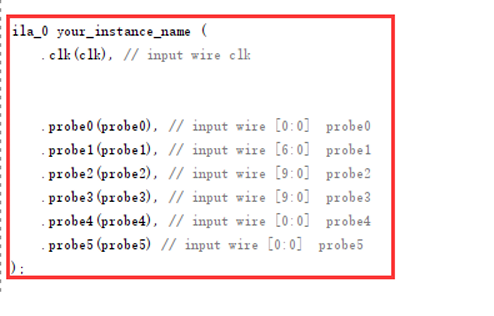

基于上述分析,调整采样时钟信号是解决问题二的关键。建议采用 PLL(锁相环)核生成采样时钟,通过 PLL 核可灵活设置时钟频率与相位,精准匹配被测信号特性,确保采样过程准确可靠,从而获取真实有效的时序波形。

以上对 ILA 使用问题的分析与优化方案,希望能为遇到类似问题的开发者提供参考。

3732

3732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?