使用always语句实现半加器:

(1)报错:[HDL 9-806] Syntax error near "non-printable character with the hex value '0xef'".

原因:Verilog中带有中文字符

(2)Verilog代码:

module ex_half_adder(A,B,Cout,Sum);

input A;

input B;

output reg Cout;

output reg Sum;

always@(*)

{Cout,Sum} = A + B;

endmodule

(3)仿真文件代码:

`timescale 1ns/1ns

module half_adder_tb;

reg A;

reg B;

wire Cout;

wire Sum;

ex_half_adder ex_half_adder_inst(

.A(A),

.B(B),

.Cout(Cout),

.Sum(Sum)

);

initial begin

A <= 1'd0;

B <= 1'd0;

#2000;

$stop;

end

always #10 A<= {$random} % 2;

always #10 B<= {$random} % 2;

endmodule

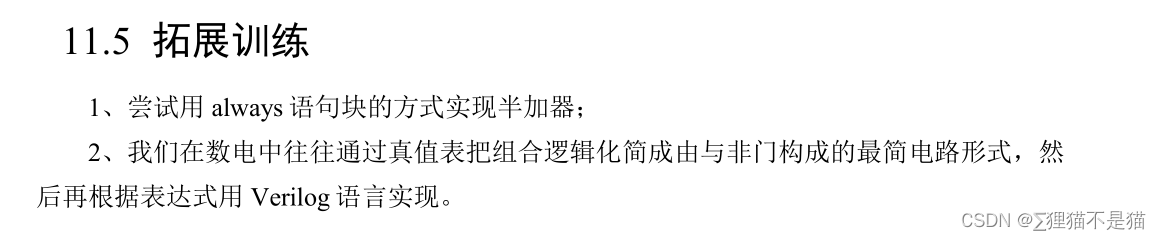

(4)RTL视图

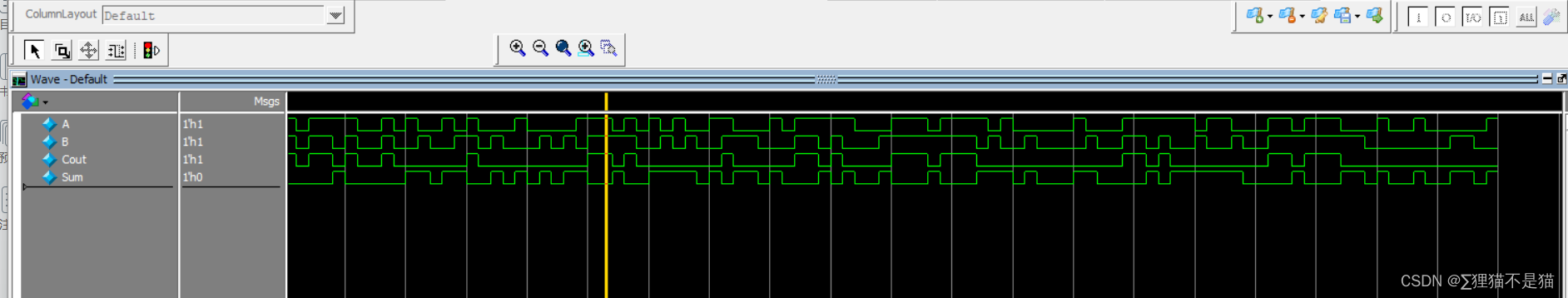

(5)仿真波形:

使用与非门实现功能:

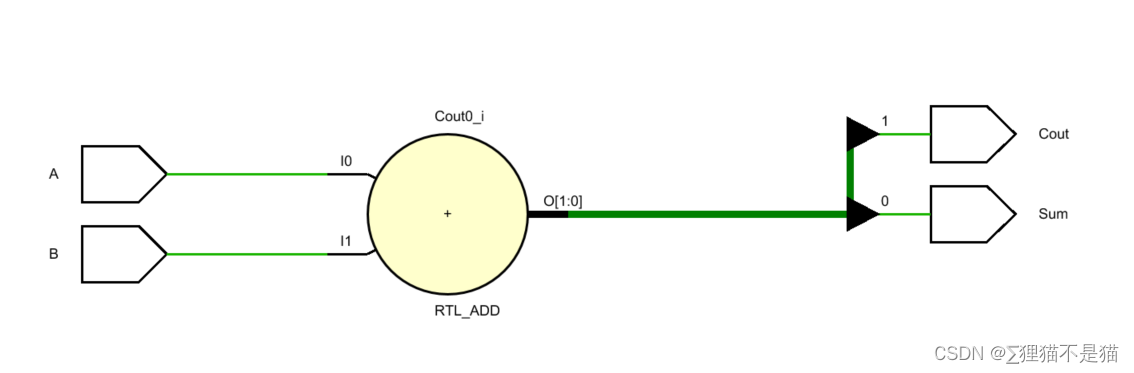

(1)真值表以及分析过程:

(2)Verilog实现代码:

module ex_half_adder(A,B,Cout,Sum);

input A;

input B;

output Cout;

output Sum;

assign Cout = !(!(A & B) & 1'd1);

assign Sum = !((!(!(B & 1'd1)& A)) & (!(!(A & 1'd1) & B)));

endmodule(3)仿真文件代码:

`timescale 1ns/1ns

module half_adder_tb;

reg A;

reg B;

wire Cout;

wire Sum;

ex_half_adder ex_half_adder_inst(

.A(A),

.B(B),

.Cout(Cout),

.Sum(Sum)

);

initial begin

A <= 1'd0;

B <= 1'd0;

#2000;

$stop;

end

always #10 A<= {$random} % 2;

always #10 B<= {$random} % 2;

endmodule

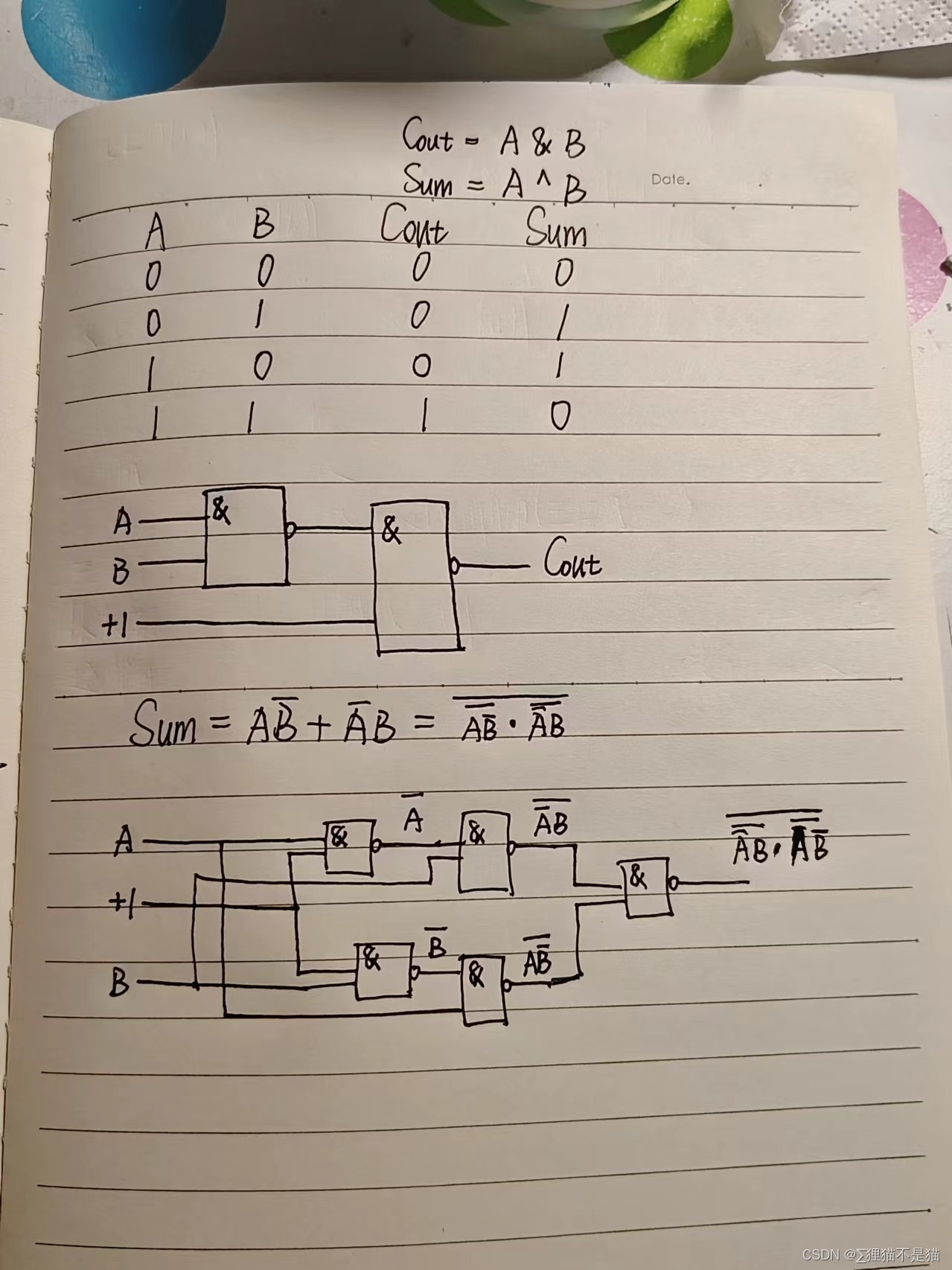

(4)RTL视图:

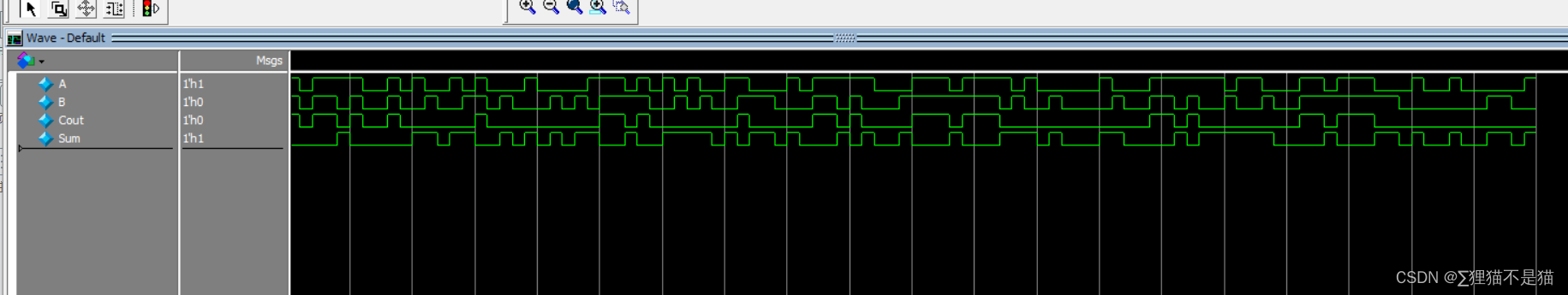

(5)仿真波形:

1068

1068

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?