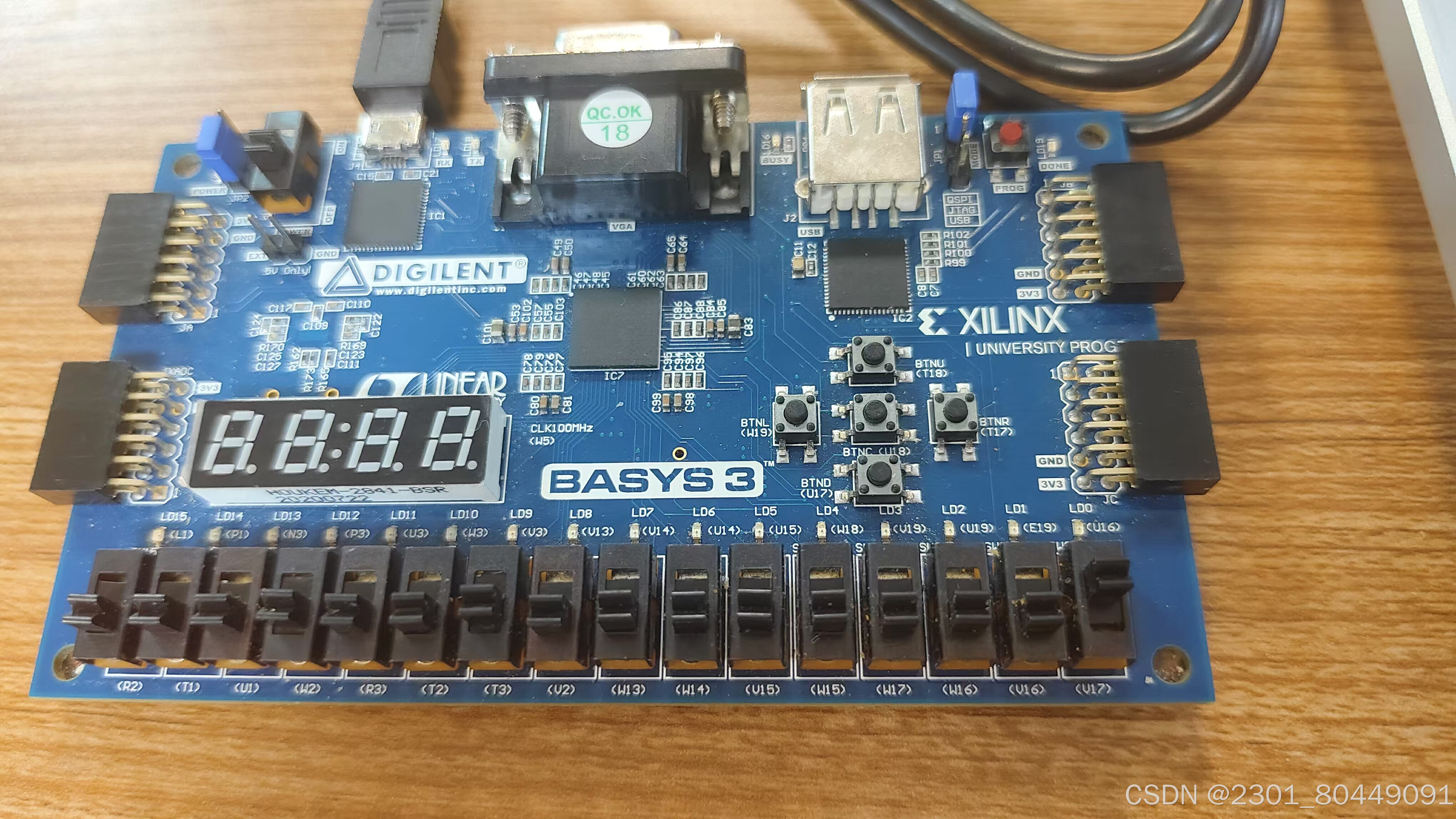

1. 流水灯设计设计

设计要求:实现5位Led灯从左向右循环依次每隔1秒点亮

2.不同频率(hz)实践:

1 不可以,只有最初的一个灯亮,不能流水

2 同上

5 可以

10 可以流水

50 闪烁但是间隔时间变慢相对于100,闪烁的更明显

100 闪烁

500 全都亮

800 全都亮

3.源代码:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/12/19 14:09:49

// Design Name:

// Module Name: FlowingLight

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module FlowingLight(

input wire clk, // 时钟信号

input wire rst, // 复位信号(低电平有效)

output reg [4:0] led // 5位LED灯

);

reg [24:0] counter=0;

always @(posedge clk or posedge rst) begin

if (rst) begin

counter <= 0;

led <= 5'b00001; // 初始状态点亮第一个LED

end else begin

if (counter == 100_000_000/5) begin //

counter <= 0;

led <= {led[3:0], led[4]}; // 循环右移

end else begin

counter <= counter + 1;

end

end

end

endmodule

5.引脚约束

set_property IOSTANDARD LVCMOS33 [get_ports {clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {rst}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[*]}]

set_property PACKAGE_PIN W5 [get_ports {clk}]

set_property PACKAGE_PIN V17 [get_ports {rst}]

set_property PACKAGE_PIN L1 [get_ports {led[0]}]

set_property PACKAGE_PIN N3 [get_ports {led[1]}]

set_property PACKAGE_PIN U3 [get_ports {led[2]}]

set_property PACKAGE_PIN V3 [get_ports {led[3]}]

set_property PACKAGE_PIN V14 [get_ports {led[4]}]

6.疑问:

所以怎么才能实现1s一亮?而且我发现只要周期一大,开发板就实现不了了

808

808

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?