大家好,我是“不做技术”,只做知识分享的知识工蚁。有请本篇文章的主角----电容!本文依旧着重围绕电路设计中,电容的相关选型以及作用展开说明,尽量用最简单的语言讲最深刻的知识。当然,考虑到不同小伙伴的需求不一样,所以跟以往一样自行根据目录选择自己需要的部分。

电容的几个重要身份剧透(带着疑问看文章)

一、电流的"水库管理员"

二、信号世界的"调音师"

三、能量魔术师

四、电路安全卫士

目录

3. 温度系数(Temperature Coefficient)

智能化:嵌入传感器实时监测电容健康状态(如ESR变化预警)。

绿色制造:无铅化、低能耗生产工艺(如水基电解液替代有机溶剂)。

1. 电容的基础概念

1.1 电容的定义与物理意义

电容(Capacitance)是描述导体或导体组合存储电荷能力的物理量。

-

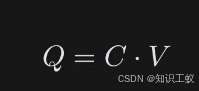

定义:当两个导体之间存在电势差(电压)时,它们能够存储等量异种电荷,电荷量 QQ 与电压 VV 的比值即为电容值 CC,即

-

物理意义:

-

电容的本质是储存电场能。当电荷积累在导体极板之间时,电场随之建立,能量以电场形式存储。

-

电容的大小取决于导体结构(如极板面积 和极板间介质的介电常数 εε,公式为:

-

类比理解:电容类似于“电荷容器”,类似于水箱储水——电压对应水位高度,电容值对应水箱容量。

-

1.2 电容的结构与符号表示

-

典型结构:

-

平行板电容器:由两块平行金属板及中间绝缘介质(如空气、陶瓷、塑料)构成,是最简单的电容模型。

-

实际电容类型:

-

电解电容:使用金属箔(阳极)+ 电解质(阴极),具有极性,容量大但高频性能差。

-

陶瓷电容:无极性,体积小,高频特性优异。

-

薄膜电容:以塑料薄膜为介质,稳定性高,适用于精密电路。

-

-

-

电路符号:

-

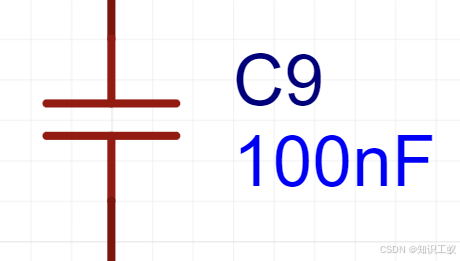

无极性电容:两条平行短线表示极板,如:

-

──| |──

-

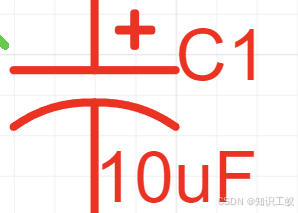

极性电容(如电解电容):符号中标注正负极,如:

──|(+)──

-

1.3 电容的单位与量纲

-

国际单位:法拉(Farad,符号 F)。

-

1 法拉定义为:当电容两端电压为 1 伏特时,存储的电荷量为 1 库仑(1 F=1 C/V1F=1C/V)。

-

-

常用单位换算:

-

-

量纲分析:

-

电容的量纲为

,即电荷与电压的比值。

,即电荷与电压的比值。

-

1.4 电容的伏安特性与基本公式

-

静态特性:电容的电荷量与电压成正比,即:

-

-

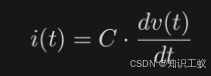

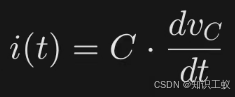

动态特性:电容的电流与电压变化率相关,即

-

-

关键结论:

关键结论:

-

电容电流由电压的变化速率决定。在直流稳态下,

,电容等效为开路。

,电容等效为开路。 -

电压不能突变:电容两端电压的变化需要时间,实际电路中表现为“缓冲”电压突变。

-

-

-

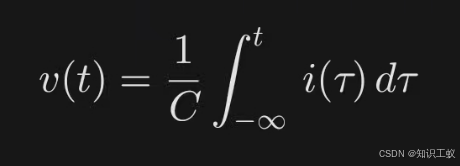

积分形式:电容电压可通过对电流积分得到:

-

2. 电容的核心特性

2.1 电容的充放电过程分析

电容的充放电行为是理解其动态特性的核心。以RC串联电路为例(电源 VSVS、电阻 RR、电容 CC 串联):

充电曲线的数学推导

-

初始条件:电容初始电压 Vc(0)=0,开关闭合后电源对电容充电。

-

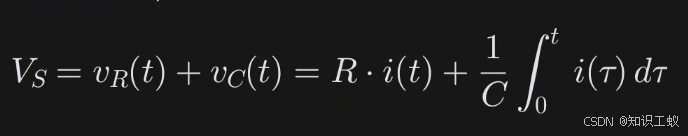

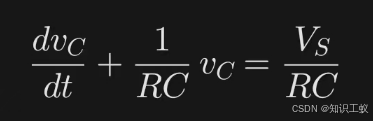

微分方程:根据基尔霍夫电压定律(KVL),电路满足:

-

结合电流公式

,方程化简为:

,方程化简为:

-

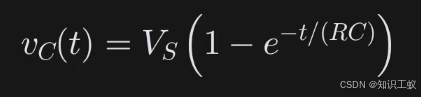

解方程:通过分离变量或一阶线性微分方程解法,得到充电电压表达式:

充电电流为:

-

充电曲线:电压按指数规律上升,电流按指数规律下降。

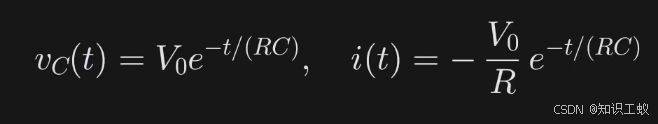

放电曲线的数学推导

-

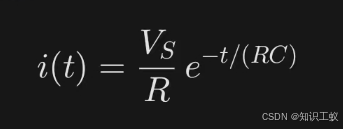

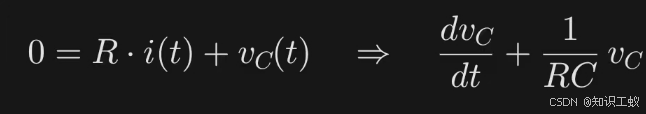

初始条件:电容已充电至 V0V0,断开电源后电容通过电阻放电。

-

微分方程:

-

解方程:放电电压和电流分别为:

-

放电曲线:电压和电流均按指数规律衰减。

时间常数(τ=RC)的物理意义与应用

-

定义:时间常数 τ=RC,单位为秒(s)。

-

物理意义:

-

充放电过程中,经过 τ时间后,电容电压变化至初始值与终值之差的 63.2%(对应 1−e−1≈0.6321−e−1≈0.632)。

-

理论上,充放电需 5τ 时间达到稳态(误差小于 1%)。

-

-

应用:

-

延时电路设计:通过调节 RR 或 CC 控制充放电时间。

-

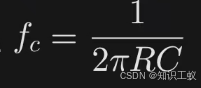

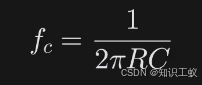

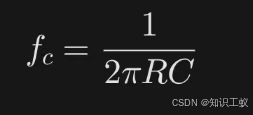

滤波器设计:在RC滤波器中,ττ 决定截止频率

。

。

-

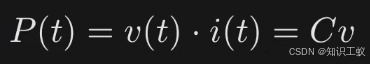

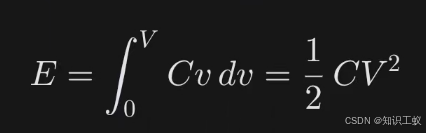

2.2 电容的储能特性与能量计算

-

储能原理:电容通过电场存储能量,能量大小与电压平方成正比。

-

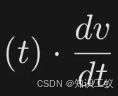

能量公式推导:

电容的瞬时功率为

,

, -

对时间积分得到总能量:

-

关键结论:

-

电容储能与电压的平方成正比,因此高压电容(如超级电容)可存储更多能量。

-

电容放电时释放能量,但实际应用中需考虑内阻(ESR)导致的能量损耗。

-

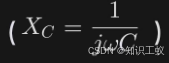

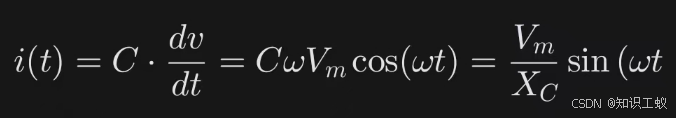

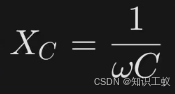

2.3 电容的阻抗特性与频率响应

容抗公式 )的推导

)的推导

-

交流电路中的电容:

设电容两端电压为 ,

, -

则电流为:

其中容抗

。

。 -

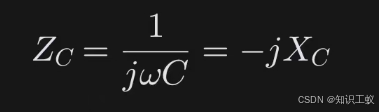

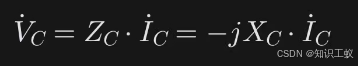

复数形式:在频域分析中,电容的阻抗表示为:

相位关系(电流超前电压90°)

-

物理本质:

-

电容电流由电压变化率驱动,因此电流最大值出现在电压变化最快时(电压过零点),导致电流相位超前电压 90°。

-

-

相量图表示:

-

电压相量 V沿实轴方向,电流相量 I˙沿虚轴正方向。

-

频率响应的实际意义

-

低频:容抗 Xc 极大,电容近似开路(隔直特性)。

-

高频:容抗 Xc 极小,电容近似短路(通交特性)。

-

应用场景:

-

高通/低通滤波器设计。(后面会提到)

-

电源去耦电容需选择容抗小的电容(高频特性好的陶瓷电容)。

-

3. 电容在电路中的应用场景

3.1 滤波电路

电容的滤波功能基于其频率依赖的阻抗特性,广泛应用于信号处理和电源设计中。

低通滤波与高通滤波的原理

-

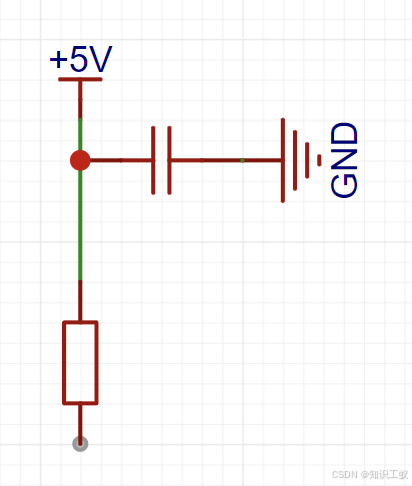

低通滤波器(LPF):

-

结构:由电阻 R和电容 C组成,电容并联在输出端。

-

原理:

-

低频信号:电容容抗 Xc 大,信号主要通过电阻输出,衰减小。

-

高频信号:容抗 Xc 小,高频分量被电容旁路到地,输出衰减大。

-

-

截止频率:

-

频率低于 fc的信号通过,高于 fc 的信号被抑制。

-

-

-

高通滤波器(HPF):

-

结构:电容 C与电阻 R串联,电阻并联在输出端。

-

原理:

-

高频信号:容抗 Xc小,信号主要通过电容输出。

-

低频信号:容抗 Xc大,低频分量被电容阻隔,输出衰减大。

-

-

截止频率:与低通滤波器公式相同,但功能相反。

-

电源去耦电容的作用

-

问题背景:数字电路中,芯片开关瞬间产生高频电流波动,导致电源电压抖动(噪声)。

-

解决方案:在电源引脚附近并联去耦电容(通常为0.1μF陶瓷电容)。

-

高频旁路:电容对高频噪声呈现低阻抗,将噪声直接短路到地。

-

储能缓冲:为芯片瞬时大电流需求提供局部能量补充,避免电源线电压跌落。

-

3.2 耦合与隔直电路

-

耦合电容:

-

功能:传递交流信号,阻隔直流分量。

-

应用场景:多级放大器中,前级输出与后级输入的连接。

-

电容阻隔前级的直流偏置电压,仅传递交流信号,避免后级工作点偏移。

-

-

容量选择:需满足 XC≪R负载 在最低工作频率处,通常选择几μF至几十μF的电解电容。

-

-

隔直电容:

-

功能:阻止直流信号通过,仅允许交流分量传输。

-

典型应用:音频信号输入端的隔直电容,消除直流偏移对扬声器的损害。

-

3.3 储能与能量缓冲

-

开关电源中的电容:

-

输入滤波电容:平滑整流后的脉动直流电压,减小纹波。

-

输出储能电容:在开关管关闭期间为负载提供持续电流,降低输出电压波动。

-

选型关键:需兼顾容量(储能)和ESR(减少损耗),常采用铝电解电容或固态电容。

-

-

超级电容的应用:

-

瞬时功率支撑:如电机启动时提供大电流,弥补电池输出不足。

-

能量回收:在制动系统中存储回收的能量。

-

3.4 定时与振荡电路

-

RC定时电路:

-

原理:利用电容充放电时间控制延时或脉冲宽度。

-

典型应用:555定时器中的充电阈值控制。

-

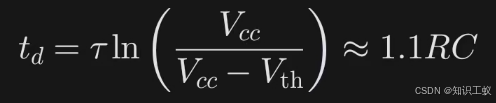

延时时间:

-

-

-

RC振荡器:

-

原理:电容充放电与比较器结合,生成方波或三角波。

-

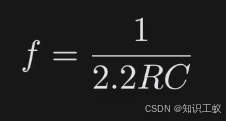

频率公式:

-

3.5 电容在交流电路中的行为(相量分析)

-

相量模型:

-

电容阻抗表示为复数形式 Zc=1/jωc=−jXc。

-

电压与电流的相量关系:

-

-

功率特性:

-

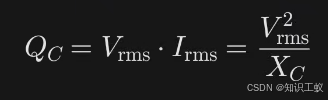

无功功率:电容不消耗能量,仅与电源交换能量,无功功率为:

-

-

实际应用:

-

功率因数校正:利用电容补偿感性负载的无功功率。

-

谐振电路:与电感组成LC谐振回路,用于选频或能量传输。

-

案例1:设计RC低通滤波器

目标:设计一个截止频率 fc=1 kHzfc=1kHz 的低通滤波器,用于滤除信号中的高频噪声。

步骤1:确定滤波参数

-

截止频率公式:

-

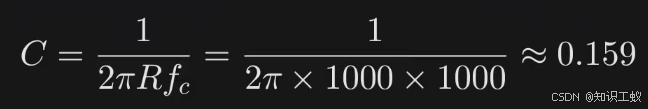

选择电阻或电容值: 单位μF

-

若选择电阻 R=1 kΩR=1kΩ,则电容值为:

-

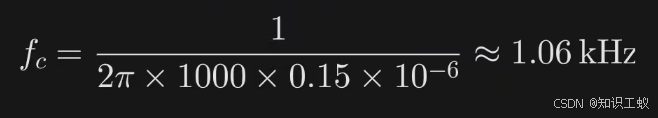

标准化取值:选择 C=0.15 μFC=0.15μF(常见容值),重新计算实际截止频率:

-

步骤2:元件选型与布局

-

电阻选择:

-

精度:1% 金属膜电阻(保证频率准确性)。

-

-

电容选择:

-

类型:陶瓷电容(高频性能好,如X7R材质)。

-

耐压:至少为输入信号峰峰值的2倍(如信号为5V,选10V以上)。

-

-

PCB布局要点:

-

电容尽量靠近信号输入/输出端,缩短走线以减少寄生电感。

-

避免平行走线引入串扰。

-

步骤3:仿真验证(以LTspice为例)

-

搭建仿真电路(电源 + 电阻 + 电容 + 负载)。

-

设置交流扫描分析(AC Analysis),频率范围:10 Hz – 100 kHz。

-

观察幅频特性曲线,确认截止频率是否接近设计值。

步骤4:实际测试

-

信号源输入:使用函数发生器输入正弦波(如 Vpp=5 VVpp=5V)。

-

示波器测量:

-

输入信号(CH1)与输出信号(CH2)对比。

-

验证1 kHz信号衰减为输入幅度的70.7%(-3 dB点)。

-

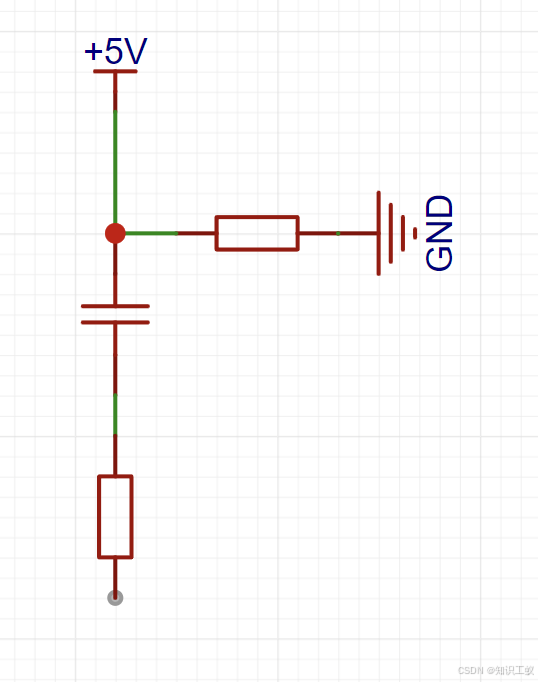

案例2:电源去耦电容设计

目标:为5V数字电路芯片(如MCU)设计去耦电容,抑制高频噪声。

步骤1:确定电容类型与容值

-

高频去耦:选择0.1 μF陶瓷电容(X7R或NP0材质),抑制10 MHz以上噪声。

-

低频储能:并联10 μF电解电容,补偿低频电流波动。

步骤2:布局与布线规则

-

电容位置:

-

0.1 μF电容尽量靠近芯片电源引脚(走线长度 < 5 mm)。

-

10 μF电容可稍远,但需在同一电源平面上。

-

-

过孔与回路:

-

电源与地引脚通过多个过孔连接,降低阻抗。

-

避免形成大环路,减少电磁辐射。

-

步骤3:测试与调试

-

噪声测量:

-

使用示波器探头(带宽 > 100 MHz)测量电源引脚噪声。

-

对比有无去耦电容时的噪声峰峰值(目标:< 50 mV)。

-

-

问题排查:

-

若高频噪声残留,可增加0.01 μF陶瓷电容进一步滤波。

-

若电压跌落明显,检查电容ESR是否过高(更换低ESR电容)。

-

案例3:RC延时电路设计

目标:设计一个延时 td=10 mstd=10ms 的RC电路,用于触发后续电路动作。

步骤1:计算R与C值

-

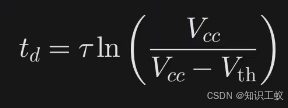

延时公式:

简化得:

-

参数选择:

-

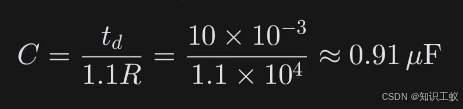

若选 R=10 kΩR=10kΩ,则:

-

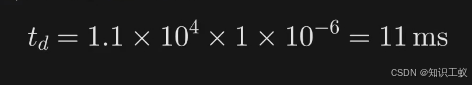

标准化取值:选择 C=1 μFC=1μF 电解电容,实际延时为:

-

步骤2:电路搭建

-

元件连接:

-

电阻与电容串联,连接至电源 Vcc。

-

电容另一端接地,电阻与电容连接点接比较器输入。

-

-

比较器阈值设置:

-

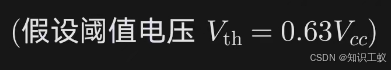

根据需求调整阈值电压(如 Vth=0.63Vcc)。

-

步骤3:验证与调整

-

示波器观测:

-

测量电容充电曲线,确认延时时间是否符合预期。

-

-

容差处理:

-

若电容容差为±20%,可通过调节电阻值微调延时(如更换为可调电阻)。

-

实际设计中的常见问题与解决

-

电容极性接反:

-

现象:电解电容发热甚至爆裂。

-

解决:严格检查极性符号,或改用无极性电容。

-

-

高频自谐振:

-

现象:电容在特定频率下阻抗突增(因寄生电感与电容谐振)。

-

解决:并联不同容值电容(如0.1 μF + 10 μF)覆盖更宽频段。

-

-

温度影响:

-

现象:陶瓷电容容值随温度变化(如Y5V材质容值漂移±80%)。

-

解决:选择温度稳定性好的材质(如X7R、NP0)。

-

4. 电容的串并联分析与等效模型

电容的串并联分析与等效模型是电路设计中优化电容性能、解决实际问题的关键。本节将深入探讨电容的组合特性、非理想参数的影响以及实际电容与理想模型的差异。

4.1 电容串联与并联的等效电容计算

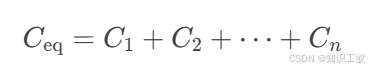

电容并联

-

等效电容:并联电容的总容量为各电容值之和,类似于增加“储电荷的容器”的总容积。

-

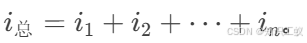

电压与电流分配:

-

所有并联电容的电压相同,由外电路电压决定。

-

总电流为各电容电流之和,满足

-

-

应用场景:

-

扩展容量:如电源滤波中通过并联多个电容提高总储能。

-

降低等效ESR:多个电容并联可减少整体等效串联电阻(ESR),提高高频性能。

-

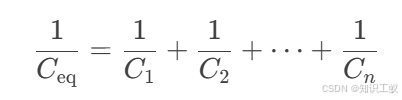

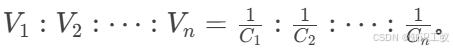

电容串联

-

等效电容:串联电容的等效电容小于任一单独电容值,类似于增加极板间距。

-

电压分配:

-

各电容的电压与其容量成反比,即

-

总电压为各电容电压之和:

-

-

应用场景:

-

高压分压:串联电解电容以承受更高电压(需并联均压电阻防止电压不均衡)。

-

精密调容:通过串联微调总容量(较少使用,优先选择并联)。

-

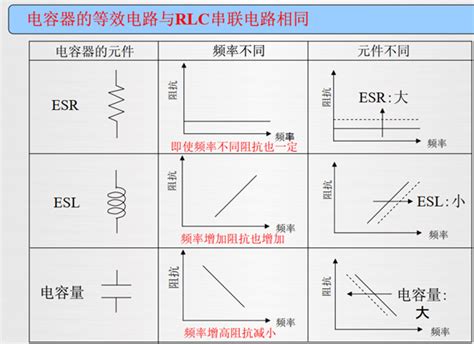

4.2 电容的等效串联电阻(ESR)与寄生电感(ESL)

等效串联电阻(ESR)

-

定义:ESR是电容内部金属电极、引线和介质的等效电阻,与电容串联存在。

-

影响:

-

能量损耗:ESR会导致电容充放电时发热,降低效率(尤其在开关电源中)。

-

滤波性能:ESR越大,高频噪声抑制能力越差(去耦电容需选择低ESR型号)。

-

-

测量与选型:

-

数据手册标注:ESR随频率升高而降低,典型值在几mΩ(陶瓷电容)至几Ω(电解电容)。

-

实际测试:可通过阻抗分析仪或测量电容充放电波形计算ESR。

-

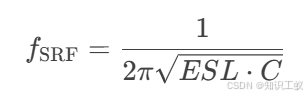

寄生电感(ESL)

-

来源:由电容内部结构和外部引线引入的微小电感,与电容串联。

-

影响:

-

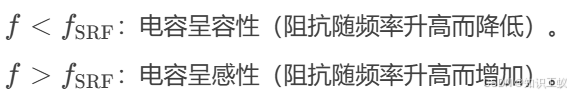

自谐振频率(SRF):电容与ESL形成LC谐振回路,在SRF处阻抗最小,超过SRF后呈现感性。

-

高频失效:当工作频率超过SRF时,电容失去容性,无法有效滤波。

-

-

降低ESL的方法:

-

选择贴片电容(缩短引线长度)。

-

使用多电容并联覆盖宽频段(如0.1 μF + 10 μF组合)。

-

4.3 实际电容与理想电容的差异

实际电容受材料、工艺和环境因素影响,与理想模型存在显著差异,主要体现在以下几个方面:

1. 频率依赖性

-

容量衰减:高频下介质极化滞后,有效容量下降(尤其电解电容)。

-

阻抗特性:实际电容的阻抗由容抗、ESR和ESL共同决定。

2. 温度影响

-

容量漂移:陶瓷电容(如Y5V)容量随温度变化可达±80%,而NP0材质仅±0.03%。

-

ESR变化:电解电容在低温下ESR显著增大(影响电源启动性能)。

3. 老化与寿命

-

电解电容电解液干涸:长期使用后容量下降,ESR增大,寿命通常为几千至几万小时。

-

薄膜电容稳定性:聚酯薄膜电容老化率低,适合长寿命应用。

4. 电压依赖性

-

陶瓷电容容量压降:施加直流电压后,部分材质(如X7R)容量可能下降20%~50%。

5. 漏电流

-

介质漏电:实际电容存在微小漏电流(电解电容漏电流较大),影响高阻电路设计。

实际案例:电源滤波电容的选型分析

目标:为12V开关电源输出端选择滤波电容,要求输出纹波 < 50 mV,工作频率100 kHz。

-

容量计算:

-

根据纹波公式 V纹波=I负载2πfCV纹波=2πfCI负载,假设负载电流1A,需 C≥32 μFC≥32μF。

-

-

ESR要求:

-

纹波电压同时受ESR影响:V纹波=I纹波⋅ESRV纹波=I纹波⋅ESR。

-

若允许ESR贡献20 mV纹波,则要求 ESR<20 mΩESR<20mΩ。

-

-

选型方案:

-

并联1颗100 μF低ESR电解电容(ESR=50 mΩ) + 2颗10 μF陶瓷电容(ESR=5 mΩ)。

-

等效ESR:

,满足要求。

,满足要求。

-

补充参考

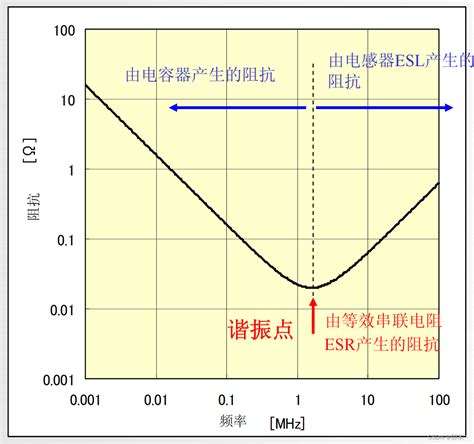

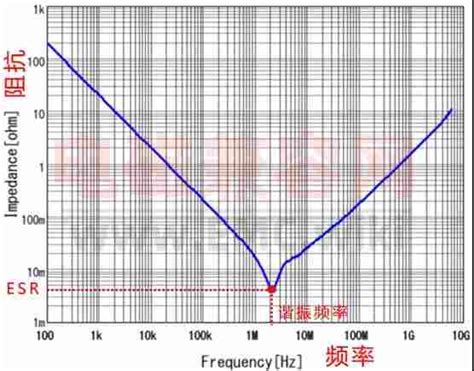

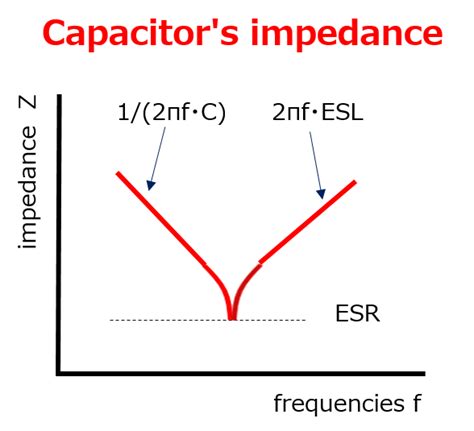

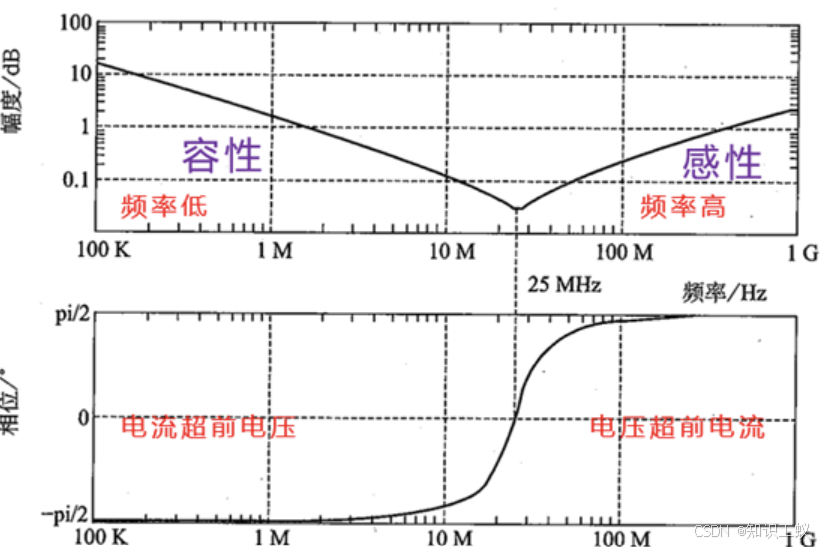

1. 电容阻抗-频率曲线的基本构成

电容的阻抗-频率曲线主要由三个部分组成:

- 容性区域:在低频段,电容表现为容性,阻抗随频率增加而减小,表现为负实部。

- 谐振点:在特定频率下,电容的总阻抗达到最小值,此时阻抗表现为纯电阻性,该频率称为谐振频率。

- 感性区域:在高频段,电容表现为感性,阻抗随频率增加而增大,表现为正实部。

SIwave中文培训手册-高性能PCB 的 SI/PI 和EMI/EMC 仿真设计 - 知乎

2. 影响电容阻抗-频率曲线的因素

电容的阻抗不仅由其标称容值决定,还受到寄生参数(ESR和ESL)的影响:

2.1 ESR(等效串联电阻)

- 作用:ESR是电容内部导线和极板之间的电阻,它会导致电容在低频段表现出一定的阻尼效果。

- 影响:ESR越大,电容的阻抗越高,尤其是在低频段。ESR的存在使得电容在低频时表现为容性,但在高频时表现为感性。

2.2 ESL(等效串联电感)

- 作用:ESL是电容内部导线和极板之间的电感,它会在高频段引入额外的感性成分。

- 影响:ESL越大,电容的阻抗越高,尤其是在高频段。ESL的存在使得电容在高频时表现为感性。

2.3 C(电容值)

- 作用:C是电容的标称容值,决定了电容在中频段的阻抗特性。

- 影响:电容值越大,谐振频率越低;电容值越小,谐振频率越高。

硬件基础元器件【2.电容篇】_电容等效模型-CSDN博客

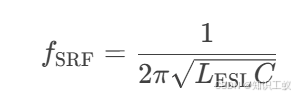

3. 谐振频率的计算

谐振频率 frfr 可以通过以下公式计算:

fr=12πLCfr=2πLC1

其中:

- LL 是等效串联电感(ESL)

- CC 是电容值

在谐振点,电容的总阻抗最小,表现为纯电阻性。

4. 电容阻抗-频率曲线的特点

4.1 低频段

- 在低频段,电容主要表现为容性,阻抗随频率增加而减小。

-

ESR和ESL的影响较小,电容的阻抗主要由其标称容值决定。

4.2 谐振点

- 在谐振频率处,电容的总阻抗达到最小值,表现为纯电阻性。

- 此时,ESR和ESL的影响达到平衡。

4.3 高频段

- 在高频段,电容主要表现为感性,阻抗随频率增加而增大。

- ESL的影响逐渐显著,导致电容的阻抗增加。

电容的特征阻抗曲线的理解 - www.EMC.wik… emc.wiki

5. 实际应用中的考虑

5.1 滤波器设计

- 在滤波器设计中,选择低ESR和低ESL的电容可以提高滤波效果。

- 大容量电容通常具有较低的ESR和ESL,适合用于低频滤波;小容量电容则适合用于高频滤波。

5.2 并联使用

- 当多个电容并联时,总阻抗会减小,但谐振频率不变。

- 并联使用多个小容量电容可以降低ESR和ESL的影响,从而提高整体性能。

5.3 串联使用

- 当多个电容串联时,总阻抗会增加,但谐振频率不变。

- 串联使用多个大容量电容可以提高总电容量,但ESR和ESL的影响仍然存在。

Basic Knowledge of LC Filters - Panasonic

6. 仿真与优化

通过仿真工具(如LTspice)可以直观地观察电容的阻抗-频率曲线,并优化电路设计。例如:

- 调整电容值、ESR和ESL以达到所需的阻抗特性。

- 使用多级并联或串联组合来扩展滤波频带。

-

注意:电容的阻抗-频率曲线是由其标称容值、ESR和ESL共同作用的结果。理解这一特性对于电路设计至关重要,尤其是在滤波器设计、去耦电路和高频电路中。通过合理选择电容参数和优化电路结构,可以有效提高电路的性能和稳定性。

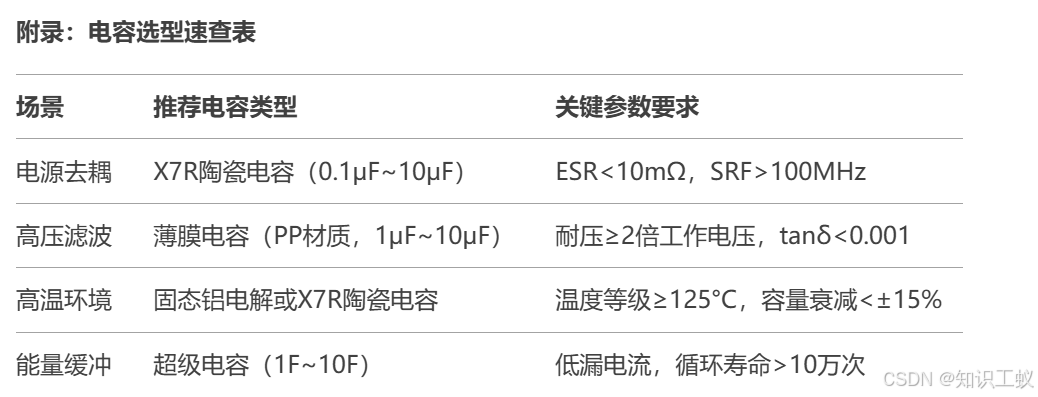

5. 电容的分类与选型指南

电容的选型直接影响电路性能与可靠性。本节将系统解析常见电容类型、关键参数及选型策略,帮助工程师在不同场景下做出最优选择。

5.1 常见电容类型及其特点

| 电容类型 | 结构特点 | 优点 | 缺点 | 典型应用场景 |

|---|---|---|---|---|

| 陶瓷电容 | - 以陶瓷为介质,多层堆叠结构 - 无极性,贴片封装为主(如0805、0603) | - 体积小,高频性能好(低ESR/ESL) - 成本低,温度稳定性可选(NP0/X7R/Y5V) | - 容量小(pF~μF级) - 直流偏压下容量可能下降 | 高频滤波(去耦)、振荡电路、信号耦合 |

| 铝电解电容 | - 铝箔阳极 + 电解液 + 氧化层 - 有极性,圆柱形或贴片封装 | - 容量大(μF~mF级) - 耐压高(可达500V) | - 高频性能差(ESR高) - 寿命有限(电解液干涸) | 电源滤波、低频储能、能量缓冲 |

| 钽电解电容 | - 钽金属阳极 + 二氧化锰电解质 - 有极性,贴片或直插封装 | - 体积小,容量密度高 - ESR低于铝电解 | - 耐压较低(一般<50V) - 价格高,过压易失效 | 精密电源滤波、便携设备储能 |

| 薄膜电容 | - 金属化聚酯(PET)或聚丙烯(PP)薄膜 - 无极性,轴向或盒式封装 | - 容量稳定,损耗低(tanδ小) - 耐高压、寿命长 | - 体积较大 - 高频性能一般 | 交流滤波、电机驱动、谐振电路、安规电容 |

| 超级电容 | - 双电层结构(活性炭电极 + 电解液) - 无极性,圆柱或方型封装 | - 容量极大(法拉级) - 充放电循环寿命长 | - 耐压低(通常<5V) - 漏电流大 | 备用电源、能量回收、瞬时大电流支撑 |

5.2 电容的关键参数解读

1. 耐压值(Rated Voltage)

-

定义:电容可长期安全工作的最大直流电压,超过此值可能导致介质击穿。

-

选型规则:实际工作电压 ≤ 80% 额定电压(留余量应对瞬态电压尖峰)。

2. 容量误差(Tolerance)

-

常见等级:±1%(精密电路)、±5%、±10%、±20%(通用场景)。

-

影响:容量偏差可能导致滤波器截止频率偏移或定时电路精度下降。

3. 温度系数(Temperature Coefficient)

-

定义:容量随温度变化的比率,单位为ppm/°C(百万分之一每摄氏度)。

-

NP0/C0G:±30ppm/°C(超稳定,适用于振荡器)。

-

X7R:±15%容量变化(-55°C~125°C)。

-

Y5V:+22%/-82%容量变化(-30°C~85°C,慎用)。

-

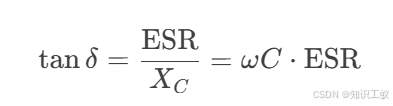

4. 损耗角正切(tanδ)

-

定义:电容等效串联电阻(ESR)与容抗的比值,反映能量损耗。

-

意义:tanδ越小,电容效率越高(薄膜电容tanδ<0.001,铝电解电容tanδ≈0.1~0.2)。

5.3 应用场景与选型建议

高频电路(如射频、高速数字电路)

-

核心需求:低ESR/ESL,高频稳定性。

-

选型方案:

-

优先选择NP0/C0G陶瓷电容(容量稳定,tanδ低)。

-

并联多容值电容(如1nF+10pF)覆盖宽频段,抑制自谐振影响。

-

-

示例:5GHz WiFi模块的去耦电容需使用0402封装的1nF NP0电容。

大电流场景(如开关电源、电机驱动)

-

核心需求:低ESR,高耐流能力。

-

选型方案:

-

铝电解电容(低频储能) + 低ESR陶瓷电容(高频滤波)组合。

-

超级电容用于瞬时大电流补偿(如电机启动)。

-

-

示例:12V/10A开关电源输出端并联1000μF铝电解电容(ESR=50mΩ)和10μF X7R陶瓷电容。

高温环境(如汽车电子、工业设备)

-

核心需求:耐高温、长寿命。

-

选型方案:

-

薄膜电容(PP材质,耐温125°C以上)。

-

固态铝电解电容(无电解液,耐温105°C)。

-

避免使用Y5V陶瓷电容(容量随温度剧烈变化)。

-

-

示例:汽车ECU中的滤波电容选择125°C额定温度的X7R陶瓷电容。

高精度电路(如ADC参考电压、传感器信号链)

-

核心需求:低漏电流、低噪声。

-

选型方案:

-

薄膜电容(如聚丙烯,漏电流<1nA)。

-

NP0陶瓷电容(无压电效应,避免引入噪声)。

-

电容选型误区与避坑指南,速查表

-

盲目追求高容量:高频电路中大容量电解电容可能因ESL过大而失效,需配合小容量陶瓷电容。

-

忽略温度影响:Y5V电容在高温下容量暴跌,可能导致滤波器失效。

-

电压余量不足:电源浪涌电压可能击穿电容,需预留至少20%耐压余量。

-

极性电容反接:钽电容反接5V即可损坏,需严格检查PCB极性标记。

6. 电容相关电路问题的分析与解决

电容在实际电路应用中可能引发多种问题,从性能下降到彻底失效。本节将针对常见问题分析原因并提供解决方案,帮助工程师快速定位与修复故障。

6.1 电容漏电对电路的影响

问题现象:

-

高阻抗节点电压漂移(如传感器信号衰减)。

-

电源电路静态功耗异常升高。

-

储能电容电量快速流失(如备用电池续航缩短)。

原因分析:

-

介质缺陷:陶瓷电容内部裂纹或薄膜电容针孔导致漏电。

-

电解液劣化:铝/钽电解电容老化后漏电流增大。

-

环境湿度:潮湿环境下电容表面漏电(尤其高压电容)。

解决方案:

-

选型优化:

-

高阻抗电路选用薄膜电容(漏电流低至nA级)或NP0陶瓷电容。

-

避免在高温高湿环境使用Y5V等低稳定性电容。

-

-

电路设计:

-

对漏电敏感的信号链路串联保护电阻(限制漏电流路径)。

-

使用Guard Ring技术隔离高阻抗节点(PCB设计)。

-

-

测试验证:

-

用高阻计测量电容漏电流,确保符合数据手册规格。

-

案例:

-

问题:某温度传感器输出信号随时间漂移。

-

排查:检测发现信号耦合电容(10nF陶瓷)漏电流达1μA,远超标称值(<10nA)。

-

解决:更换为聚丙烯薄膜电容,漏电流降至2nA,信号恢复稳定。

6.2 电容老化与寿命问题

老化表现:

-

容量下降(铝电解电容容量减少20%以上)。

-

ESR升高(开关电源输出纹波增大)。

-

漏电流增加(钽电容漏电流超规格)。

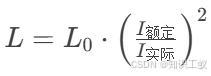

寿命影响因素:

-

温度:电解电容寿命遵循“10°C法则”——温度每升高10°C,寿命减半。

-

电压应力:长期超80%额定电压工作加速介质老化。

-

纹波电流:高频大纹波电流导致内部发热(寿命公式:

)。

)。

延长寿命的措施:

-

降额使用:

-

电压降额:工作电压 ≤ 80% 额定电压。

-

温度降额:实际工作温度 ≤ 电容额定温度 -20°C。

-

-

散热设计:

-

避免电容靠近发热元件(如电感、功率管)。

-

对高纹波电流场景,选择低ESR电容并增加散热孔。

-

-

寿命预测:

-

使用厂商提供的寿命计算工具(如Nippon Chemi-Con的“CapLife”软件)。

-

6.3 电容失效的常见原因

| 失效模式 | 触发条件 | 后果 | 预防措施 |

|---|---|---|---|

| 过压击穿 | 工作电压 > 额定电压 | 介质击穿、短路/爆炸(电解电容) | 增加TVS二极管钳位;选择耐压≥1.5倍工作电压 |

| 过热失效 | 环境温度或纹波电流导致温升超标 | 电解液干涸(容量↓,ESR↑) | 优化散热;限制纹波电流;选用固态电容 |

| 极性接反 | 电解电容正负极反接 | 钽电容冒烟/起火;铝电容鼓包 | PCB极性标注清晰;加装防反接二极管 |

| 机械应力 | 贴片电容PCB弯曲导致开裂 | 内部短路或开路 | 避免电容布局在PCB易变形区域;选择柔性端头电容 |

典型案例:

-

问题:某电源板电解电容爆炸。

-

分析:输入电压瞬态尖峰达35V(电容额定25V),叠加高温环境导致过压击穿。

-

改进:更换为35V耐压电容,并添加36V TVS二极管保护。

6.4 高频电路中的自谐振与规避方法

问题现象:

-

去耦电容在特定频率下滤波失效(阻抗突增)。

-

电路产生意外振荡(如放大器的自激振荡)。

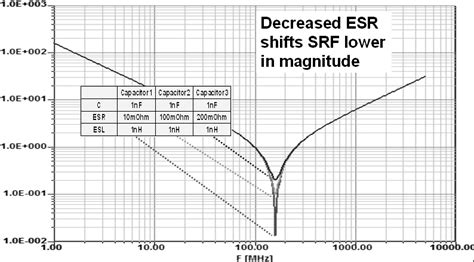

自谐振原理以及自谐振阻抗曲线:

电容的自谐振阻抗曲线可分为容性区、感性区和谐振点三个关键区域,其特性分析如下:

1. 容性区(低频区)

当工作频率低于自谐振频率时,电容主要呈现容性。此时阻抗由电容容抗主导,随着频率增加呈-20dB/dec斜率下降,满足公式 ![]() 。容值越大,容性区阻抗越小,滤波效果越好。

。容值越大,容性区阻抗越小,滤波效果越好。

2. 感性区(高频区)

当频率超过自谐振频率后,等效串联电感(ESL)的影响占据主导,电容表现为感性。此时阻抗随频率上升以+20dB/dec斜率增加,满足 ![]() 。ESL越大,感性区阻抗越大,高频滤波能力越差。

。ESL越大,感性区阻抗越大,高频滤波能力越差。

3. 谐振点(自谐振频率)

在谐振频率点 ![]() ,容抗与感抗相互抵消,总阻抗达到最小值,且表现为纯电阻特性(阻抗值等于等效串联电阻ESR)。此时电容的退耦或滤波效果最佳。

,容抗与感抗相互抵消,总阻抗达到最小值,且表现为纯电阻特性(阻抗值等于等效串联电阻ESR)。此时电容的退耦或滤波效果最佳。

关键特性总结

- 曲线形态:阻抗曲线呈"V"型,最低点对应谐振频率。

- 寄生参数影响:ESR决定谐振点阻抗最小值,ESL和C共同决定谐振频率位置。ESL越大或C越大,谐振频率越低。

- 去耦能力限制:电容仅在谐振频率以下的容性区有效退耦,高频时因感性特性失效。例如0.1μF陶瓷电容自谐振频率约15MHz,无法用于100MHz电路。

多电容并联的特殊现象

当不同容值的电容并联时,可能出现反谐振效应:

- 在中间频段(如大电容已感性、小电容仍容性时),等效为LC并联电路,产生阻抗尖峰(反谐振点)。

- 实际应用中需通过合理选容(如100μF与0.1μF组合)使各电容的谐振频率覆盖目标频段,避免反谐振导致的阻抗恶化。

设计建议

- 选择低ESR和低ESL的电容可拓宽有效滤波频段。

- 高频电路优先选用小封装电容(如0402比0805 ESL更低),并缩短PCB布线以减少附加电感。

- 仿真工具(如SimSurfing)可辅助分析实际电容的阻抗曲线。

自谐振原理:

-

电容的寄生电感(ESL)与自身容量形成LC谐振:

-

阻抗曲线:

-

规避方法:

-

多电容并联:

-

不同容值电容覆盖多个谐振点(如0.1μF+10nF+100pF组合)。

-

-

优化封装:

-

选择低ESL的贴片电容(如0402封装比0805 ESL更低)。

-

-

布局规则:

-

缩短电容引脚/焊盘与电源平面的距离(减少回路电感)。

-

使用地平面作为电流返回路径,降低整体寄生电感。

-

案例:

-

问题:某射频模块在2.4GHz频段噪声抑制不足。

-

分析:去耦电容(1nF,SRF=1.5GHz)在2.4GHz时呈感性,阻抗升高。

-

解决:并联一颗2.2pF电容(SRF=5GHz),高频段阻抗降低60%。

补充:(以下补充的电容并联内容来源于百度贴)

单电容在电子电路中滤除高频干扰信号往往达不到很好的效果,通常可以通过多个电容并联来解决这一问题。

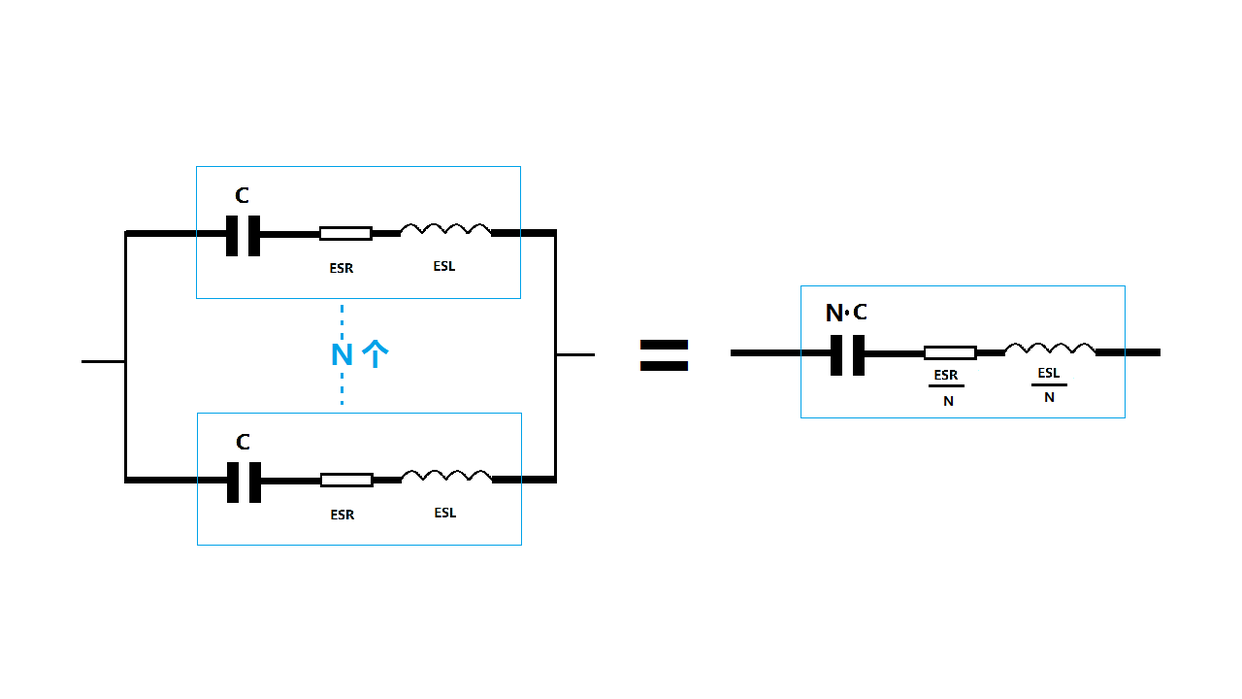

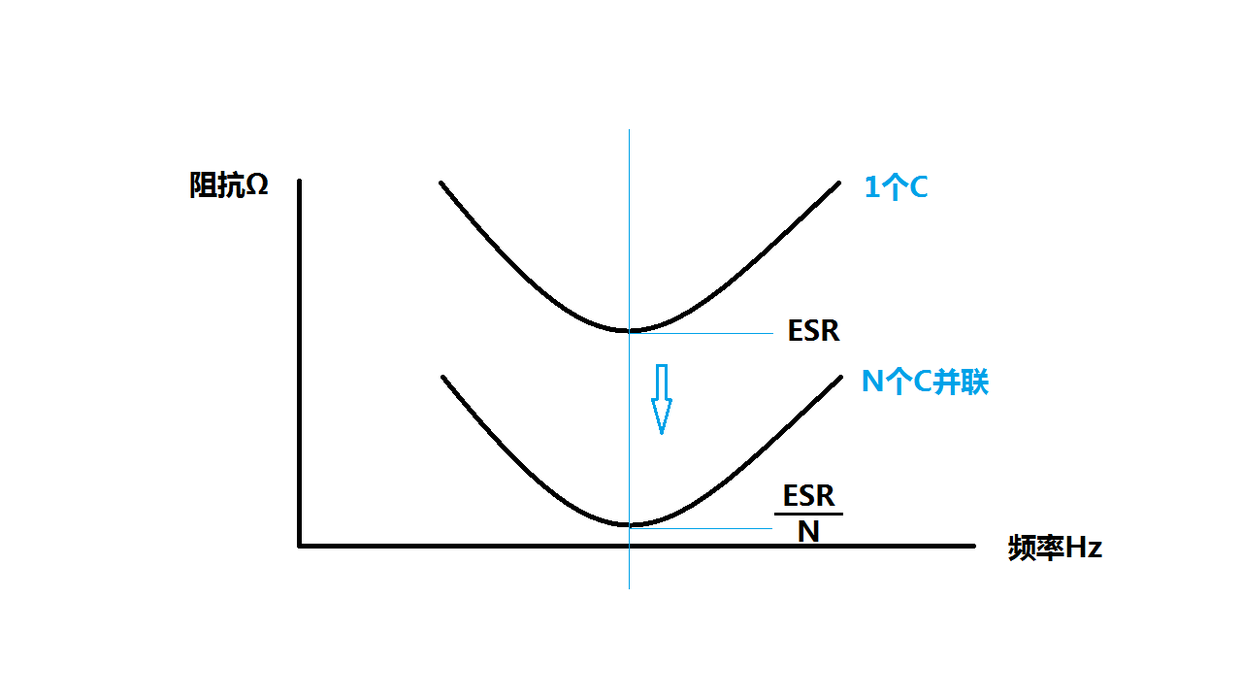

相同电容并联

N个相同电容并联,并联后ESR为原来的1/N,ESL也为原来的1/N,容值为原来的N倍。

相同电容并联后的等效电容

阻抗频率曲线为:

相同电容并联后的频率曲线

多个相同的电容并联后,阻抗频率曲线的整体形状不变,但是各个频率点的阻抗整体下移。

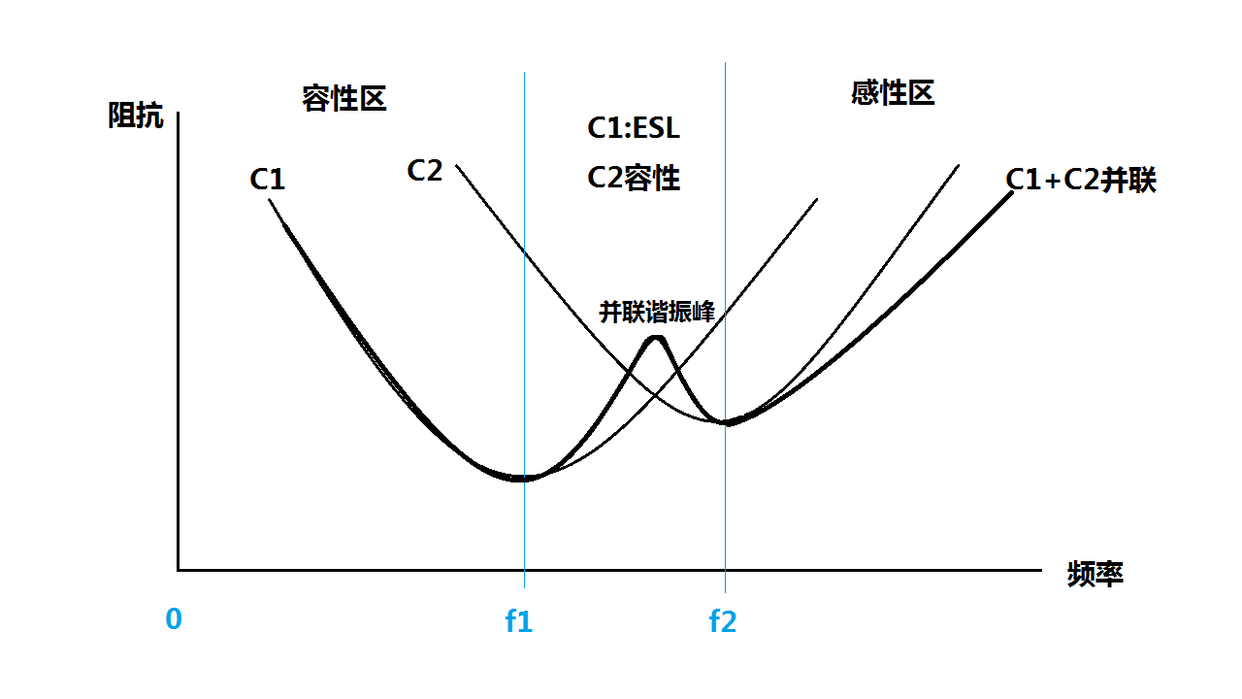

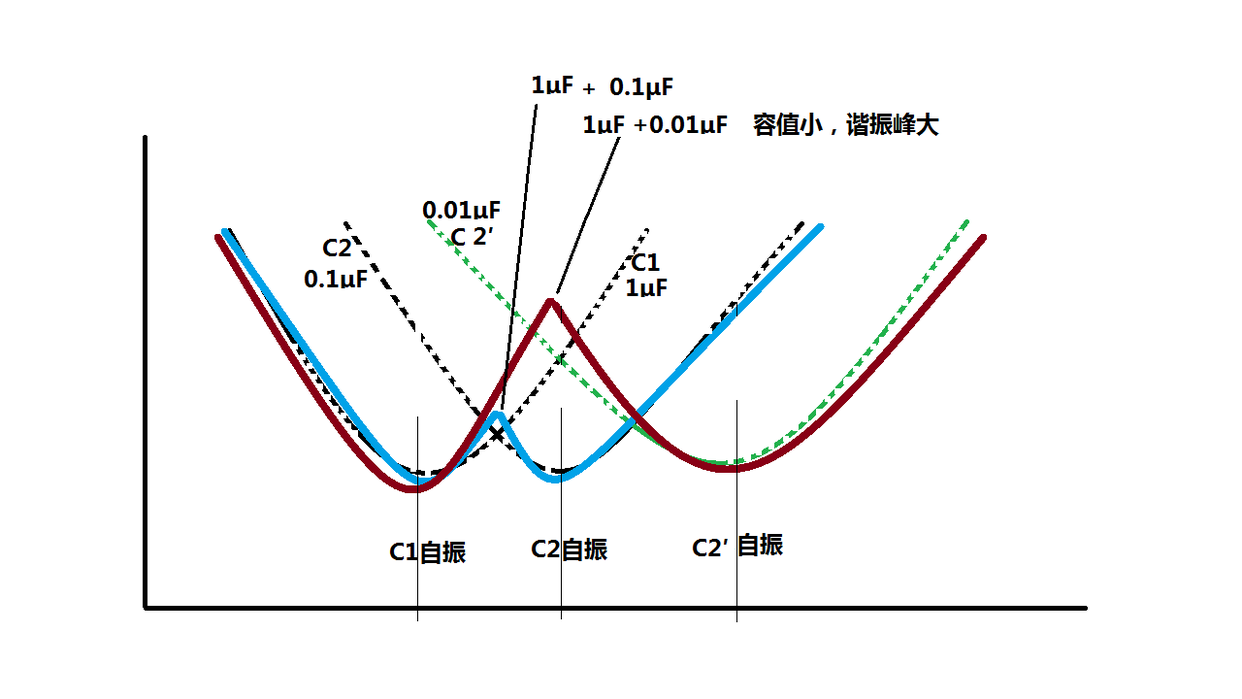

不同电容并联(ESR都较小)

由于每个电容的自谐振频率点不同,两个电容的行为特征存在差异。并联后阻抗频率曲线如下。

不同电容并联

在0—f1,两个电容都表现为容性,总阻抗曲线会保持原来的变化趋势。

在>f2,两个电容都表现为感性,总阻抗会比任意一个电容的稍小。

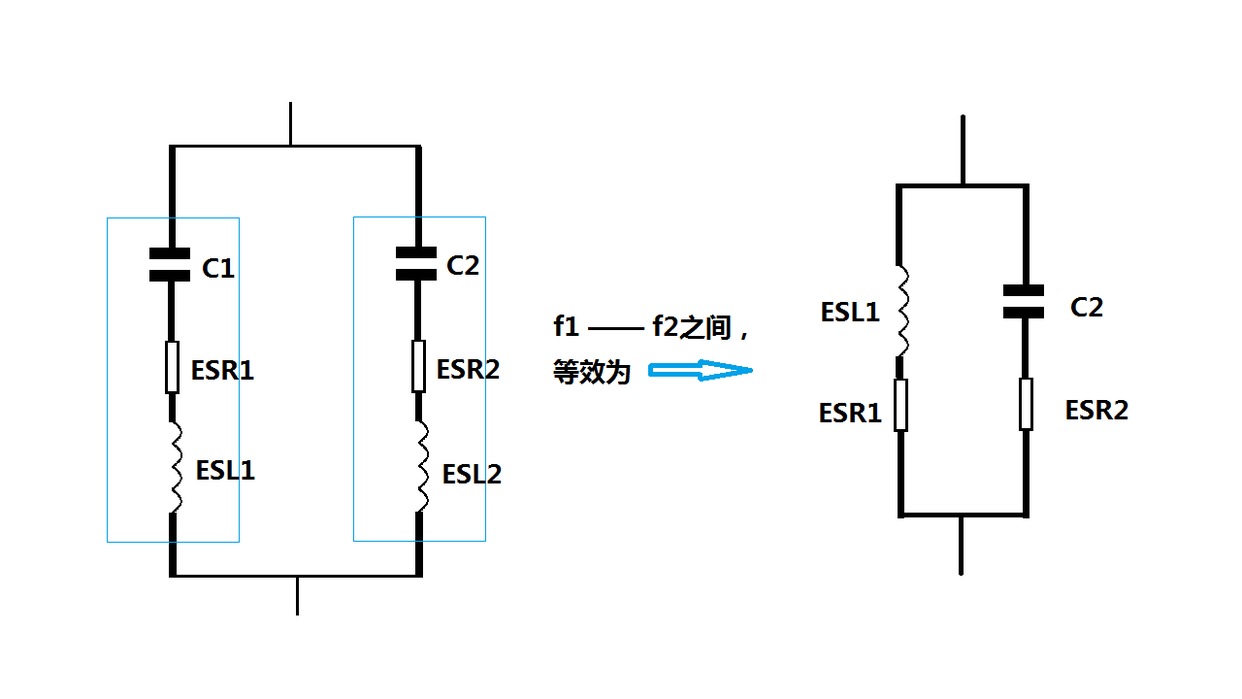

在f1—f2,就像是一个电感和一个电容并联,构成了LC并联谐振电路,会在某个频率点发生并联谐振,阻抗达到区间内最大值,我们称之为并联谐振峰 (位于两条阻抗曲线交叉点附近)。 并联谐振峰也叫作反谐振点,可以理解为是由C1的ESL1和C2形成的。

并联谐振峰处阻抗较大,会影响并联后的滤波效果,那么哪些因素会影响谐振峰值的大小。

在此,两个电容并联可以等效为:

f1f2之间电容并联等效

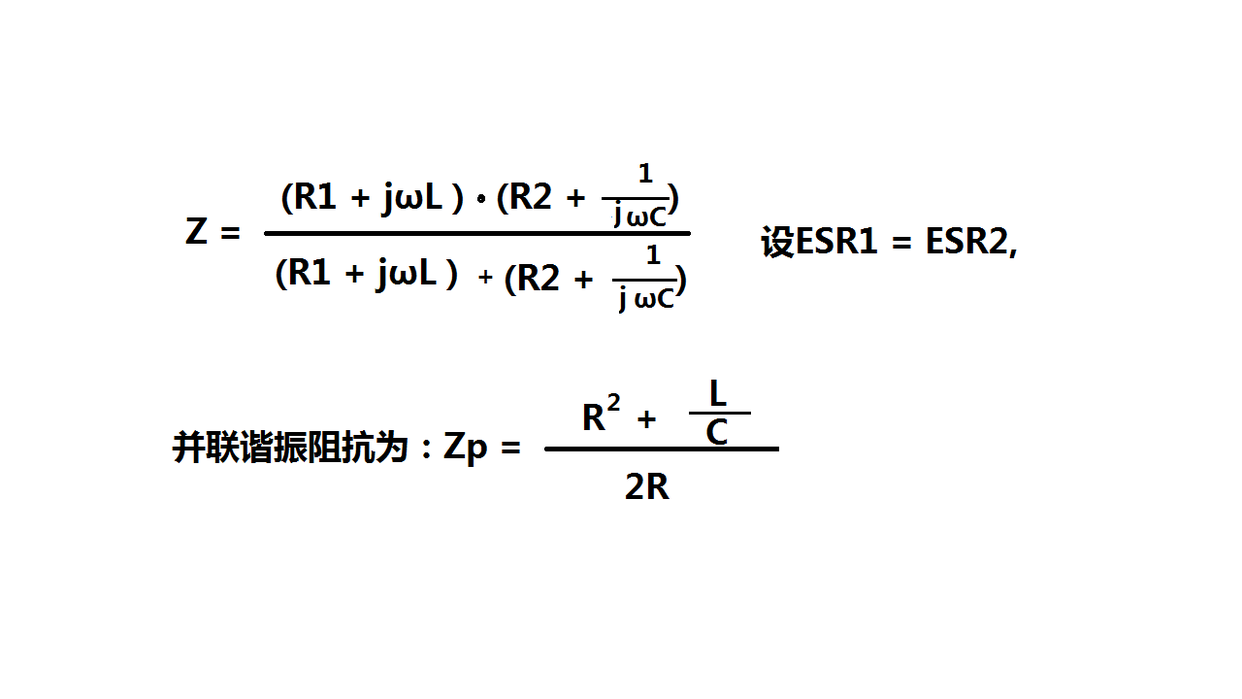

则并联谐振峰公式为:

并联谐振峰计算公式

根据公式可得出以下三个结论:

两电容容值差越大,谐振峰越大

当ESR、ESL(分别代入公式中的R、L)一定时,C2容值越小(在图上表现为两电容的距离越小容差越小)并联谐振阻抗(并联谐振峰)越小。

容差不同电容并联

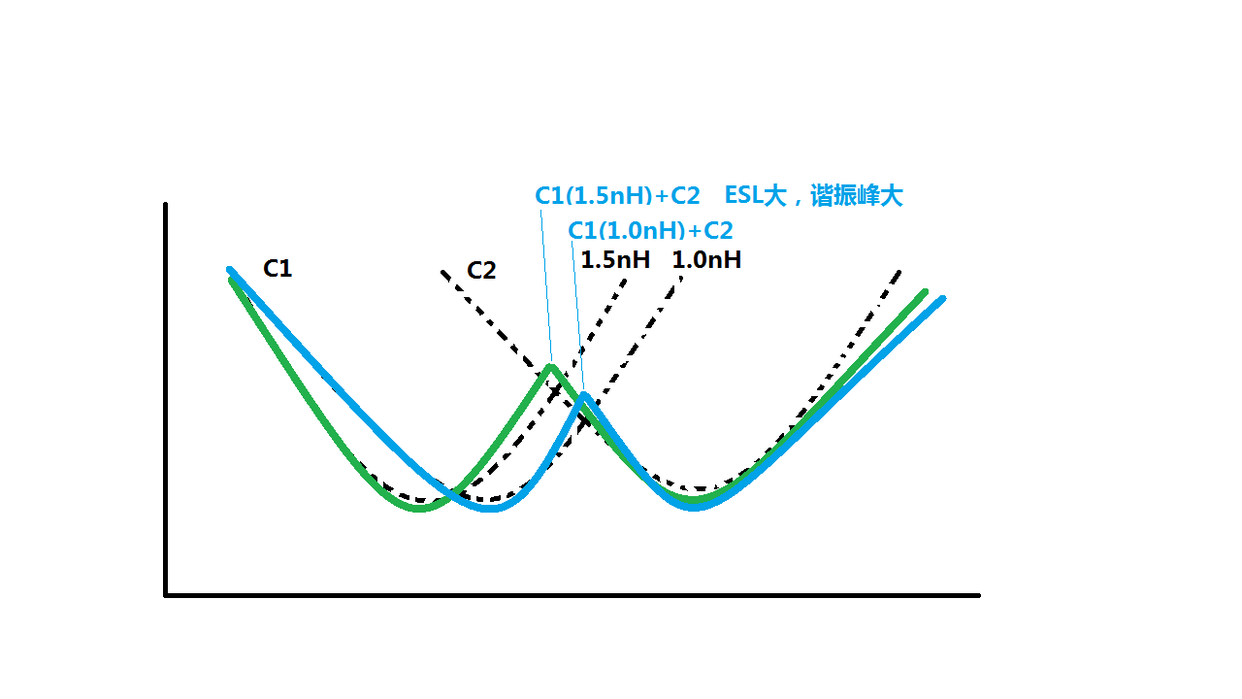

等效串联电感(ESL)越大,谐振峰越大。

当ESR、C2(分别代入公式中的R、C)一定时,ESL1越大并联谐振阻抗(并联谐振峰)越大。

ESL大小对谐振峰的影响

ESL不仅影响电容并联谐振峰值的大小,也影响电容的自谐振频率,ESL变大,使阻抗在自谐振频率点之后增加变快。

ESL越大,并联谐振峰值越大,而且并联谐振频率越低。一方面,由于并联谐振峰值增大,要想满足目标阻抗的要求,需要增加更多的电容;另一方面,由于谐振点向低频移动,为了高频处也能满足目标阻抗的要求,需要增加更多的小电容。

通常电容安装电感会影响ESL变大,所以需要通过一些方法来预防,比如体积大的电容用多个过孔并联,使电源过孔和地过孔尽量靠近,电容尽量靠近芯片的供电引脚减小平面的分布电感等。

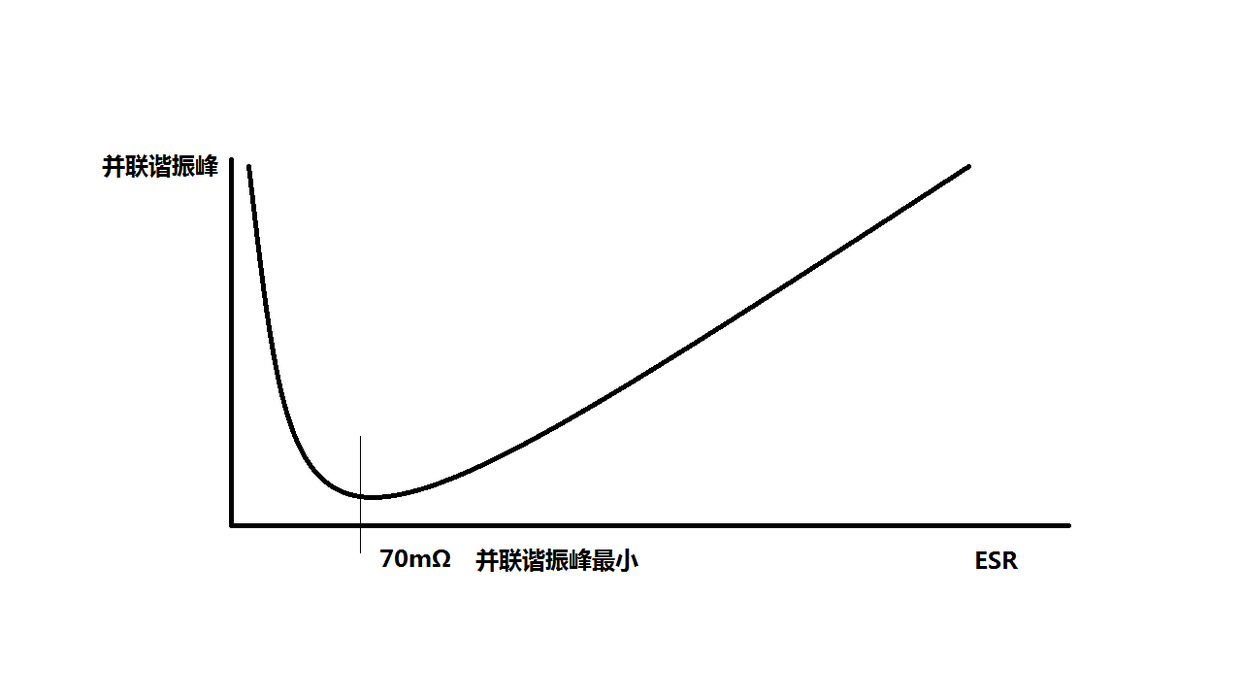

等效串联电阻ESR不宜过大或过小

假设ESL1=0.5nH、C2=0.1uF时,并联谐振峰值Zp与ESR的关系为:

并联谐振峰与ESR

并联谐振峰曲线是一个中间低两头高的形状,所以总有一个中间的ESR值使得并联谐振峰达到最小值,大于或小于此中间值都会使并联谐振峰变大。

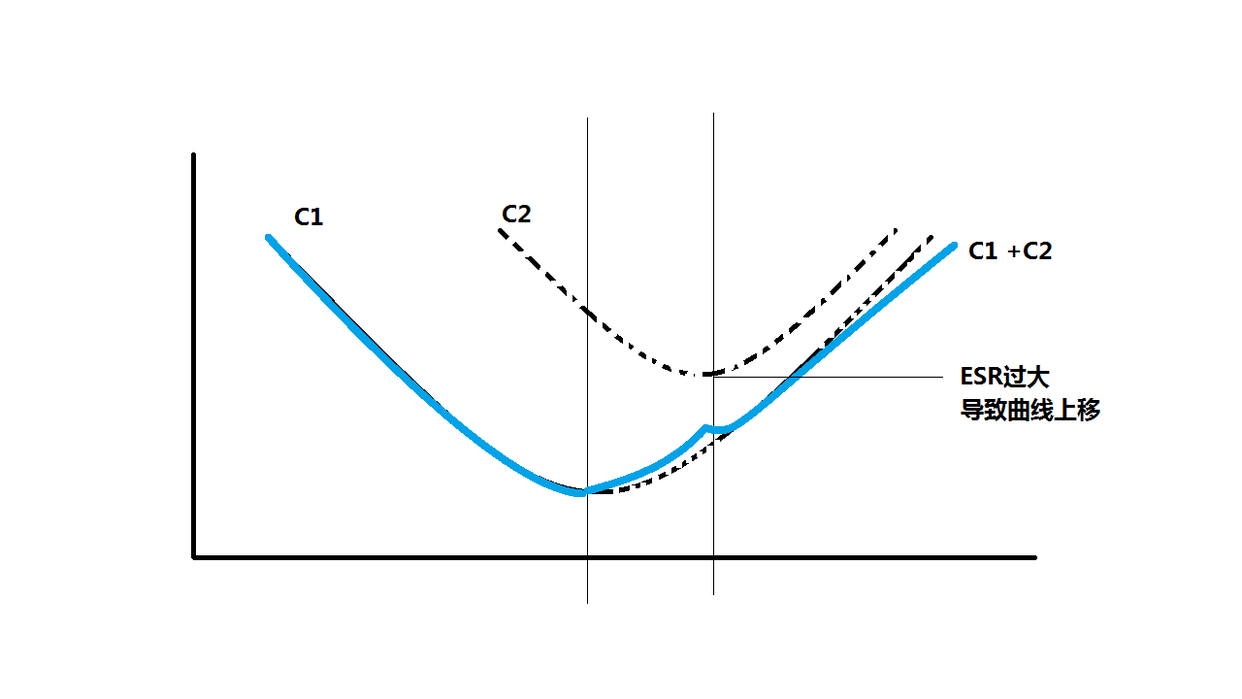

不同电容并联(其中有一个电容ESR过大)

当C2 ESR过大时,阻抗特性曲线可能会落如C1中,此时并不能达到展宽低阻抗频带的目的,电容并联后的曲线与C1的曲线差别不大。

ESR过大并联无效

如果C2为MLCC,ESR会受体积的影响,比如可以将0.01μF 0603更改为0.01μF 0402的封装,或者更换更小ESR的电容,便可让曲线不落入C1中。

7. 电容的未来发展与新技术

7.1 高密度储能电容(如超级电容的应用前景)

超级电容(又称双电层电容器,EDLC)因其高功率密度、快速充放电(秒级)和超长循环寿命(百万次)成为储能领域的重要方向,未来应用前景广阔:

- 技术突破:

- 材料创新:石墨烯、碳纳米管、MXene等新型电极材料可显著提升能量密度(从5-10 Wh/kg向50+ Wh/kg迈进)。

- 混合超级电容:结合电池的高能量密度与电容的高功率密度,例如锂离子电容器(LIC)已在电动汽车中试应用。

- 应用场景:

- 电动汽车:用于能量回收(刹车动能存储)、瞬时加速供电,缓解电池峰值负载压力。

- 电网储能:平抑风光发电的波动性,提供毫秒级频率调节。

- 工业设备:替代传统电池为无人机、机器人提供短时高功率输出。

- 挑战:成本高(石墨烯制备工艺复杂)、低温性能优化、能量密度仍低于锂电池(需突破电极-电解质界面技术)。

7.2 新型介电材料与微型化趋势

电容性能的升级高度依赖介电材料创新与制造工艺突破:

- 材料方向:

- 高介电常数(High-k)材料:钛酸锶钡(BST)、聚合物基纳米复合材料(如P(VDF-TrFE)),提升单位体积电容密度。

- 柔性介电材料:可拉伸聚合物/陶瓷复合材料,支持柔性电子(可穿戴设备、折叠屏手机)。

- 高温稳定材料:氮化铝(AlN)等陶瓷材料,适用于航空航天和车载高温环境。

- 微型化技术:

- 多层陶瓷电容(MLCC) :通过超薄层压技术(层厚<1μm)实现0402/0201封装的小型化,同时容量突破100μF。

- 3D集成电容:在芯片内部堆叠电容结构(如TSV硅通孔技术),减少PCB面积占用。

- 未来趋势:

- 纳米级介电层:原子层沉积(ALD)技术制备纳米氧化层,突破传统击穿电压限制。

- 生物可降解电容:基于纤维素或蛋白质的环保材料,减少电子垃圾污染。

7.3 电容在新能源与电动汽车中的角色

电容技术是新能源革命与电动化转型的核心支撑:

- 电动汽车应用:

- 逆变器滤波:薄膜电容用于IGBT/MOSFET开关噪声吸收,提升电机效率。

- 电池管理系统(BMS) :MLCC为电压监测电路提供高频去耦,防止误触发。

- 快充系统:高压铝电解电容(450-1000V)支撑800V平台超充桩的瞬时能量缓冲。

- 新能源领域:

- 风光储系统:超级电容平抑风光发电的秒级波动,减少对锂电池的频繁充放。

- 氢燃料电池:脉冲功率电容为氢燃料电堆启动提供瞬态电流。

- 创新结合:

- 无线充电系统:谐振电容实现高效磁耦合,推动电动车动态无线充电技术。

- 固态电池兼容电容:固态电解质与电容集成,实现高安全、高响应速度的混合储能单元。

未来展望

- 技术融合:电容将与半导体、电池技术深度整合(如“电容-芯片”一体化封装)。

-

智能化:嵌入传感器实时监测电容健康状态(如ESR变化预警)。

-

绿色制造:无铅化、低能耗生产工艺(如水基电解液替代有机溶剂)。

总结:电容在电路设计中的核心地位

电容作为电子电路中最基础的被动元件之一,其核心地位体现在对电路性能的全局性影响,涵盖能量管理、信号完整性、系统稳定性等多个维度。以下是其关键作用及设计逻辑的深入解析:

1. 能量存储与瞬态响应

- 储能缓冲:电容通过充放电为电路提供瞬时能量补偿,尤其在电源系统中:

- 电源滤波:平滑整流后的脉动直流电压(如铝电解电容用于低频滤波)。

- 负载瞬态响应:在CPU或功率器件突发电流需求时(如GPU渲染),多层陶瓷电容(MLCC)快速释放电荷,抑制电压跌落。

- 动态能量分配:

- 开关电源:电容在Buck/Boost电路中存储能量并传递至负载,决定转换效率与纹波水平。

- 电池供电系统:超级电容与锂电池配合,应对脉冲负载(如无线模块发射信号),延长电池寿命。

2. 信号完整性保障

- 高频噪声抑制:

- 去耦电容(Decoupling) :在IC电源引脚就近放置小容量陶瓷电容(0.1μF),吸收高频开关噪声(如数字芯片的GHz级瞬态电流)。

- 旁路电容(Bypass) :为敏感模拟电路(如运放、ADC)提供低阻抗回路,避免噪声耦合至信号路径。

- 信号耦合与隔离:

- 交流耦合:通过隔直电容(如10μF电解电容)阻断直流偏置,仅传递交流信号(如音频放大器输入级)。

- 阻抗匹配:在射频电路中,电容与电感组合实现阻抗变换(如天线匹配网络)。

3. 系统稳定性控制

- 反馈环路补偿:

- 相位裕度调节:在运放或稳压器反馈网络中,电容与电阻构成极点/零点,避免振荡(如LDO输出端加1μF+10Ω RC网络)。

- 环路带宽控制:通过电容容值调整系统响应速度(如PID控制器积分电容)。

- 时序与振荡控制:

- RC定时电路:电容充放电时间决定延时、振荡频率(如555定时器的周期由R、C值设定)。

- 谐振电路:LC/RC网络用于频率选择(如滤波器中心频率由电容和电感值决定)。

4. 电磁兼容(EMC)与抗干扰

- 共模/差模滤波:

- X/Y电容:在开关电源输入级,X电容抑制差模噪声,Y电容旁路共模噪声至地(需符合安规耐压要求)。

- EMI吸收:铁氧体磁珠与电容组合形成π型滤波器,抑制高频辐射(如USB接口的EMC设计)。

- 静电防护(ESD):

- TVS+电容组合:电容吸收ESD脉冲能量,TVS钳位电压(如触控屏接口防护)。

5. 关键设计参数与选型逻辑

- 核心参数权衡:

- 容值(C) :低频场景需大容量(如1000μF电解电容),高频场景依赖小容量低ESL电容(如10nF MLCC)。

- 电压额定值:需留至少20%裕量(如12V电源选用25V耐压电容)。

- ESR/ESL:低ESR电容(如聚合物电解电容)可降低纹波;低ESL设计(如三端陶瓷电容)提升高频性能。

- 温度与寿命考量:

- 温度系数:X7R/X5R陶瓷电容容值随温度变化较小,适用于宽温环境。

- 老化效应:MLCC的容值随时间下降(如Y5V材质年衰减率可达5%),需预设计余量。

6. 典型失效模式与设计避坑

- 电压击穿:过压或电压瞬态导致介质击穿(如钽电容反接易爆炸)。

- 机械应力:PCB弯曲导致MLCC开裂(如大尺寸封装电容需远离板边)。

- 热失效:高温加速电解液干涸(如铝电解电容靠近发热元件时寿命缩短)。

- 谐振风险:忽略电容自谐振频率时,高频去耦失效(如0.1μF MLCC在100MHz以上感性区阻抗升高)。

7. 未来技术对设计的影响

- 高密度电容:超级电容与电池混合储能系统将简化电源拓扑(如无人机动力系统)。

- 高频材料:氮化镓(GaN)器件驱动下,低ESL电容(如倒装封装MLCC)需求激增。

- 集成化趋势:嵌入式电容(如PCB内层埋容)减少寄生参数,提升信号完整性。

350

350

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?