一、VGA概述

1.1 简述

图像显示设备在日常生活中随处可见,例如家庭电视机、计算机显示屏幕等,这些设备之所以能够显示我们需要的数据图像信息,归功于视频传输接口。常见的视频传输接口有三种:VGA 接口、 DVI 接口和 HDMI 接口,目前的显示设备都配有这三种视频传输接口。

三类视频接口的发展历程为 VGA → DVI → HDMI 。其中 VGA 接口出现最早,只能传输模拟图像信号; 随后出现的 DVI 接口又分为三类: DVI-A 、 DVI-D 、 DVI-I ,分别可传输纯模拟图像信号、纯数字图像信号和兼容模拟、数字图像信号;最后的 HDMI 在传输数字图像信号的基础上又可以传输音频信号。

VGA,英文全称“ Video Graphics Array ”,译为视频图形阵列,是一种使用模拟信号进行视频传输的标准协议,由 IBM 公司于 1987 年推出,因其分辨率高、显示速度快、颜色丰富等优点,广泛应用于彩色显示器领域。由于 VGA 接口体积较大,与追求小巧便携的笔记本电脑背道而驰,在笔记本电脑领域,VGA 接口已被逐渐淘汰,但对于体积较大的台式机,这种情况并未发生,虽然 VGA 标准在当前个人电脑市场中已经过时,但因其在显示标准中的重要性和良好的兼容性,VGA 仍然是最多制造商所共同支持的一个标准,个人电脑在加载自己独特驱动程序之前,都必须支持 VGA 的标准。

早期的 CRT 显示器只能接收模拟信号,不能接收数字信号,计算机内部显卡将数字信号转换成模拟信号,通过 VGA 接口传给 VGA 显示器,虽然现如今许多种类的显示器可以直接接收数字信号,但为了兼容显卡的 VGA 接口,大都支持 VGA 标准。

VGA 接口中以针式引出信号线的称为公头,以孔式引出信号线的称为母头。在计算机和 VGA 显示器上一般引出母头接口,使用两头均为公头的 VGA 连接线将计算机与 VGA显示器连接起来,两者图像传输时,使用的是 VGA 图像传输标准,该标准的具体内容在后面博文会详细说明。VGA 公头、母头接口和 VGA 连接线。

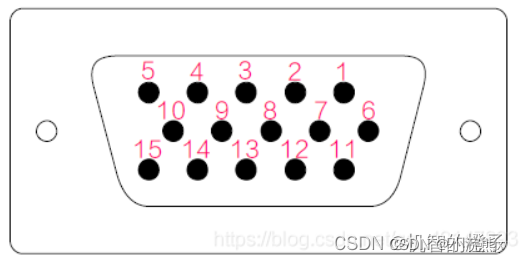

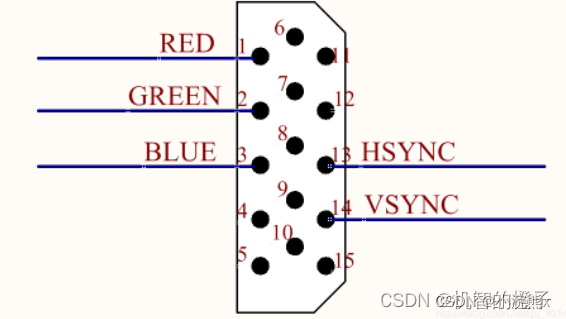

1.2 管脚定义

1.3 VGA显示原理

VGA通过引脚的模拟电压(0V-0.714V)显示红绿蓝三种颜色,不同的电压值对应不同的颜色。

VGA驱动显示器用的是扫描的方式,一般是逐行扫描。

逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;

当扫描完所有的行,形成一帧后,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

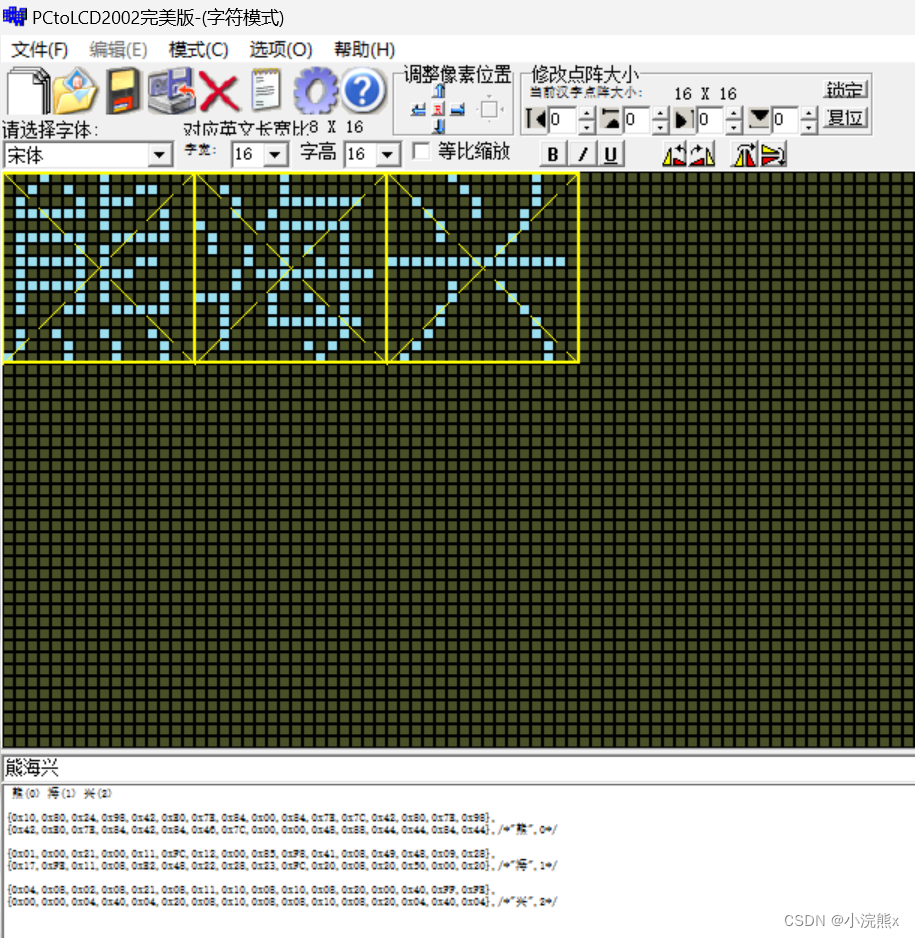

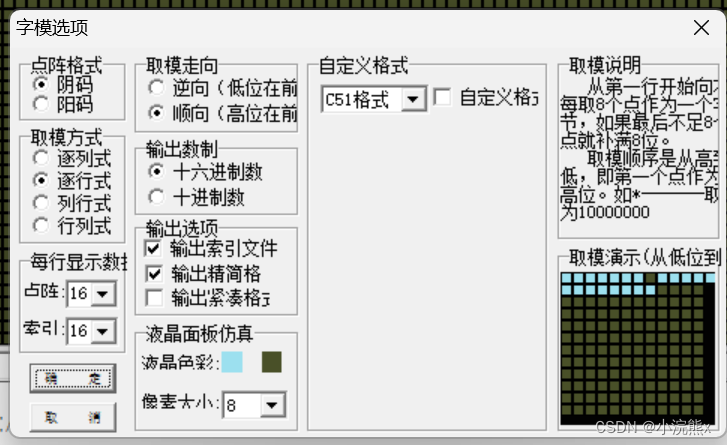

二.VGA显示字符

1.1 提取字模

代码:

module VGA_test(

OSC_50, //原CLK2_50时钟信号

VGA_CLK, //VGA自时钟

VGA_HS, //行同步信号

VGA_VS, //场同步信号

VGA_BLANK, //复合空白信号控制信号 当BLANK为低电平时模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略

VGA_SYNC, //符合同步控制信号 行时序和场时序都要产生同步脉冲

VGA_R, //VGA绿色

VGA_B, //VGA蓝色

VGA_G); //VGA绿色

input OSC_50; //外部时钟信号CLK2_50

output VGA_CLK,VGA_HS,VGA_VS,VGA_BLANK,VGA_SYNC;

output [7:0] VGA_R,VGA_B,VGA_G;

parameter H_FRONT = 16; //行同步前沿信号周期长

parameter H_SYNC = 96; //行同步信号周期长

parameter H_BACK = 48; //行同步后沿信号周期长

parameter H_ACT = 640; //行显示周期长

parameter H_BLANK = H_FRONT+H_SYNC+H_BACK; //行空白信号总周期长

parameter H_TOTAL = H_FRONT+H_SYNC+H_BACK+H_ACT; //行总周期长耗时

parameter V_FRONT = 11; //场同步前沿信号周期长

parameter V_SYNC = 2; //场同步信号周期长

parameter V_BACK = 31; //场同步后沿信号周期长

parameter V_ACT = 480; //场显示周期长

parameter V_BLANK = V_FRONT+V_SYNC+V_BACK; //场空白信号总周期长

parameter V_TOTAL = V_FRONT+V_SYNC+V_BACK+V_ACT; //场总周期长耗时

reg [10:0] H_Cont; //行周期计数器

reg [10:0] V_Cont; //场周期计数器

wire [7:0] VGA_R; //VGA红色控制线

wire [7:0] VGA_G; //VGA绿色控制线

wire [7:0] VGA_B; //VGA蓝色控制线

reg VGA_HS;

reg VGA_VS;

reg [10:0] X; //当前行第几个像素点

reg [10:0] Y; //当前场第几行

reg CLK_25;

always@(posedge OSC_50)

begin

CLK_25=~CLK_25; //时钟

end

assign VGA_SYNC = 1'b0; //同步信号低电平

assign VGA_BLANK = ~((H_Cont<H_BLANK)||(V_Cont<V_BLANK)); //当行计数器小于行空白总长或场计数器小于场空白总长时,空白信号低电平

assign VGA_CLK = ~CLK_to_DAC; //VGA时钟等于CLK_25取反

assign CLK_to_DAC = CLK_25;

always@(posedge CLK_to_DAC)

begin

if(H_Cont<H_TOTAL) //如果行计数器小于行总时长

H_Cont<=H_Cont+1'b1; //行计数器+1

else H_Cont<=0; //否则行计数器清零

if(H_Cont==H_FRONT-1) //如果行计数器等于行前沿空白时间-1

VGA_HS<=1'b0; //行同步信号置0

if(H_Cont==H_FRONT+H_SYNC-1) //如果行计数器等于行前沿+行同步-1

VGA_HS<=1'b1; //行同步信号置1

if(H_Cont>=H_BLANK) //如果行计数器大于等于行空白总时长

X<=H_Cont-H_BLANK; //X等于行计数器-行空白总时长 (X为当前行第几个像素点)

else X<=0; //否则X为0

end

always@(posedge VGA_HS)

begin

if(V_Cont<V_TOTAL) //如果场计数器小于行总时长

V_Cont<=V_Cont+1'b1; //场计数器+1

else V_Cont<=0; //否则场计数器清零

if(V_Cont==V_FRONT-1) //如果场计数器等于场前沿空白时间-1

VGA_VS<=1'b0; //场同步信号置0

if(V_Cont==V_FRONT+V_SYNC-1) //如果场计数器等于行前沿+场同步-1

VGA_VS<=1'b1; //场同步信号置1

if(V_Cont>=V_BLANK) //如果场计数器大于等于场空白总时长

Y<=V_Cont-V_BLANK; //Y等于场计数器-场空白总时长 (Y为当前场第几行)

else Y<=0; //否则Y为0

end

reg valid_yr;

always@(posedge CLK_to_DAC)

if(V_Cont == 10'd32) //场计数器=32时

valid_yr<=1'b1; //行输入激活

else if(V_Cont==10'd512) //场计数器=512时

valid_yr<=1'b0; //行输入冻结

wire valid_y=valid_yr; //连线

reg valid_r;

always@(posedge CLK_to_DAC)

if((H_Cont == 10'd32)&&valid_y) //行计数器=32时

valid_r<=1'b1; //像素输入激活

else if((H_Cont==10'd512)&&valid_y) //行计数器=512时

valid_r<=1'b0; //像素输入冻结

wire valid = valid_r; //连线

wire[10:0] x_dis; //像素显示控制信号

wire[10:0] y_dis; //行显示控制信号

assign x_dis=X; //连线X

assign y_dis=Y; //连线Y

parameter

char_line00=240'h010010400000000000000000000000000000000000000000000000000000,

char_line01=240'h010010400000000000000000000000000000000000000000000000000000,

char_line02=240'h7FFCFE780000000000000000000000000000000000000000000000000000,

char_line03=240'h03801088000007F00FE000800FE007E01FFC07E007F007E00FE000800080,

char_line04=240'h05407C100000081830180780301818183008181808181818301807800780,

char_line05=240'h092011FC0000100038180180300C381C2010381C1000381C381801800180,

char_line06=240'h3118FE240000300000180180700C300C0020300C3000300C001801800180,

char_line07=240'hC10600247FFE37F000600180301C300C0040300C37F0300C006001800180,

char_line08=240'h0FE07DFE0000380C01F00180382C300C0080300C380C300C01F001800180,

char_line09=240'h004044240000300C001801800FCC300C0180300C300C300C001801800180,

char_line0a=240'h00807C240000300C000C0180001C300C0300300C300C300C000C01800180,

char_line0b=240'hFFFE45FC0000300C380C01800018381803003818300C3818380C01800180,

char_line0c=240'h01007C24000018183018018038301C1003801C1018181C10301801800180,

char_line0d=240'h01004420000007E00FE00FF80FC007E0030007E007E007E00FE00FF80FF8,

char_line0e=240'h050054A00000000000000000000000000000000000000000000000000000,

char_line0f=240'h020048400000000000000000000000000000000000000000000000000000;

reg[7:0] char_bit;

always@(posedge CLK_to_DAC)

if(X==10'd180)char_bit<=9'd240; //当显示到144像素时准备开始输出图像数据

else if(X>10'd180&&X<10'd420) //左边距屏幕144像素到416像素时 416=144+272(图像宽度)

char_bit<=char_bit-1'b1; //倒着输出图像信息

reg[29:0] vga_rgb; //定义颜色缓存

always@(posedge CLK_to_DAC)

if(X>10'd180&&X<10'd420) //X控制图像的横向显示边界:左边距屏幕左边144像素 右边界距屏幕左边界416像素

begin case(Y) //Y控制图像的纵向显示边界:从距离屏幕顶部160像素开始显示第一行数据

10'd200:

if(char_line00[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000; //如果该行有数据 则颜色为红色

else vga_rgb<=30'b0000000000_0000000000_0000000000; //否则为黑色

10'd201:

if(char_line01[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd202:

if(char_line02[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd203:

if(char_line03[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd204:

if(char_line04[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd205:

if(char_line05[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd206:

if(char_line06[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd207:

if(char_line07[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd208:

if(char_line08[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd209:

if(char_line09[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd210:

if(char_line0a[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd211:

if(char_line0b[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd212:

if(char_line0c[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd213:

if(char_line0d[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd214:

if(char_line0e[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

10'd215:

if(char_line0f[char_bit])vga_rgb<=30'b1111111111_0000000000_0000000000;

else vga_rgb<=30'b0000000000_0000000000_0000000000;

default:vga_rgb<=30'h0000000000; //默认颜色黑色

endcase

end

else vga_rgb<=30'h000000000; //否则黑色

assign VGA_R=vga_rgb[23:16];

assign VGA_G=vga_rgb[15:8];

assign VGA_B=vga_rgb[7:0];

endmodule

三.VGA显示彩色条纹

代码:

module VGA_colorbar_test(

OSC_50, //原CLK2_50时钟信号

VGA_CLK, //VGA自时钟

VGA_HS, //行同步信号

VGA_VS, //场同步信号

VGA_BLANK, //复合空白信号控制信号 当BLANK为低电平时模拟视频输出消隐电平,此时从R9~R0,G9~G0,B9~B0输入的所有数据被忽略

VGA_SYNC, //符合同步控制信号 行时序和场时序都要产生同步脉冲

VGA_R, //VGA绿色

VGA_B, //VGA蓝色

VGA_G); //VGA绿色

input OSC_50; //外部时钟信号CLK2_50

output VGA_CLK,VGA_HS,VGA_VS,VGA_BLANK,VGA_SYNC;

output [7:0] VGA_R,VGA_B,VGA_G;

parameter H_FRONT = 16; //行同步前沿信号周期长

parameter H_SYNC = 96; //行同步信号周期长

parameter H_BACK = 48; //行同步后沿信号周期长

parameter H_ACT = 640; //行显示周期长

parameter H_BLANK = H_FRONT+H_SYNC+H_BACK; //行空白信号总周期长

parameter H_TOTAL = H_FRONT+H_SYNC+H_BACK+H_ACT; //行总周期长耗时

parameter V_FRONT = 11; //场同步前沿信号周期长

parameter V_SYNC = 2; //场同步信号周期长

parameter V_BACK = 31; //场同步后沿信号周期长

parameter V_ACT = 480; //场显示周期长

parameter V_BLANK = V_FRONT+V_SYNC+V_BACK; //场空白信号总周期长

parameter V_TOTAL = V_FRONT+V_SYNC+V_BACK+V_ACT; //场总周期长耗时

reg [10:0] H_Cont; //行周期计数器

reg [10:0] V_Cont; //场周期计数器

wire [7:0] VGA_R; //VGA红色控制线

wire [7:0] VGA_G; //VGA绿色控制线

wire [7:0] VGA_B; //VGA蓝色控制线

reg VGA_HS;

reg VGA_VS;

reg [10:0] X; //当前行第几个像素点

reg [10:0] Y; //当前场第几行

reg CLK_25;

always@(posedge OSC_50)begin

CLK_25=~CLK_25; //时钟

end

assign VGA_SYNC = 1'b0; //同步信号低电平

assign VGA_BLANK = ~((H_Cont<H_BLANK)||(V_Cont<V_BLANK)); //当行计数器小于行空白总长或场计数器小于场空白总长时,空白信号低电平

assign VGA_CLK = ~CLK_to_DAC; //VGA时钟等于CLK_25取反

assign CLK_to_DAC = CLK_25;

always@(posedge CLK_to_DAC)begin

if(H_Cont<H_TOTAL) //如果行计数器小于行总时长

H_Cont<=H_Cont+1'b1; //行计数器+1

else H_Cont<=0; //否则行计数器清零

if(H_Cont==H_FRONT-1) //如果行计数器等于行前沿空白时间-1

VGA_HS<=1'b0; //行同步信号置0

if(H_Cont==H_FRONT+H_SYNC-1) //如果行计数器等于行前沿+行同步-1

VGA_HS<=1'b1; //行同步信号置1

if(H_Cont>=H_BLANK) //如果行计数器大于等于行空白总时长

X<=H_Cont-H_BLANK; //X等于行计数器-行空白总时长 (X为当前行第几个像素点)

else X<=0; //否则X为0

end

always@(posedge VGA_HS)begin

if(V_Cont<V_TOTAL) //如果场计数器小于行总时长

V_Cont<=V_Cont+1'b1; //场计数器+1

else V_Cont<=0; //否则场计数器清零

if(V_Cont==V_FRONT-1) //如果场计数器等于场前沿空白时间-1

VGA_VS<=1'b0; //场同步信号置0

if(V_Cont==V_FRONT+V_SYNC-1) //如果场计数器等于行前沿+场同步-1

VGA_VS<=1'b1; //场同步信号置1

if(V_Cont>=V_BLANK) //如果场计数器大于等于场空白总时长

Y<=V_Cont-V_BLANK; //Y等于场计数器-场空白总时长 (Y为当前场第几行)

else Y<=0; //否则Y为0

end

reg valid_yr;

always@(posedge CLK_to_DAC)begin

if(V_Cont == 10'd32) //场计数器=32时

valid_yr<=1'b1; //行输入激活

else if(V_Cont==10'd512) //场计数器=512时

valid_yr<=1'b0; //行输入冻结

end

wire valid_y=valid_yr; //连线

reg valid_r;

always@(posedge CLK_to_DAC)begin

if((H_Cont == 10'd32)&&valid_y) //行计数器=32时

valid_r<=1'b1; //像素输入激活

else if((H_Cont==10'd512)&&valid_y) //行计数器=512时

valid_r<=1'b0; //像素输入冻结

end

wire valid = valid_r; //连线

assign x_dis=X; //连线X

assign y_dis=Y; //连线Y

// reg[7:0] char_bit;

// always@(posedge CLK_to_DAC)

// if(X==10'd144)char_bit<=9'd240; //当显示到144像素时准备开始输出图像数据

// else if(X>10'd144&&X<10'd384) //左边距屏幕144像素到416像素时 416=144+272(图像宽度)

// char_bit<=char_bit-1'b1; //倒着输出图像信息

reg[29:0] vga_rgb; //定义颜色缓存

always@(posedge CLK_to_DAC) begin

if(X>=0&&X<200)begin //X控制图像的横向显示边界:左边距屏幕左边144像素 右边界距屏幕左边界416像素

vga_rgb<=30'hffffffffff; //白色

end

else if(X>=200&&X<400)begin

vga_rgb<=30'hf00ff65f1f;

end

else if(X>=400&&X<600)begin

vga_rgb<=30'h9563486251;

end

else begin

vga_rgb<=30'h5864928654;

end

end

assign VGA_R=vga_rgb[23:16];

assign VGA_G=vga_rgb[15:8];

assign VGA_B=vga_rgb[7:0];

endmodule

四.VGA显示彩色图片

在前面的学习中了解到图像的格式有多种,例如JPEG,BMP,PNG,JPG等,图像的位数也有单色、16色、256色、4096色、16位真彩色、24位真彩色、32位真彩色在这里插入图片描述

这几种。

VGA的驱动程序显示的格式为RGB565,我们先找到一张需要显示的彩色图片,经过处理,将该图片转化为ROM可以存储的格式,然后VGA驱动程序从ROM中读取数据,输出到VGA显示屏显示。尽量选一张小的图片,因为ROM存储空间有限。

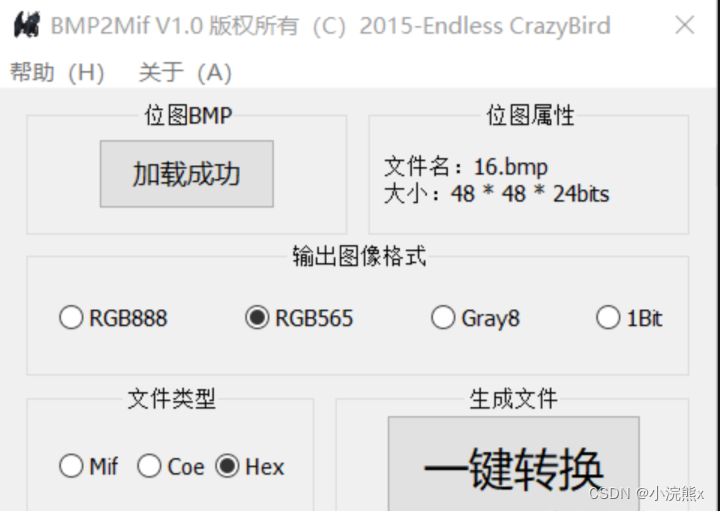

1.使用BMP2Mif软件将bmp格式图片转换为hex文件

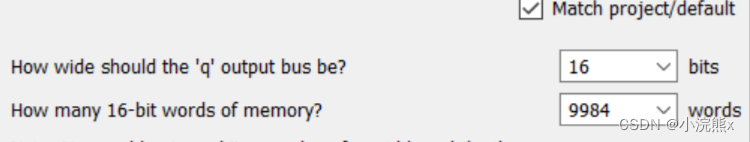

2、 新建Quartus工程,产生ROM IP核,将生成的mif文件保存在ROM中

双击选择ROM:1-PORT

设置位宽度为16位,以及图片大小

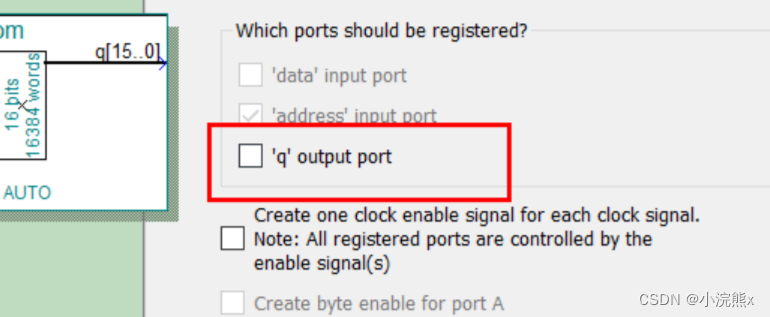

取消勾选:

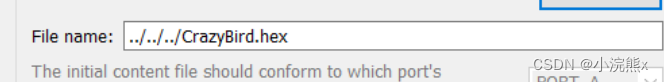

加载HEX文件

3、从ROM取出图片数据

代码如下:

module data_drive (

input wire vga_clk,

input wire rst_n,

input wire [ 11:0 ] addr_h,

input wire [ 11:0 ] addr_v,

output reg [ 15:0 ] rgb_data

);

localparam black = 16'd0;

parameter height = 48; // 图片高度

parameter width = 48; // 图片宽度

reg [ 13:0 ] rom_address ; // ROM地址

wire [ 15:0 ] rom_data ; // 图片数据

wire flag_enable_out2 ; // 图片有效区域

wire flag_clear_rom_address ; // 地址清零

wire flag_begin_h ; // 图片显示行

wire flag_begin_v ; // 图片显示列

always @( posedge vga_clk or negedge rst_n) begin

if(!rst_n)begin

rgb_data = black;

end

else if ( flag_enable_out2 ) begin

rgb_data = rom_data;

end

else begin

rgb_data = black;

end

end

//ROM地址计数器

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

rom_address <= 0;

end

else if ( flag_clear_rom_address ) begin //计数满清零

rom_address <= 0;

end

else if ( flag_enable_out2 ) begin //在有效区域内+1

rom_address <= rom_address + 1;

end

else begin //无效区域保持

rom_address <= rom_address;

end

end

assign flag_clear_rom_address = rom_address == height * width - 1;

assign flag_begin_h = addr_h > ( ( 640 - width ) / 2 ) && addr_h < ( ( 640 - width ) / 2 ) + width + 1;

assign flag_begin_v = addr_v > ( ( 480 - height )/2 ) && addr_v <( ( 480 - height )/2 ) + height + 1;

assign flag_enable_out2 = flag_begin_h && flag_begin_v;

//实例化ROM

rom rom_inst (

.address ( rom_address ),

.clock ( vga_clk ),

.q ( rom_data )

);

endmodule

vga驱动程序

module vga_display_pic (

input wire clk, //系统时钟

input wire rst_n, //复位

input wire [ 15:0 ] rgb_data, //16位RGB对应值

output wire vga_clk, //vga时钟 25M

output reg h_sync, //行同步信号

output reg v_sync, //场同步信号

output reg [ 11:0 ] addr_h, //行地址

output reg [ 11:0 ] addr_v, //列地址

output wire [ 4:0 ] rgb_r, //红基色

output wire [ 5:0 ] rgb_g, //绿基色

output wire [ 4:0 ] rgb_b //蓝基色

);

// 640 * 480 60HZ

localparam H_FRONT = 16; // 行同步前沿信号周期长

localparam H_SYNC = 96; // 行同步信号周期长

localparam H_BLACK = 48; // 行同步后沿信号周期长

localparam H_ACT = 640; // 行显示周期长

localparam V_FRONT = 11; // 场同步前沿信号周期长

localparam V_SYNC = 2; // 场同步信号周期长

localparam V_BLACK = 31; // 场同步后沿信号周期长

localparam V_ACT = 480; // 场显示周期长

localparam H_TOTAL = H_FRONT + H_SYNC + H_BLACK + H_ACT; // 行周期

localparam V_TOTAL = V_FRONT + V_SYNC + V_BLACK + V_ACT; // 列周期

reg [ 11:0 ] cnt_h ; // 行计数器

reg [ 11:0 ] cnt_v ; // 场计数器

reg [ 15:0 ] rgb ; // 对应显示颜色值

// 对应计数器开始、结束、计数信号

wire flag_enable_cnt_h ;

wire flag_clear_cnt_h ;

wire flag_enable_cnt_v ;

wire flag_clear_cnt_v ;

wire flag_add_cnt_v ;

wire valid_area ;

// 25M时钟

wire clk_25 ;

// 50M时钟

wire clk_50 ;

wire locked ;

//PLL

pll pll_inst (

.areset ( ~rst_n ),

.inclk0 ( clk ),

.c0 ( clk_50 ), //50M

.c1 ( clk_25 ), //25M

.locked (locked )

);

//根据不同分配率选择不同频率时钟

assign vga_clk = clk_25;

// 行计数

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

cnt_h <= 0;

end

else if ( flag_enable_cnt_h ) begin

if ( flag_clear_cnt_h ) begin

cnt_h <= 0;

end

else begin

cnt_h <= cnt_h + 1;

end

end

else begin

cnt_h <= 0;

end

end

assign flag_enable_cnt_h = 1;

assign flag_clear_cnt_h = cnt_h == H_TOTAL - 1;

// 行同步信号

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

h_sync <= 0;

end

else if ( cnt_h == H_SYNC - 1 ) begin // 同步周期时为1

h_sync <= 1;

end

else if ( flag_clear_cnt_h ) begin // 其余为0

h_sync <= 0;

end

else begin

h_sync <= h_sync;

end

end

// 场计数

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

cnt_v <= 0;

end

else if ( flag_enable_cnt_v ) begin

if ( flag_clear_cnt_v ) begin

cnt_v <= 0;

end

else if ( flag_add_cnt_v ) begin

cnt_v <= cnt_v + 1;

end

else begin

cnt_v <= cnt_v;

end

end

else begin

cnt_v <= 0;

end

end

assign flag_enable_cnt_v = flag_enable_cnt_h;

assign flag_clear_cnt_v = cnt_v == V_TOTAL - 1;

assign flag_add_cnt_v = flag_clear_cnt_h;

// 场同步信号

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

v_sync <= 0;

end

else if ( cnt_v == V_SYNC - 1 ) begin

v_sync <= 1;

end

else if ( flag_clear_cnt_v ) begin

v_sync <= 0;

end

else begin

v_sync <= v_sync;

end

end

// 对应有效区域行地址 1-640

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

addr_h <= 0;

end

else if ( valid_area ) begin

addr_h <= cnt_h - H_SYNC - H_BLACK + 1;

end

else begin

addr_h <= 0;

end

end

// 对应有效区域列地址 1-480

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

addr_v <= 0;

end

else if ( valid_area ) begin

addr_v <= cnt_v -V_SYNC - V_BLACK + 1;

end

else begin

addr_v <= 0;

end

end

// 有效显示区域

assign valid_area = cnt_h >= H_SYNC + H_BLACK && cnt_h <= H_SYNC + H_BLACK + H_ACT && cnt_v >= V_SYNC + V_BLACK && cnt_v <= V_SYNC + V_BLACK + V_ACT;

// 显示颜色

always @( posedge vga_clk or negedge rst_n ) begin

if ( !rst_n ) begin

rgb <= 16'h0;

end

else if ( valid_area ) begin

rgb <= rgb_data;

end

else begin

rgb <= 16'b0;

end

end

assign rgb_r = rgb[ 15:11 ];

assign rgb_g = rgb[ 10:5 ];

assign rgb_b = rgb[ 4:0 ];

endmodule

顶层模块

module vga_top (

input wire clk,

input wire rst_n,

output wire vga_clk,

output wire h_sync,

output wire v_sync,

output wire [ 4:0 ] rgb_r,

output wire [ 5:0 ] rgb_g,

output wire [ 4:0 ] rgb_b

);

wire [ 11:0 ] addr_h ;

wire [ 11:0 ] addr_v ;

wire [ 15:0 ] rgb_data ;

//模块例化

vga_display_pic (

.clk (clk ),

.rst_n (rst_n ),

.rgb_data (rgb_data ),

.vga_clk (vga_clk ),

.h_sync (h_sync ),

.v_sync (v_sync ),

.addr_h (addr_h ),

.addr_v (addr_v ),

.rgb_r (rgb_r ),

.rgb_g (rgb_g ),

.rgb_b (rgb_b )

);

//数据模块

data_drive u_data_drive(

.vga_clk ( vga_clk ),

.rst_n ( rst_n ),

.addr_h ( addr_h ),

.addr_v ( addr_v ),

.rgb_data ( rgb_data )

);

endmodule

645

645

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?