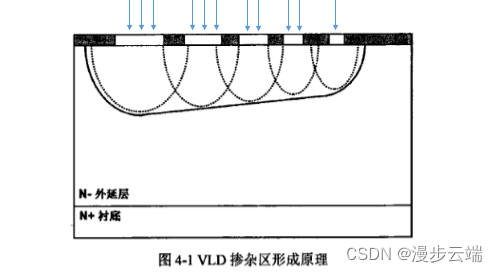

横向变掺杂(Variation of Lateral Doping,VLD)的基本原理是:掺杂注入开孔的大小不同,退火后掺杂区的杂质浓度和结深也会不一样。利用这种现象在横向形成掺杂浓度及结深变化的P型区,如图 4-1 所示。有效的改善了主结电场,降低了芯片面积,提升了终端的耐压占比。

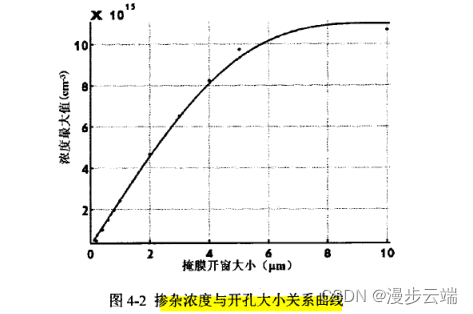

可以通过调整 mask 窗口大小来控制掺杂浓度。图 4-2 是在确定的工艺条件下,通过改变 mask 窗口大小进行工艺仿真,然后测量其掺杂浓度。

设计方法

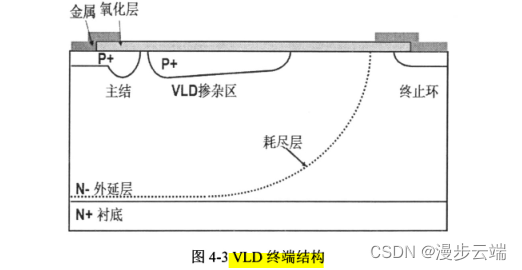

在设计 VLD 终端时,可将整个杂质浓度变化的 P 型区看做一个场限环,设置在主结外侧,用来分担主结电场,提升击穿电压,如图 4-3 所示。从理论上来讲,主结与 VLD 掺杂区同时击穿时,耐压达到最大。因此,在设置 VLD 区域和主结之间的间距时,可参考单浮空场限环的设计方法。

仿真结果分析

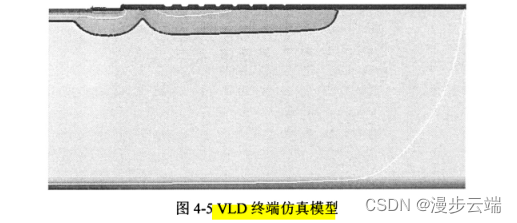

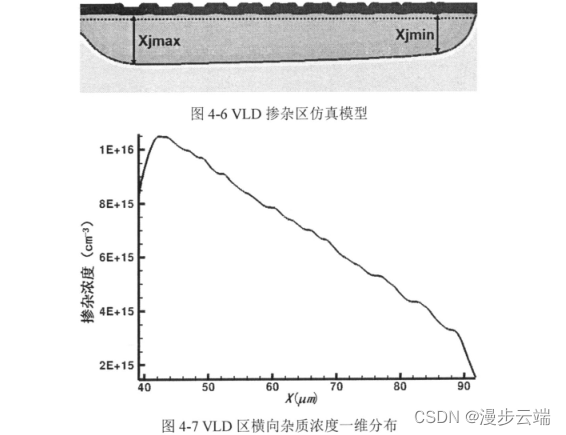

图 4-5 为在确定的工艺条件和mask参数下仿真得到的掺杂模型图。可以看出,VLD 掺杂区的结深从左到右逐渐减小,测量得到最大结深 Xj max=7.82um,最小结深 Xj min=6.33um。为了显示 VLD 结构的掺杂浓度变化,沿着图 4-6 中的虚线截取杂质浓度的一维分布曲线,如图 4-7。

从图 4-7 可以看出,结深最大的地方,表面掺杂浓度约为 1.05E16 cm-3,结深最小的地方,表面掺杂浓度约为 3.09E15 cm-3,而且近似呈线性分布。

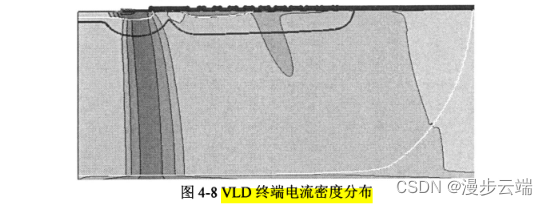

图 4-8 为击穿时的电流密度分布。可以看出,在主结底部电流最集中,因此击穿发生在主结处。

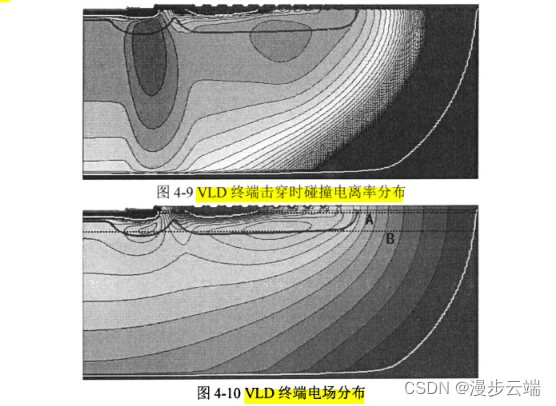

图 4-9 为击穿时终端的碰撞电离率分布,图 4-10 为 VLD 终端击穿时的电场分布,并且电场较大的区域在 VLD 掺杂区底部和主结外侧底部,结合图 4-8、4-9、4-10 可以推断:击穿点在电场强度最大的主结底部而不是表面。

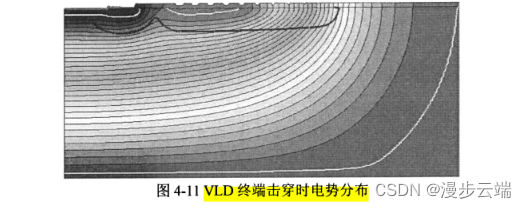

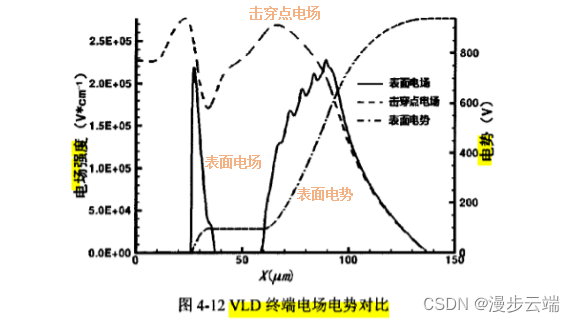

图 4-11 为 VLD 终端在击穿时的电势分布,沿图 4-10 中 A、B 两条虚线,以及图 4-11 的表面分别截取表面以及体内的电场分布和电势分布得到图 4-12 所示的曲线。

在图 4-12 中内部击穿点的电场一维分布曲线有两个峰值点,对应于主结底部和 VLD 掺杂区底部,分别是 2.77E5 V/cm 和 2.69E5 V/cm,VLD 掺杂区的峰值电场与主结很接近,说明 VLD 终端的效果基本达到最大了。由于击穿发生在主结底部,因此可以认为 2.77E5 V/cm 为此终端结构的临界电场。表面电场的峰值也有2个,最大的约为 2.28E5 V/cm,<临界电场,因此击穿不会发生在表面。另外,从电势分布可以看出,VLD 终端承担了大部分电压。

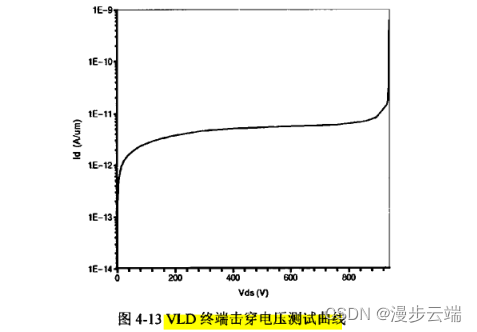

图 4-13 为击穿电压测试曲线。从图中可以看出,VLD 终端的击穿电压约为 938.5V。

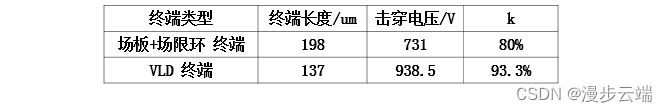

从下表可以看出,VLD 终端能够较大程度上减小芯片面积,提升了终端的耐压占比。

1246

1246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?