由于对基础知识的理解还不扎实,先阅读前辈的毕业论文,里面会讲的比较详细。

结终端

结终端技术的目的是解决功率半导体器件边缘部分阻断性能下降的问题。

结终端的作用是能够有效减小功率半导体器件边缘部分的曲率,缓解电场集中问题,从而提升器件的耐压能力。

结终端结构主要分为平面结终端、纵向结终端、复合结终端三个类型。

平面结终端结构基于平面工艺,包括等位环 ( Guard Ring , GR )、场限环( Field Limit Ring , FLR )、场板( Field Plate , FP )、结终端扩展( Junction Termination Extension , JTE )、横向变掺杂终端( Variation of Lateral Doping , VLD ) 等多种类型。

纵向终端结构基于纵向工艺,包括正斜角终端 ( Positive Bevel Edge Termination , PBET )、负斜角终端 ( Negative Bevel Edge Termination , NBET )、沟槽终端 ( Etch Termination , ET ) 等多种类型。

复合结终端结合了平面工艺与纵向工艺,为超结、碳化硅等功率器件的终端设计提供了解决方案。

下面分别介绍一下几种常见的结终端:

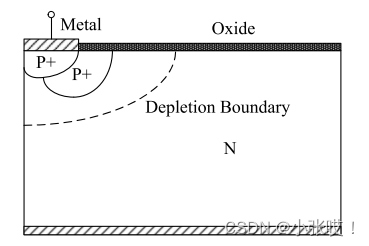

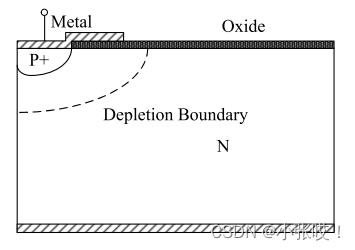

等位环终端

等位环终端通过在器件边缘部分注入一块结深大于主结的区域缓解器件边缘部分柱、球面结引入的曲率效应,提升器件的反向阻断能力,其结构如图 1所示。等位环终端提升耐压能力的作用有限,在实际应用中常与 FLR、JTE、VLD 等平面终端结合使用。

图 1 等位环结构示意图

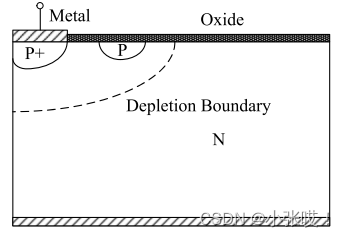

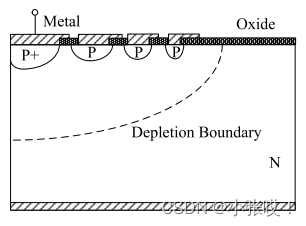

场限环终端

场限环终端于 1967 年由Y.C. KAO等人提出,其结构如图2所示。场限环终端通过在器件边缘耗尽区内的适当位置处注入一块浮空掺杂区,缓解电场聚集,提升终端位置处的电压阻断能力。

图2 场限环终端结构示意图

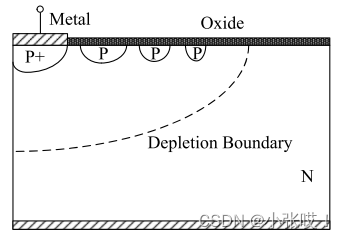

由于单场限环终端在实际应用中往往效率很低,多重场限环终端在中低压功率器件中应用的更加广泛,其示意图如图3所示。

图3 多重场限环终端示意图

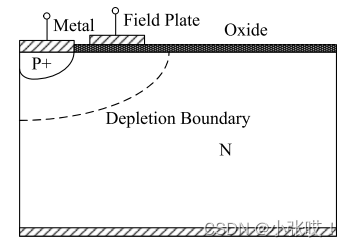

场板终端

场板终端由 A.S. Grove 等人于 1967 年提出,其结构如图4所示。该结构通过在终端氧化层上方覆盖一层金属电极,当施加反向偏压时,电子被推离终端表面,终端耗尽区扩展,以缓解终端电场集中问题,提升器件耐压能力。这种方法虽然理论上可以实现,但在实际应用中,新电极的引入会带来额外的工艺步骤且不易于控制。

图4 电极场板示意图

为解决上述问题,图5所示的场板结构被提出。该结构利用浮空电极的负电位推走终端表面电子,以实现扩展终端耗尽区,缓解电场集中的效果。实际应用中,为提升终端阻断能力,增强终端可靠性,通常采用金属场板与多晶硅场板的复合结构以解决金属场板末端会出现电场峰值的问题。此外,1976 年 T.Matsushita 等人提出了 SIPOS 钝化层技术,SIPOS 终端电荷沾污少,可靠性更好。SIPOS 钝化层在与场板共同组成的终端结构中,能够有效削减高电场,提升终端可靠性。

图5 浮空场板结构示意图

场限环与场板终端在结构上有着良好的兼容性。图6所示的多重场限环终端配合多重场板可以极大地提高终端阻断能力。在该结构中,场板利用场限环处的浮空电势排走终端表面电子,使终端耗尽区进一步展宽,合理的场限环宽度、场板长度设计可以进一步提升终端的利用效率。在功率半导体器件阻断性能不断进步的当下,单独的场限环、场板已经不再满足大多数应用场景的需求,多重场限环配合多重场板的终端结构在中高压硅基功率器件、碳化硅功率器件中有着更广泛的应用。

图6 多重场板场环

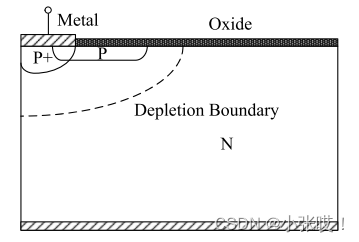

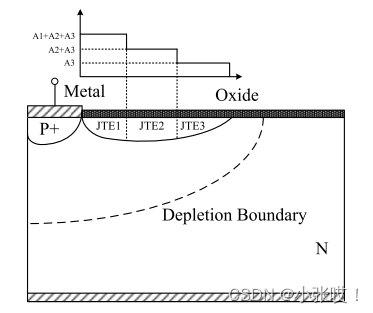

JTE 终端由V.A.K Temple 于 1977 年提出,其结构如图7所示。通过在主结边缘部分注入一块杂质浓度均匀分布的区域辅助分担终端部分的电场,以达到提升器件反向阻断能力的作用。单区域的 JTE 终端耐压能力取决于其杂质浓度,为了进一步提升 JTE 终端的耐压能力,多区 JTE 技术被提出。1993 年,张波、陈星弼、李肇基在《JTE 结的二维电场分析》一文中提出,从主结位置到终端末端浓度逐渐降低的三区 JTE 终端能够有效的削减单区 JTE 终端的尖峰电场,提升终端的阻断能力,其结构如图8所示。该文献还指出,单区 JTE 终端仅能够使器件达到35%的平行平面结耐压,而三区JTE终端能够将这一数据提升到91%。

图7 单区 JTE 终端示意图

图8 三区 JTE 终端结构示意图

VLD终端由 R. Stengl 等人于 1985 年提出,其结构如图9所示。从结构上看,VLD终端与 JTE 终端完全相同。但从本质上看,VLD终端内部浓度从主结位置向终端末端逐渐变小,降低了 JTE 终端对于精准的掺杂浓度的依赖。相较于多区 JTE 终端,VLD 终端仅需要一次掩膜注入就可以实现,工艺难度更低。渐变的掺杂分布对于终端末端的耗尽区有着良好的展宽作用,能够实现更高的耐压与更好的可靠性。VLD 终端连续成片的结构特点使其能够用更小的终端实现更高的耐压,反应在器件制作上可以节省大量终端面积,降低芯片制造成本。

本文详细介绍了结终端技术,包括平面结终端(如等位环、场限环和场板)、纵向结终端(PBET和NBET)以及复合结终端,着重阐述了这些技术如何通过改善电场分布来提升功率半导体器件的耐压能力。

本文详细介绍了结终端技术,包括平面结终端(如等位环、场限环和场板)、纵向结终端(PBET和NBET)以及复合结终端,着重阐述了这些技术如何通过改善电场分布来提升功率半导体器件的耐压能力。

1025

1025

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?