Chapter 27 Nonlinear Analog Circuits

这一章我们讨论非线性电路 (输出不是线性输入), 包括电压比较器, adaptive biasing 和 analog multiplier design.

Basic CMOS Comparator Design

一个完整比较器包括:

The pre-amp stage: 放大输入信号, 增大comparator sensitivity; 隔离来自后级positive feedback stage的kickback noise.

The positive feedback决定哪个信号更大.

The output buffer amplifies this information and outputs a digital signal.

输出级buffer信号并输出数字信号.

Preamplification

pre-amp stage如下图所示, 除了input和output. 没有高阻节点, 这对于高速设计很重要.

输出电流:

i

o

p

=

g

m

2

(

v

p

−

v

n

)

+

I

S

S

2

=

I

S

S

−

i

o

m

i_{op}=\frac{g_{m}}{2}(v_{p}-v_{n})+\frac{I_{SS}}{2}=I_{SS}-i_{om}

iop=2gm(vp−vn)+2ISS=ISS−iom

Decision Circuit

Decision Circuit 需要能判断mV的信号, 同时有hysteresis来抑制噪声. 下图用M6和M7形成positive feedback来增加gain.

一开始iop>>iom, M5, M7 on, M6 and M8 off.

随着iom增大, M6开始导通, 抢走M5的电流, 降低drain-source电压来关闭M7.

trip-point: M8的Vgs达到Vthn, M8快要导通, 但是M8和M6的电流都为0. M7和M5 电流mirror. 因此

i

o

p

=

β

A

β

B

i

o

m

i_{op}=\frac{\beta_{A}}{\beta_{B}}i_{om}

iop=βBβAiom

当betaA=betaB, iop=iom时, 发生switch, 取不同betaA和betaB可以产生hysteresis.

V

S

P

H

=

v

p

−

v

m

=

I

S

S

g

m

⋅

β

B

β

A

−

1

β

B

β

A

+

1

for

β

B

≥

β

A

V_{SPH}=v_{p}-v_{m}=\frac{I_{SS}}{g_{m}}\cdot \frac{\frac{\beta_{B}}{\beta_{A}}-1}{\frac{\beta_{B}}{\beta_{A}}+1} \text{ for } \beta_{B}\ge \beta_{A}

VSPH=vp−vm=gmISS⋅βAβB+1βAβB−1 for βB≥βA

and

V

S

P

L

=

−

V

S

P

H

V_{SPL}=-V_{SPH}

VSPL=−VSPH

Output Buffer

Output buffer的主要作用是将decision circuit的output转换成logic signal.

如果decision circuit的output 不匹配 output buffer的输入电压, 可以加入level-shift.

如下图所示:

下图展示了input rail-to-rail的comparator的design. 请注意PMOS diff-amp的output是如何加到NMOS (current) output. 如果把PMOS diff-amp直接连到decision circuits会导致minimum input common-mode变大, 减少input range.

Characterizing the Comparator

可以在pre-amp input diff pair之间加入MOS, 确保 drain电压不要变化太大, 防止一边的pre-amp 关闭.

Propagation Delay

The delay of a comparator can be reduced by cascading gain stages. In other words, the delay of a single high-gain stage is in general longer than the delay of several low-gain stages

设计多级小增益的延迟会小于单级高增益.

Minimum Input Slew Rate

If a comparator is to be used with slowly varying signals, or in a noisy environment, the decision circuit should have hysteresis.

如果input 变化很慢或者有noise, decision circuit需要有迟滞.

Clocked Comparators

clocked comparator: 在CLK rising/falling edge, 比较器输出才变化.

例如下图结构, 当clock=low, NAND SR pulled high, 比较器输出不变. 当clock=high, 才比较输入, 决定输出大小.

Input需要大于NMOS Vth, 当输入电压过大, MB1和MB2进入深线性区, 通过small channel resistance的差异, 影响比较器输出(不是特别好).

下图结构中, 去掉了在线性区的MB1和MB2. 通过steer电流来改变latch输出.

Input Buffers Revisited

Input buffer有相同propagation delays, 无视input slew-rate, amplitudes, or direction (high-to-low or low-to-high).

下图为input buffer改进版.

Adaptive Biasing

Adaptive biasing能在增大output current drive capability, 同时减小Op-amp功耗.

原理如下: 当vi1=vi2, Iss1=Iss2=0, 与普通op-amp一样

当vi1>vi2, Iss1增大. 当vi2>vi1, Iss2增大.

因此最大输出电流为Iss+Iss1 or Iss+Iss2.

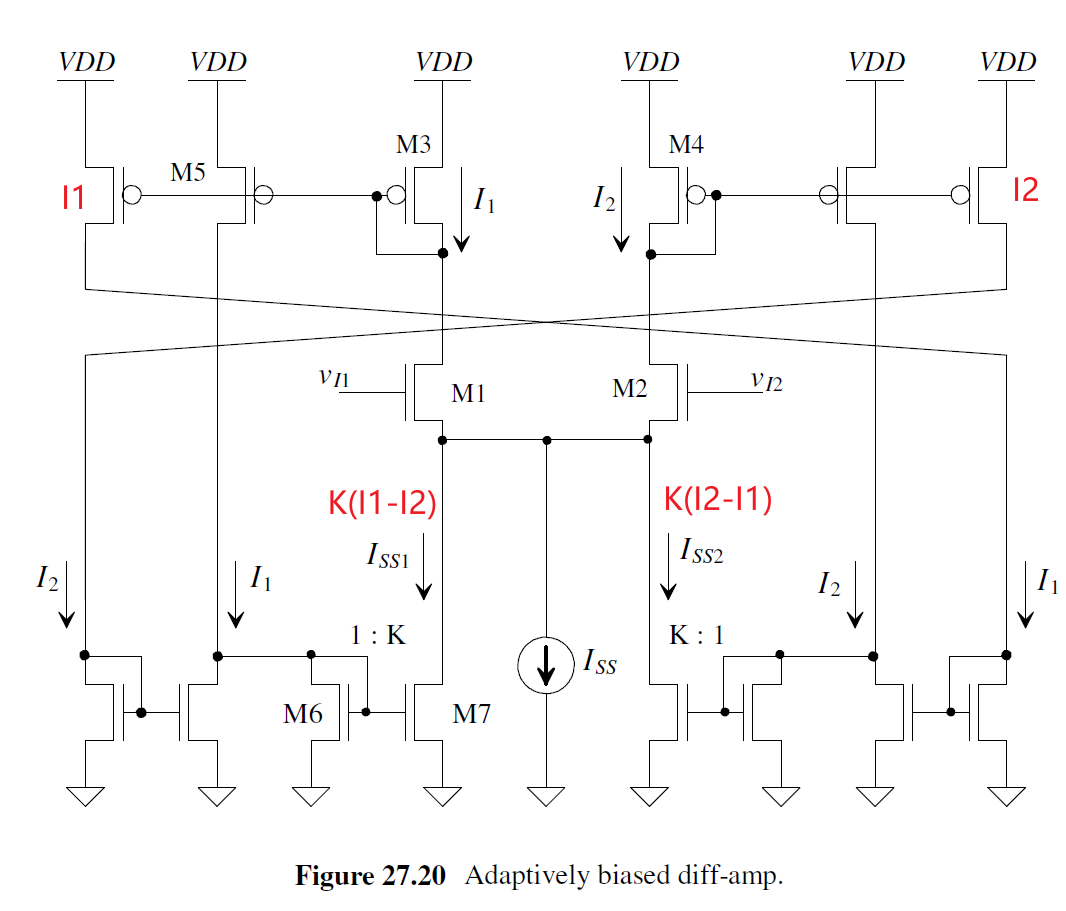

具体实现可见下图. Iss1=K(I1-I2)

具体实现电路可见下图:

当M2 off 时, M1上流过最大电流.

另外M1, M3, M5-M7形成正反馈. 一开始当M2 off, M1和M3的电流为Iss, 被M5和M6 Mirror, 因此Iss1=K*Iss, 因此M1上流过电流为Iss+K *Iss. 若M1,M3-M7仍在饱和区, 那么电流继续增大K倍

I

t

o

t

=

I

s

s

⋅

(

1

+

K

+

K

2

+

K

3

+

⋯

)

I_{tot}=I_{ss}\cdot (1+K+K^{2}+K^{3}+\cdots )

Itot=Iss⋅(1+K+K2+K3+⋯)

K=1, 这样无限的tail current看似能解决slew rate问题, 但实际上adaptive biasing会降低source电压, 导致关闭one-side diff pair变得困难.

如果K<1, 那么

I

t

o

t

=

I

s

s

1

−

K

I_{tot}=\frac{I_{ss}}{1-K}

Itot=1−KIss

如果K=0,(即M7不存在), 则没有adaptive biasing.

设K=1/2(M7是M6 size一半), 则能提供的 tail current = 2·Iss. 对于OTA design, K应该< =1.

adaptive biasing voltage-follower amplifier如下所示:

这是一个unity buffer. 当vin=vout, 流过M1和M2的电流为Iss+Id6. 当vin增加, IM1和IM3增加, 导致M4-M5-M6电流增加, 有效增加diff-pair的tail current. 而且可以增加drive load的电流. 注意M7的size可以比管子size更大去增加最大output current.

Analog Multipliers

在通信系统, 需要Analog multipliers. 下图展示了四象限乘法器.

v

o

u

t

=

K

m

⋅

v

x

v

y

v_{out}=K_{m}\cdot v_{x}v_{y}

vout=Km⋅vxvy

where Km is the multiplier gain with units of V^-1.

The Multiplying Quad

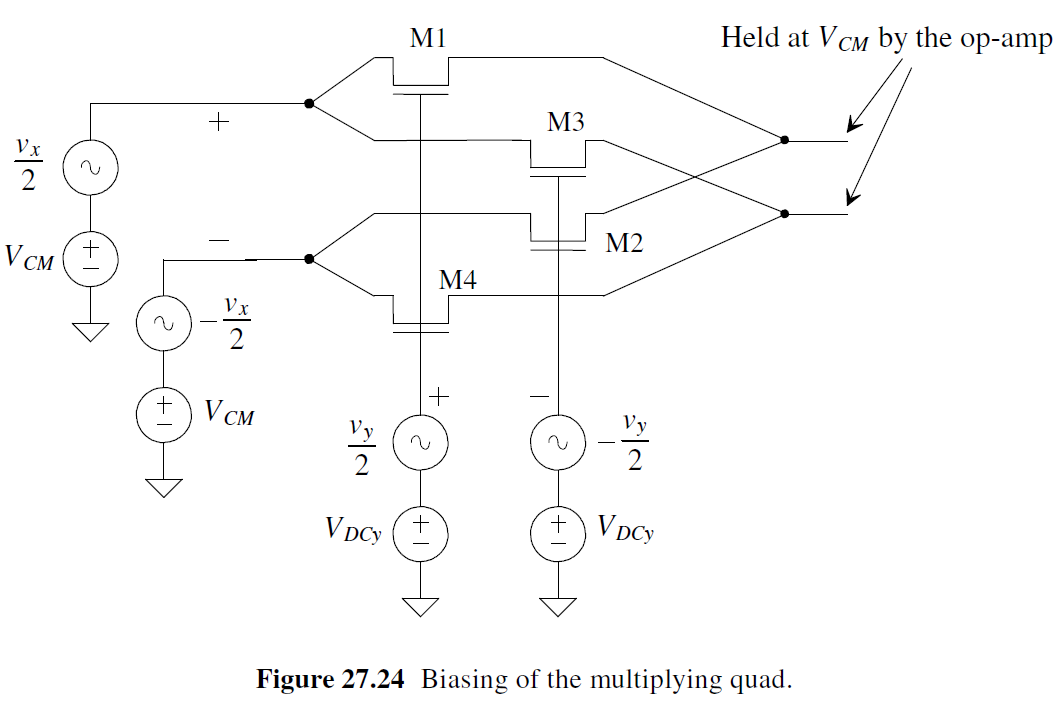

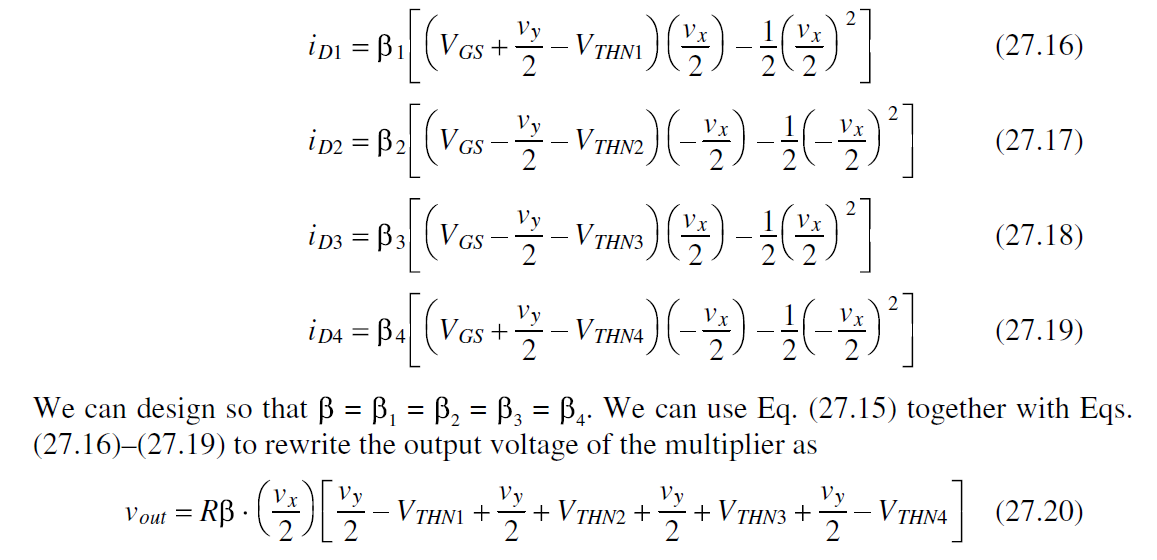

下图展示了CMOS multiplying quad(M1-M4). M1-M4工作在triode region, 可认为是电阻.

v

o

m

=

−

R

(

i

D

1

+

i

D

2

)

v_{om}=-R(i_{D1}+i_{D2})

vom=−R(iD1+iD2)

v o p = − R ( i D 3 + i D 4 ) v_{op}=-R(i_{D3}+i_{D4}) vop=−R(iD3+iD4)

v o u t = v o p − v o m = R ⋅ ( i D 1 + i D 2 − i D 3 − i D 4 ) v_{out}=v_{op}-v_{om}=R\cdot (i_{D1}+i_{D2}-i_{D3}-i_{D4}) vout=vop−vom=R⋅(iD1+iD2−iD3−iD4)

考虑下图Multiplying Quad. Vx的DC voltage为VCM. Vy的DC voltage确保M1-M4在线性区.

Vthn1=Vthn2, Vthn4=Vthn2, 因此

v

o

u

t

=

R

β

⋅

v

x

v

y

v_{out}=R\beta \cdot v_{x}v_{y}

vout=Rβ⋅vxvy

在实际应用中, Vx的VCM越低越容易进入triode region, 但是限制了full-diff的op-amp的output voltage swing.

Multiplier Design Using Squaring Circuits

analog multiplier还可以通过利用电压平方律得到:

V

o

=

(

V

1

+

V

2

)

2

−

(

V

1

−

V

2

)

2

=

4

V

1

V

2

V_{o}=(V_{1}+V_{2})^{2}-(V_{1}-V_{2})^{2}=4V_{1}V_{2}

Vo=(V1+V2)2−(V1−V2)2=4V1V2

上图中M1,M4是source-follower, beta1=beta4 >> beta2=beta3. 几乎所有DC current流过M1和M4. 当input=0V(or whatever the common-mode voltage), Isq=0A

I

S

Q

(

a

)

=

β

23

4

(

V

1

+

V

2

)

2

I_{SQ(a)}=\frac{\beta_{23}}{4}(V_{1}+V_{2})^{2}

ISQ(a)=4β23(V1+V2)2

I S Q ( b ) = β 23 4 ( V 1 − V 2 ) 2 I_{SQ(b)}=\frac{\beta_{23}}{4}(V_{1}-V_{2})^{2} ISQ(b)=4β23(V1−V2)2

V o + = V D D − I S Q ( a ) R V_{o+}=VDD-I_{SQ(a)}R Vo+=VDD−ISQ(a)R

V o u t = V o + − V o − = R β 23 4 [ ( V 1 + V 2 ) 2 − ( V 1 − V 2 ) 2 ] V_{out}=V_{o+}-V_{o-}=R\frac{\beta_{23}}{4}[(V_{1}+V_{2})^{2}-(V_{1}-V_{2})^{2}] Vout=Vo+−Vo−=R4β23[(V1+V2)2−(V1−V2)2]

V o u t = R β 23 ⋅ V 1 V 2 V_{out}=R\beta_{23}\cdot V_{1}V_{2} Vout=Rβ23⋅V1V2

对于这种架构的乘法器主要担忧是在现代小尺寸CMOS工艺电流不遵循电压平方律定理.

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?