收集整理了一份《2024年最新物联网嵌入式全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升的朋友。

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

四、举个栗子

(1)Hi3516A 用户手册上,USB PCB 设计建议

为了保证良好的信号质量, USB 2.0 端口数据信号线按照差分线方式走线。为了达到USB 2.0 高速 480MHz 的速度要求,建议 PCB 布线设计采用以下原则:

差分数据线走线尽可能短、直,差分数据线对内走线长度严格等长,走线长度偏差控制在±5mil 以内。

差分数据线控制 90±10%的均匀差分阻抗。

差分数据线走线尽可能在临近地平面的布线层走线且不要换层。

差分数据线走线应有完整的地平面层作为参考平面,不能跨平面分割。

差分数据线走线应尽量用最少的过孔和拐角,拐角可考虑用圆弧或者 135 度角,避免直角,以减少反射和阻抗变化。

避免邻近其它高速周期信号和大电流信号,并保证间距大于 50mil,以减小串扰。

此外,还应远离低速非周期信号,保证至少 20mil 的距离。

REXT 电阻应该尽可能靠近 Hi3516A 侧。

(2)图文说明

USB是一种快速、双向、同步传输、廉价、方便使用的可热拔插的串行接口。由于数据传输快,接口方便,支持热插拔等优点使USB设备得到广泛应用。目前,市场上以USB2.0为接口的产品居多,但很多硬件新手在USB应用中遇到很多困扰,往往PCB装配完之后USB接口出现各种问题

比如通讯不稳定或是无法通讯,检查原理图和焊接都无问题,或许这个时候就需怀疑PCB设计不合理。绘制满足USB2.0数据传输要求的PCB对产品的性能及可靠性有着极为重要的作用。

USB协议定义由两根差分信号线(D+、D-)传输数字信号,若要USB设备工作稳定差分信号线就必须严格按照差分信号的规则来布局布线。根据笔者多年USB相关产品设计与调试经验,总结以下注意要点:

- 在元件布局时,尽量使差分线路最短,以缩短差分线走线距离(√为合理的方式,×为不合理方式);

- 优先绘制差分线,一对差分线上尽量不要超过两对过孔(过孔会增加线路的寄生电感,从而影响线路的信号完整性),且需对称放置(√为合理的方式,×为不合理方式);

- 对称平行走线,这样能保证两根线紧耦合,避免90°走线,弧形或45°均是较好的走线方式(√为合理的方式,×为不合理方式);

- 差分串接阻容,测试点,上下拉电阻的摆放(√为合理的方式,×为不合理方式);

- 由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,而线长一旦不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里;

五、阻抗匹配

(1)阻抗计算工具

上面一直提到,差分阻抗。这个怎么计算呢?推荐一款阻抗计算工具 Polar CITS25

1、软件下载

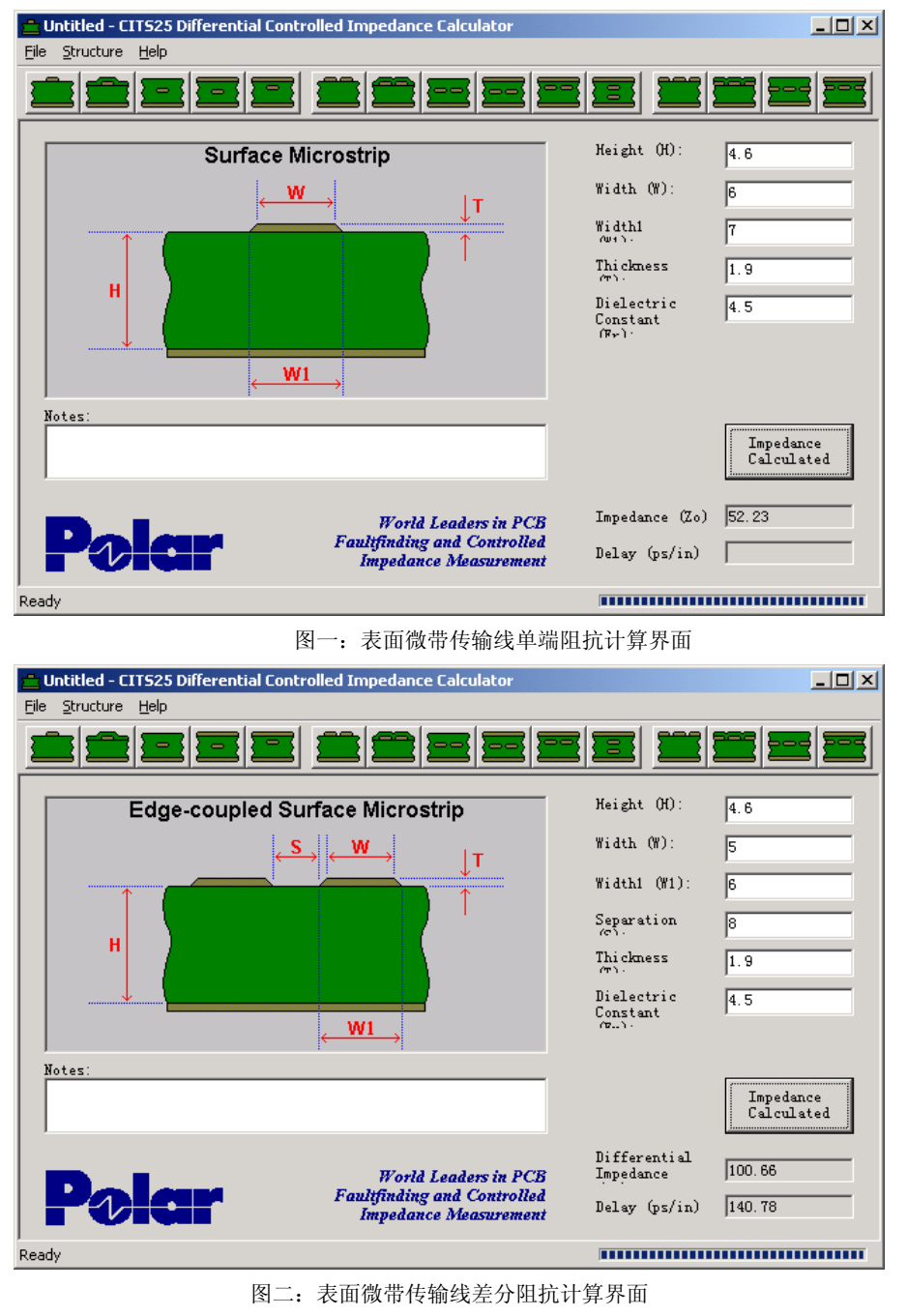

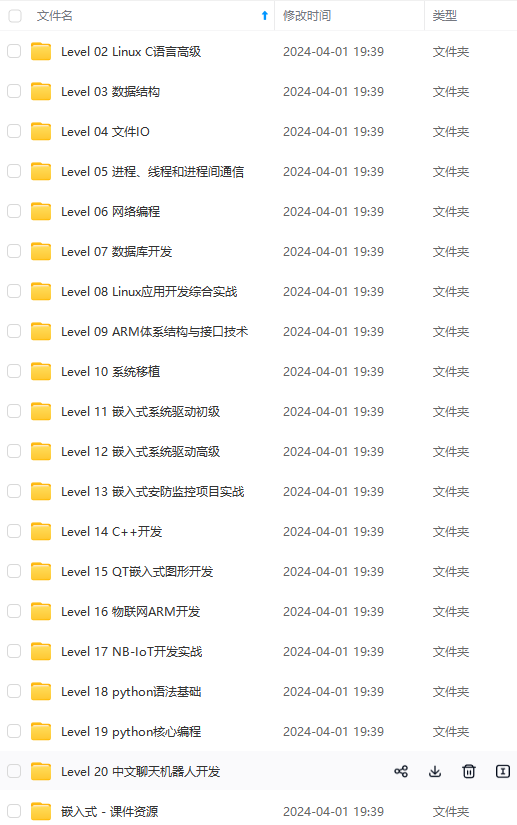

举个例子:

我们用一对 0.006 英寸宽, 1/2 盎司铜厚,间距为 0.01 英寸, FR4 材料作衬底,离地线层 0.005 英寸 (微带方式)的差分信号走线的差分阻抗计算作为例子,铜的厚度 T 为 0.7/1000 英寸。下图显示了各参数。

(单位换算:1Mil=千分之一英寸,约等于0.0254毫米;1 盎司 = 0.0014 英寸=0.7 mil)

H:介质厚度(PP片或者板材,不包括铜厚) (5)

W:阻抗线下线宽(W2=W1-0.5MIL) (6)

W1:阻抗线上线宽(客户要求的线宽) (6)

S:阻抗线间距(客户原稿) (10)

T:成品铜厚 (0.7)

Er1:PP片的介电常数(板材为:4.5 P片4.2) (4.2)

2、软件各个界面含义

该软件跟上面软件不同,但是参数差不多,仅供参考。

如果想下载下面的软件,参看:PCB特征阻抗计算神器Polar SI9000安装及破解指南

1. 外层单端:Coated Microstrip 1B

H1:介质厚度(PP片或者板材,不包括铜厚)

Er1:PP片的介电常数(板材为:4.5 P片4.2)

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

T1:成品铜厚

C1:基材的绿油厚度(我司按0.8MIL)

C2:铜皮或走线上的绿油厚度(0.5MIL)

Cer:绿油的介电常数(我司按3.3MIL)

Zo:由上面的参数计算出来的理论阻值

2.外层差分:Edge-Coupled Coated Microstrip 1B(重点)

H1:介质厚度(PP片或者板材,不包括铜厚)

Er1:PP片的介电常数(板材为:4.5 P片4.2)

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

S1:阻抗线间距(客户原稿)

T1:成品铜厚

C1:基材的绿油厚度(我司按0.8MIL)

C2:铜皮或走线上的绿油厚度(0.5MIL)

C3:基材上面的绿油厚度(0.50MIL)

Cer:绿油的介电常数(我司按3.3MIL)

3.内层单端:Offset Stripline 1B1A

H1:介质厚度(PP片或者光板,不包括铜厚)

Er1:H1厚度PP片的介电常数(P片4.2MIL)

H2:介质厚度(PP片或者光板,不包括铜厚)

Er2:H2厚度PP片的介电常数(P片4.2MIL)

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

T1:成品铜厚

Zo:由上面的参数计算出来的理论阻值

4.内层差分:Edge-Couled Offset Stripline 1B1A

H1:介质厚度(PP片或者光板,不包括铜厚)

Er1:H1厚度PP片的介电常数(P片4.2MIL)

H2:介质厚度(PP片或者光板,不包括铜厚)

Er2:H2厚度PP片的介电常数(P片4.2MIL)

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

S1:客户要求的线距

T1:成品铜厚

Zo:由上面的参数计算出来的理论阻值

5.外层单端共面地:Coated Coplanar Waveguide With Ground 1B

H1:介质厚度(PP片或者板材,不包括铜厚)

Er1:PP片的介电常数(板材为:4.5 P片4.2)

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

D1:阻抗线到两边铜皮的距离

T1:成品铜厚

C1:基材的绿油厚度(我司按0.8MIL)

C2:铜皮或走线上的绿油厚度(0.5MIL)

Cer:绿油的介电常数(我司按3.3MIL)

Zo:由上面的参数计算出来的理论阻值

6.外层差分共面地:Diff Coated Coplanar Waveguide With Ground 1B

H1:介质厚度(PP片或者板材,不包括铜厚)

Er1:PP片的介电常数(板材为:4.5 P片4.2)

W1:阻抗线上线宽(客户要求的线宽)

W2:阻抗线下线宽(W2=W1-0.5MIL)

S1:阻抗线间距(客户原稿)

D1:阻抗线到铜皮的距离

T1:成品铜厚

C1:基材的绿油厚度(我司按0.8MIL)

C2:铜皮或走线上的绿油厚度(0.5MIL)

C3:基材上面的绿油厚度(0.50MIL)

Cer:绿油的介电常数(我司按3.3MIL)

Zo:由上面的参数计算出来的理论阻值

(2)阻抗匹配

参看:PCB阻抗设计参考

参看:PCB迹线的阻抗控制技术

参看:PCB阻抗匹配总结

确实,一开始我也以为阻抗是写到 PCB 制版要求里,然后让制版厂来做的。

从上面的例子中就可以看到它与 差分线的线宽、线间距、介质厚度、成品铜****厚、****介电常数、叠层结构等有关。

差分线的线宽、线间距,这些都是在 PCB 规则里设置好的。只不过以前不晓得,为什么要设置成线宽 6 mil,间距 8 mil 等等这样的要求,还以为只是与制版价格有关呢。现在看来,它还和阻抗大小有关的!!

1、线宽、线间距规则设置

线宽:(最小线宽 5mil)

差分线间距:(差分线最小间距 10mil)

其他信号线间距:(最小线宽 7.5mil)

2、查看板卡厚度和叠层结构

**在 Design--Layer Stack Manager--thickness**

(3)传输线阻抗计算中的有关问题

上面参看的文档,讲的真好,看了一遍受益匪浅。不过内容较多,不一一分析了,下面只看一部分。

结合目前我公司 PCB 板加工厂家的工艺能力,在用 polar 公司阻抗计算器 CITS25 计算PCB 板上迹线特性阻抗时,对影响 PCB 板迹线控制阻抗的几个相关参数分述如下:

#### 1、 铜层厚度

铜层厚度代表了 PCB 迹线的高度 T。**内层铜箔通常情况下用到 1 OZ(厚度为 35 微米)**,也有在电源层要流过大电流时用到 2OZ(厚度为 70 微米)。**外层铜箔常用 1/2 OZ(18 微米)**,但由于经过板镀和图形电镀最终成品外层铜厚将达到48 微米(实际计算时用该值),设计成其他铜厚将较难控制铜厚厚度公差。若外层使用 1OZ铜箔,则最终铜厚将达到 65 微米。

#### 2、 PCB 板迹线的上下线宽

由于侧蚀的影响, PCB 迹线的截面为一梯形,上下线宽差距以 1mil 来计算,其中**下线宽****=要求线宽,而上线宽=要求线宽-1mil****。**

#### 3、 阻焊层

阻焊层厚度按 10um 为准(选择盖阻焊模式),但有机印后将会有所增厚,但其变化将基本不会带来阻抗值的变化。

#### 4、 介质厚度

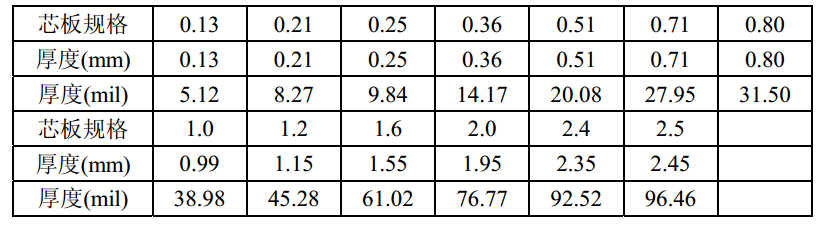

常用板材(芯板): (mm OZ/OZ \*表示其数值为不包括铜箔厚度的芯板厚度)

0.13\* 1/1 0.21\* 1/1 0.25\* 1/1 0.36\* 1/1

0.51\* 1/1 0.71\* 1/1 0.80\* 1/1

1.0 1/1 1.2 1/1 1.6 0.5/0.5 1.6 1/1 1.6 2/2

2.0 1/1 2.0 2/2 2.4 1/1 3.0 1/1 3.2 1/1

芯板在计算控制阻抗时的实际厚度:

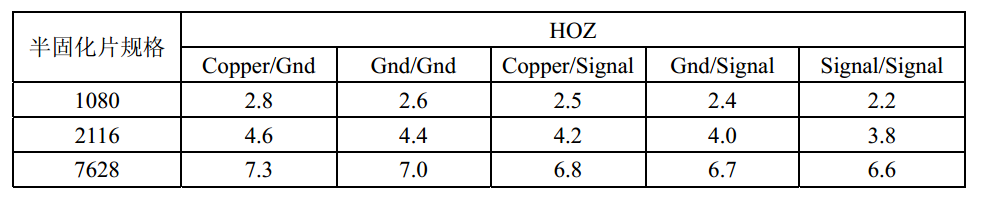

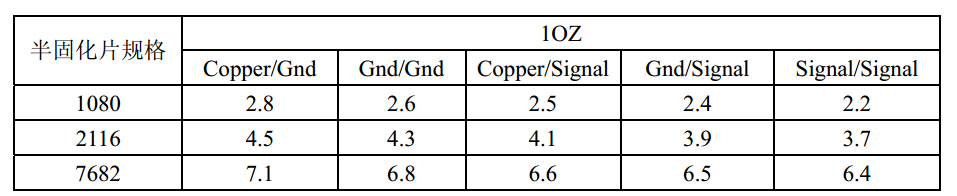

常用半固化片: (mm/mil)

7628: 0.175/6.9

**2116****:** **0.11/4.3**1080: 0.066/2.6

实际计算厚度时注意半固化片随着两面线路结构不同而有所不同:(mil)

其中 GND 层包括铜面积占 80%以上的线路层。如果介质在 HOZ 和 1OZ 铜箔之间,其厚度按 HOZ 情况计算。

#### 5、 介电常数

● Er 的值是线路板材质的绝缘常数(介电常数), 它对于线路的特性阻抗值而言是一个重要的组成部分。设计厂商因此有时会指定迹线阻抗值并依赖于线路板制造商来控制流程,以使迹线阻抗满足设计厂商指定的技术规范。

● 迹线的控制阻抗与板材介电常数的平房根成反比。

● 通过板材供应商提供的板材阻抗范围为 4.2~5.2,而**POLAR 公司建议单端采用 4.2,而差分若两线间距小会有所影响则建议采用 4.7****。**

● 根据一年多来各阻抗实验及生产板,我公司选用 4.2 进行计算能符合要求。

● 由于介电常数与板材型号和信号频率有相关性, 请设计人员能充分考虑该影响。如:高频板材有介电常数 2.5 等。

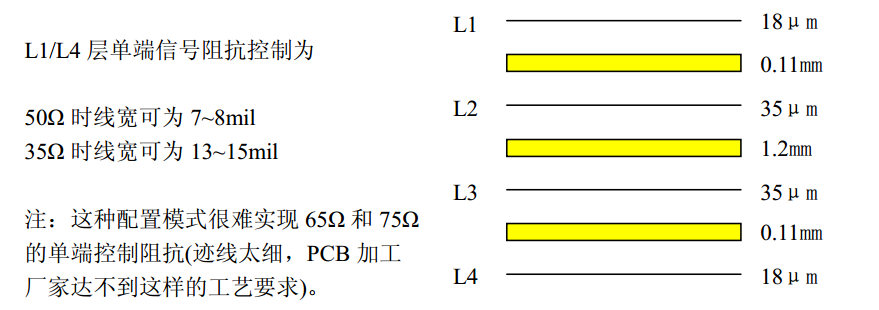

### (4)传输线阻抗控制典型应用总结

我们的制版要求,如果需要差分阻抗,一般会有这几个选项:

层数:4

板厚1.6mm,整板喷锡工艺。

阻抗匹配 目录中的图片信号需要100欧姆差分阻抗匹配。

严格禁止修改PCB图的任何东西的。

则 1.6mm 厚度的 4 层 PCB 板加工,建议做阻抗设计的时候按照 1.5mm 厚度进行设计,剩下 0.1mm 厚度留给工厂作为其他工艺要求用(后制诚厚度,绿油、丝印等)。

板厚 1.5mm(**采用** **1.2 35/35 的芯板,其余两个介质层为 2116**)。

L1/L4 层差分信号(阻抗控制为 100Ω)的线宽/间距可以为 5/5、 5/6、 6/7、**6/8**、 6/9(mil/mil)

L1/L4 层差分信号(阻抗控制为 75Ω)的线宽/间距可以为 10/7、 10/6、 11/9、 11/10、10/11(mil/mil)①

计算单端阻抗和差分阻抗的界面分别如下图一和图二:

L1 和 L2 层、 L3 和 L4 层之间的**介质层用** **2116**,模式为 Copper/Gnd(HOZ), 所以 **厚度** **H=4.6mil,介电常数为 4.5,外层铜厚为 1OZ(1.9mil)**。

实际板厚: 0.01+0.048+0.12+1.2+0.12+0.048+0.01=1.556mm。②

**既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!**

**由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新**

**需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)**

**[如果你需要这些资料,可以戳这里获取](https://bbs.csdn.net/topics/618679757)**

H=4.6mil,介电常数为 4.5,外层铜厚为 1OZ(1.9mil)**。

实际板厚: 0.01+0.048+0.12+1.2+0.12+0.048+0.01=1.556mm。②

[外链图片转存中...(img-0OqdEOhA-1715763517995)]

[外链图片转存中...(img-8SC4NZdF-1715763517996)]

**既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!**

**由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新**

**需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)**

**[如果你需要这些资料,可以戳这里获取](https://bbs.csdn.net/topics/618679757)**

4354

4354

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?