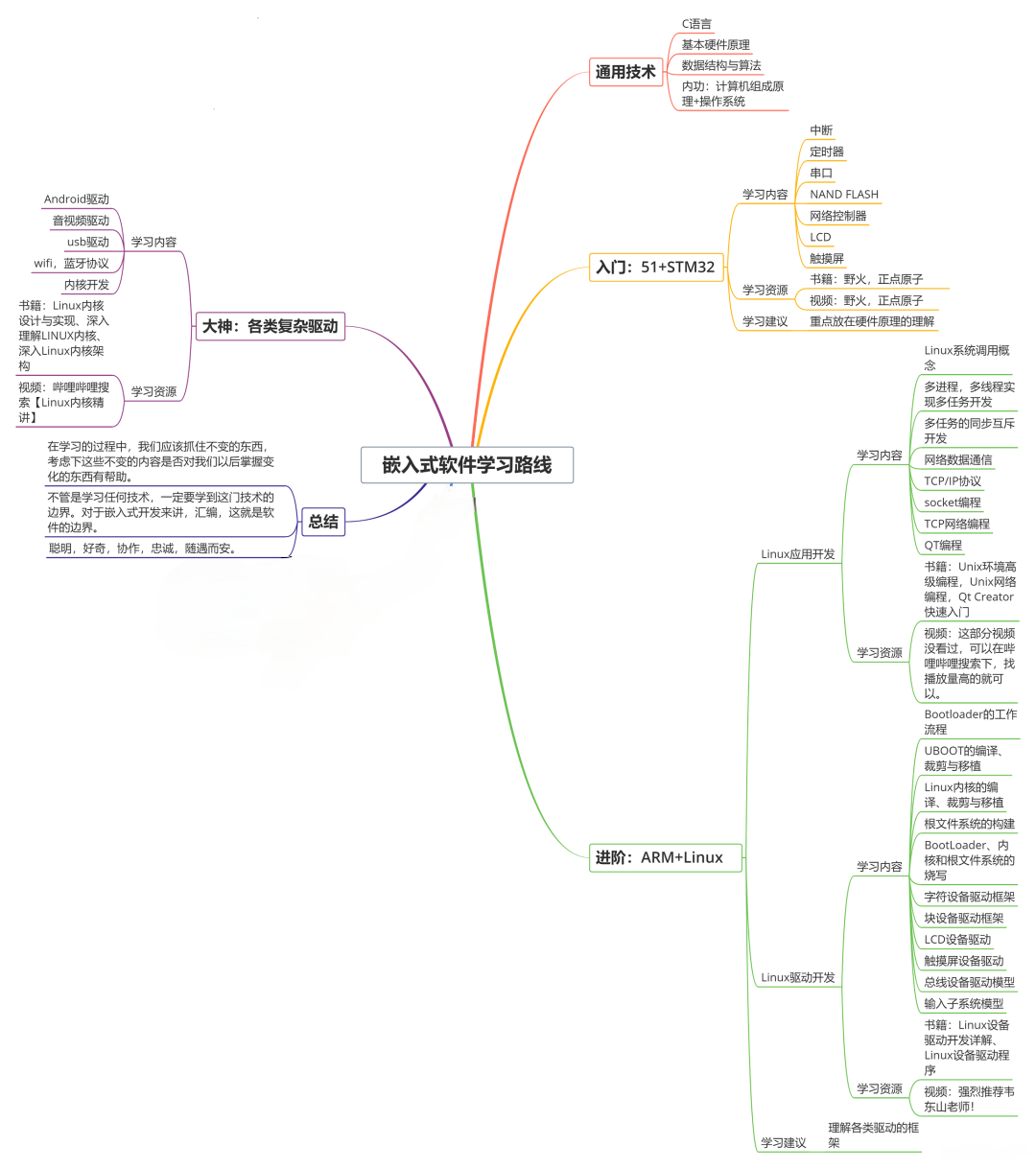

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

上一课:

【小黑嵌入式系统第二课】嵌入式系统的概述(二)——外围设备、处理器、ARM、操作系统

下一课:

【小黑嵌入式系统第四课】嵌入式系统硬件平台(二)——I/O设备、通信设备(UART&USB&蓝牙)、其他(电源&时钟&复位&中断)

文章目录

一、概述

嵌入式系统的硬件除了核心部件——嵌入式处理器,还包括存储器系统、外围接口部件以及连接各种设备的总线系统。

其中,存储器是嵌入式系统存放数据和程序的功能部件;

而外围设备决定了应用于不同领域的嵌入式系统的独特功能。

嵌入式系统的硬件是 以嵌入式处理器为中心,由存储器、I/O单元电路、通信模块、其它外部设备 等必要的辅助接口组成。

在实际应用中,嵌入式系统硬件配置非常精简,除了微处理器和基本的外围电路以外,其余的电路可以根据需要和成本进行裁剪、定制。

通常,嵌入式系统还包括人机交互界面,用于系统与人的交互。人机界面常常使用键盘、液晶屏、触摸屏等部件,以方便与人的交互操作。

存储器是构成嵌入式系统硬件的必要组成部分。在嵌入式系统中使用的存储器可以只是内部存储器,也可以包含外部存储器。

嵌入式处理器工作时必须有附属电路支持。在设计其硬件电路时,常常将它们与嵌入式处理器设计成一个模块,形成处理器子系统。

嵌入式处理器在功能上与通用处理器的区别之一在于嵌入式处理器上集成了大量的I/O电路。用户在开发时,根据系统需求选择某款嵌入式处理器,而不是让嵌入式处理器另外选择配合外围的大量I/O电路。

二、总线

1. 总线的概念

**总线(Bus)**是计算机各种功能部件之间传输信息的公共通信干线,它是由导线组成的传输线束。根据所传输的信息种类,计算机的总线可以划分为 数据总线、地址总线和控制总线 ,分别用来传输数据、数据地址和控制信号。

所有微机系统的总线结构,不外乎有“冯·诺伊曼”和“哈佛”两种。

1.1 总线结构

- 冯·诺伊曼总线结构将程序存储器和数据存储器合在一起管理,采用同一套地址和数据总线对它们进行寻址。因此总线就特别繁忙,成为提高运行速度的“瓶颈”。但在使用上非常灵活。

- 哈佛总线结构采用两套总线分别控制程序存储器和数据存储器,分别读取程序代码和存取数据。

☆ 降低了总线繁忙程度和指令执行的时间。

☆ 哈佛结构使得指令的执行时间相等,提高了控制性能。

- 改进型哈佛总线结构 虽然也使用两个不同的存储器:程序存储器和数据存储器,但合并了两个存储器的地址总线,数据总线也进行了合并,即原哈佛结构需要4条不同的总线,改进后需要两条总线。

☆ 使用两个独立的存储器模块,分别存储程序指令和数据,每个存储模块都不允许指令和数据并存,以便实现并行处理;

☆ 具有一条独立的地址总线和一条独立的数据总线,利用公用地址总线访问两个存储模块(程序存储模块和数据存储模块),公用数据总线则用来完成程序存储模块或数据存储模块与CPU之间的数据传输;

☆ 两条总线由程序存储器和数据存储器分时共用。

1.2 总线类型

1.2.1 数据总线

数据总线的宽度又称为计算机的“位数”,是计算机系统一个最重要的参数。原因是数据总线的宽度表明了计算机系统能够一次(单指令)处理的数据的范围,代表了计算机系统处理数据的能力。

如:MCS-51单片机的数据总线宽度为8位,ARM Cortex-M3的数据总线宽度为32位。

1.2.2 程序总线

决定了CPU每次能够从程序存储器取出多少位的指令,或者说一条指令中能够含有多少信息。因此程序总线的宽度在很大程度上决定了计算机系统指令集的效率。

1.2.3 数据地址总线

数据地址总线配合数据总线,对数据存储器进行寻址。其宽度决定了CPU能够寻址的数据存储器的多少。

1.2.4 程序地址总线

程序地址总线配合程序总线,对程序存储器进行寻址。程序地址总线的宽度决定了微处理器理论上能够含有的程序存储器的多少。

以上概念主要描述的是并行通信总线,对于串行通信总线,则情况会有较多区别。

不管怎样,总线是各种功能部件之间传输信息的公共通道,总线上所接的功能部件一定是可以多于2个的。

2. 总线协议

2.1 握手协议

- 总线握手协议的作用是控制每个总线周期中数据传送的开始和结束,从而实现两个设备间协调和配合,保证数据传送的正确和可靠。

- 这是因为总线上连接有多个通信设备,它们之间若随意在总线上传送数据必然会导致冲突。

最简单的握手使用两根用来进行握手的电线enq(表示查询)和ack(表示应答),并使用专用的电线来传输数据。 - 握手信号线必须以某种方式的信号变化来表明整个总线传输周期的开始和结束,以及在整个周期内每个子周期(若有)的开始和结束。

总线握手协议中的基本构件是 四周期握手协议 。

2.2 总线读写

- 微处理器总线在握手基础上为CPU和系统其它部分建立通信。基本的总线操作包括读和写。

- 总线行为经常用时序图来说明,时序图表示了总线上的信号如何随时间变化。

- 在许多系统中,总线上也可执行突发数据传输。

- 总线事务的状态机是对时序图的有效补充。

- 当CPU决定执行一个读事务,它转换到新状态,并发给让设备正确工作的总线信号;而设备状态转换图捕获它这一端的总线协议状态。

2.3 DMA

关于DMA的文章:【物联网】DMA传输原理与实现详解(超详细)

某些数据传输可能并不需要CPU介入,如I/O设备和存储器之间的数据交换。要实现这类操作,就要求有CPU以外的设备单元能够控制总线上的操作。

- 直接存储器访问(Direct Memory Access,DMA)允许不由CPU控制的总线读写操作。

虽然名字上有“存储器”,但DMA也可以适用于映射到地址空间上的别的I/O设备。 - DMA使用一种称为DMA控制器的专用硬件来完成外设与存储器之间的高速数据传送。

- DMA控制器向CPU请求总线控制,当CPU不需使用总线传输数据时,则DMA控制器得到总线控制权,它能像CPU那样提供存储地址和必要的读写控制信号,实现直接在设备和存储器之间执行读写操作。

DMA控制器、CPU都可以发起总线数据传输,它们被称为总线主设备,总线上的其它设备则称为总线从设备。

总线在一段时间内只能由一个主设备控制使用,若多个总线主设备同时需要使用总线,此时需要“仲裁”,由仲裁器决定哪一个使用。

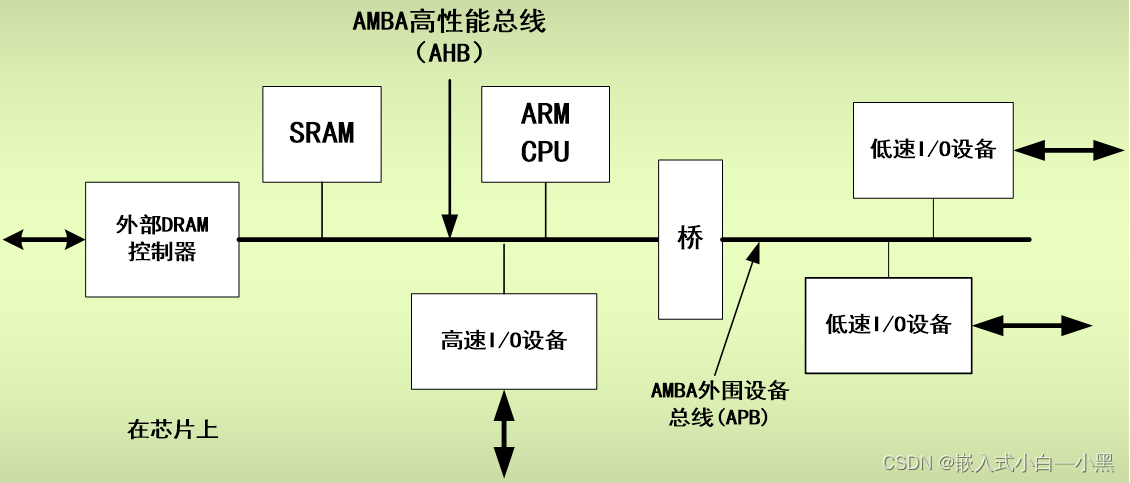

2.4 多总线系统

- 一个微处理器系统可能使用多条总线来连接设备。

- 使用这样的总线配置主要考虑到以下几个原因:

1、高速总线通常提供较宽的数据连接。

2、高速总线通常要更昂贵的电路和连接器,可以通过使用较慢的、比较便宜的总线来降低低速设备成本。

3、桥允许总线独立操作,因此可以在I/O操作中提供并行性。

2.5 多总线系统实例

ARM AMBA(Advanced Microcontroller Bus Architecture)总线系统

三、存储设备

存储设备更加详细文章:【物联网】ROM、RAM和FLASH的区别

存储器用来存放计算机工作所必须的数据和程序,在嵌入式系统中普遍使用。

嵌入式微处理器在运行时,大部分总线周期都是用于对存储器的读/写访问。存储器系统性能的好坏将在很大程度上影响嵌入式系统的性能。

为了追求存储器的高性能,一方面要从存储单元的设计、制造上研究改进(Flash、NVRAM) ;另一方面从存储器系统的结构上探索、优化(3D堆叠,多通道)。

- 嵌入式系统存储器子系统的结构 :

- RAM

- ROM

- Flash

3.1 嵌入式系统存储器子系统的结构

- 嵌入式系统的存储器子系统与通用计算机的存储器子系统的功能并无明显的区别。

- 这决定了嵌入式系统的存储器子系统的设计指标和方法也可以采用通用计算机的方法,尤其是嵌入通用计算机的大型嵌入式系统更是如此。

- 存储器子系统设计的首要目标是使存储器在工作速度上很好地与处理器匹配,并满足各种存取需要。

存储器子系统设计的首要目标是使存储器在工作速度上很好地与处理器匹配,并满足各种存取需要。

- 大量使用高速存储器,使它们在速度上与处理器相吻合,能够简便地解决问题,但受到经济上的限制。

在实际的计算机系统中,总是采用分级的方法来设计整个存储器子系统。 - 全部存储系统分为四级,即寄存器组、高速缓存、内存和外存。它们在存取速度上依次递减,而在存储容量上逐级递增。

存储的分层体系:

存储的分层体系:

寄存器组:

寄存器组是最高一级的存储器。

- 在计算机设备中,寄存器组一般是CPU内含的,ARM处理器中有37个寄存器。

- 有些待使用的数据或者运算的中间结果可以暂存在这些寄存器中。

- 微处理器在对CPU内的寄存器读写时,速度很快,一般在一个时钟周期内完成。

- 从总体上说,设置一系列寄存器是为了尽可能减少微处理器从外部取数的次数。

- 但由于寄存器组是制作在CPU内部的,受芯片面积和集成度、以及指令系统的限制,寄存器的数量不可能做得很多。

高速缓冲存储器(Cache):

第二级存储器是高速缓冲存储器(Cache)。

- 高速缓存是一种小型、快速的存储器,其存取速度足以与微处理器相匹配。

- 高速缓存保存部分内存内容的拷贝,这部分内容应是被高频率使用的。如果正确使用,它能够减少内存平均访问时间。

内存:

第三级是内存。

- 运行的程序和数据都放在内存中。

- 如果微处理器的访问大部分在高速缓存上,内存就可以采用速度稍慢的存储器,对系统性能的影响不会太大,同时又降低了成本。

- 内存除主要使用RAM外,还要使用一定量的ROM。

外存:

最低一级存储器是大容量的外存。

- 这种外存容量大,但是在存取速度上比内存要慢得多。

- 目前嵌入式系统中常用闪存作为大容量“硬盘”存储各种程序和数据。

3.2 RAM

随机存取存储器(Random Access Memory,RAM)能够随时在任一地址读出或写入内容。

- RAM的突出优点是读写方便、使用灵活。缺点是不能长期保存信息,一旦停电,所存信息就会丢失。但维持静态数据所需的功耗通常较低。

- RAM用于数据的临时存储或缓冲存储,在嵌入式系统中主要用于:

- 存放当前正在执行的程序和数据,如用户的调试程序、程序的中间运算结果以及掉电时无需保存的I/O数据和参数等。

收集整理了一份《2024年最新物联网嵌入式全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升的朋友。

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

新物联网嵌入式全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升的朋友。**

[外链图片转存中…(img-1xw4YNWK-1715798035875)]

[外链图片转存中…(img-lBfIQlfL-1715798035875)]

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

4733

4733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?