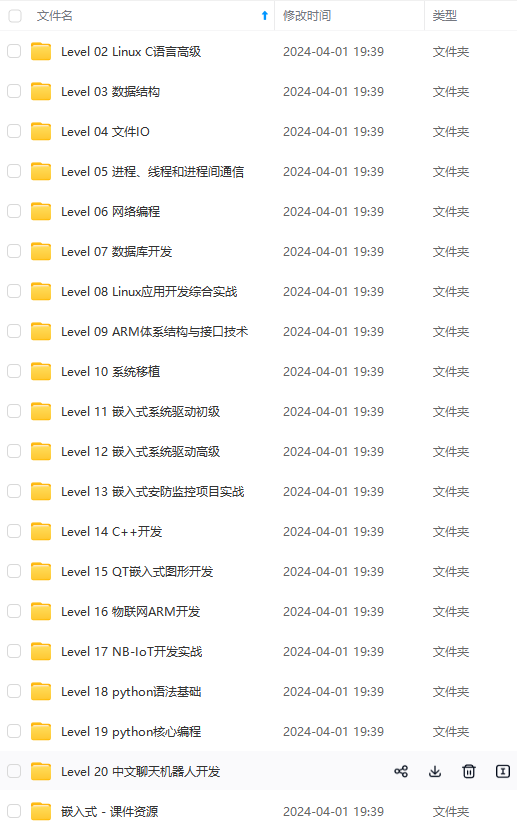

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

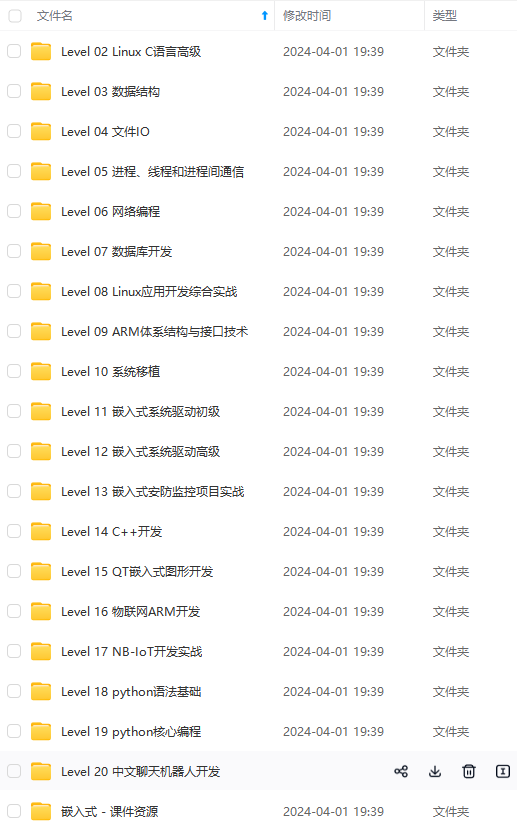

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

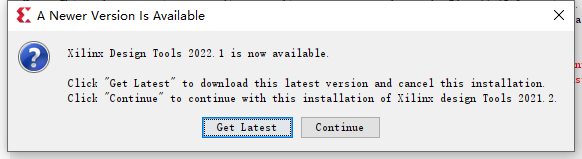

(2)弹出下面的提示,选择“continue”

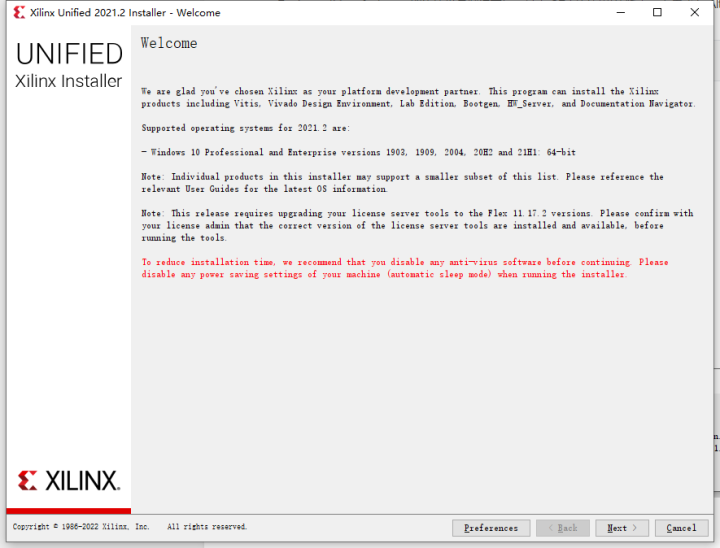

(3)点击“next”即可

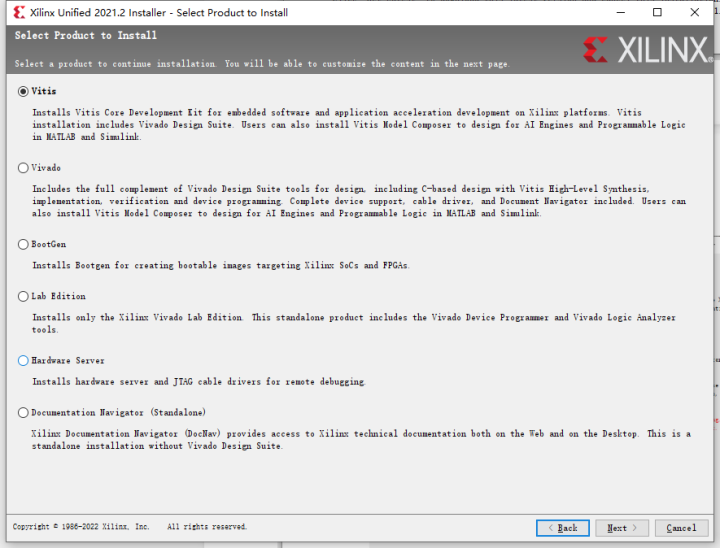

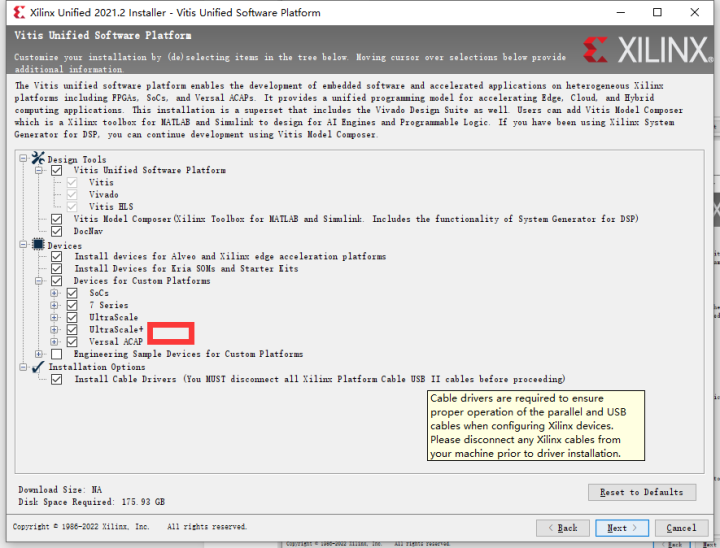

(4)选择安装的芯片型号,对于不需要的芯片型号,可以不选,降低安装空间占用

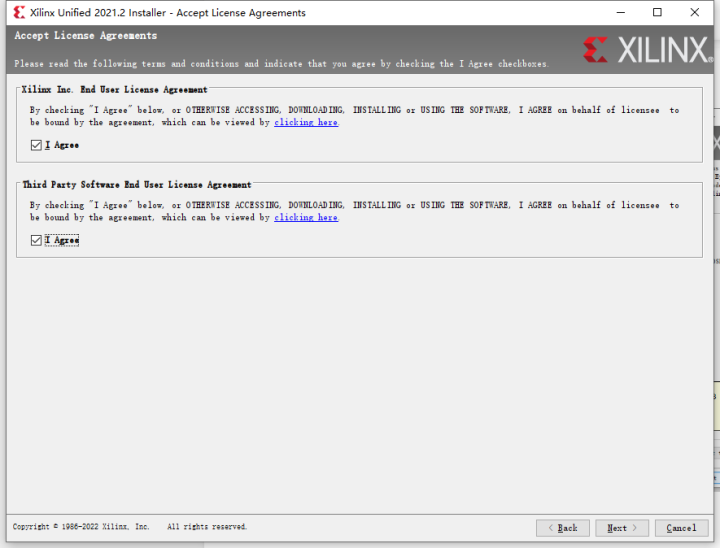

(5)选中“I agree”,点击“next”

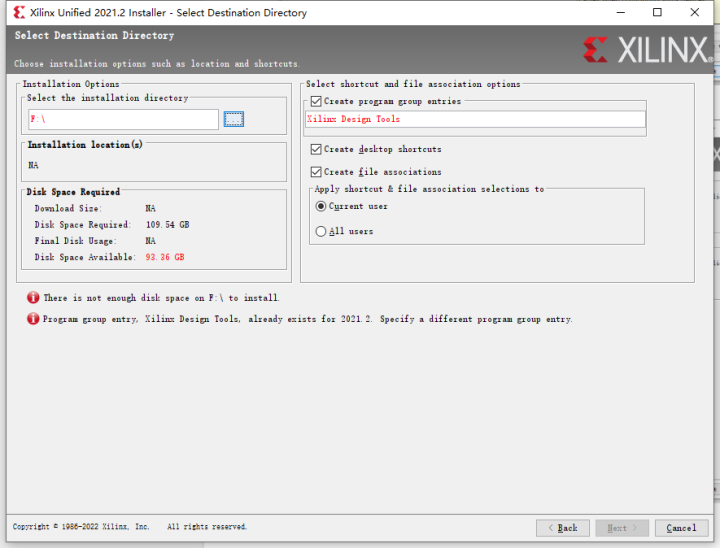

(6)选择“安装目录”,点击“next”

(7)等待安装完毕,即可。

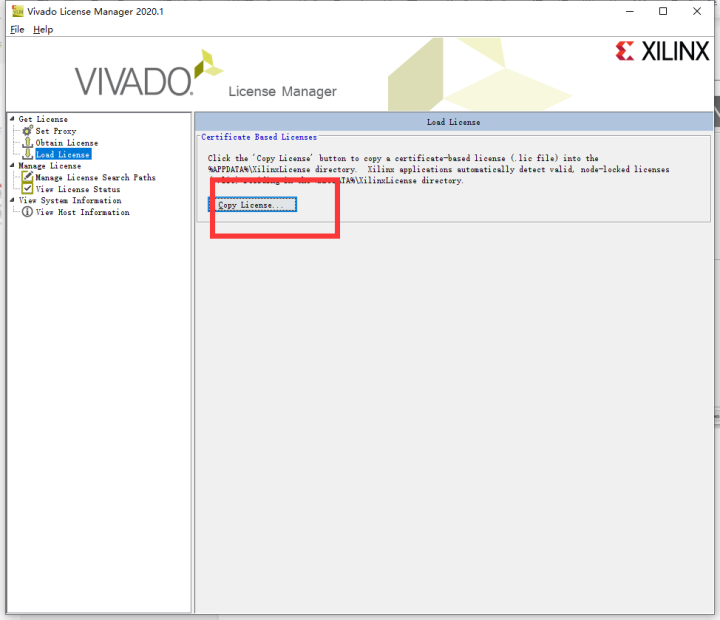

(8)license加载,打开“Manage xilinx license s”,点击“Load license”,点击“Copy License”,选择加载license文件即可

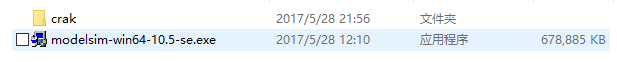

2、modelsim安装

(1)点击“modesim.exe”文件

(2)一直点击下一步安装即可

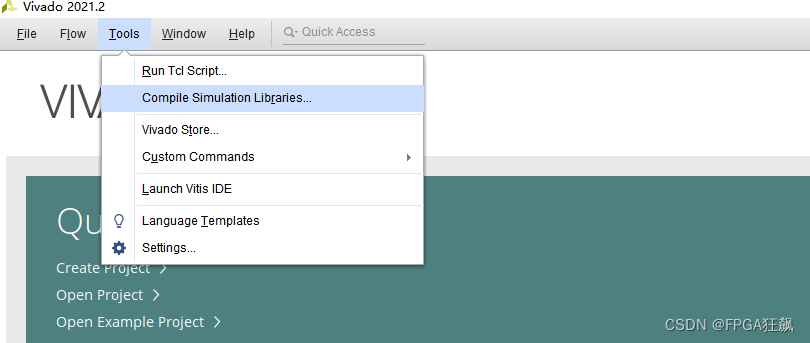

3、vivado中配置modesim仿真设置

(1)在Vivado中生成lib

打开Vivado软件,点击Tools-》Compile Simulation Libraries,生成库函数

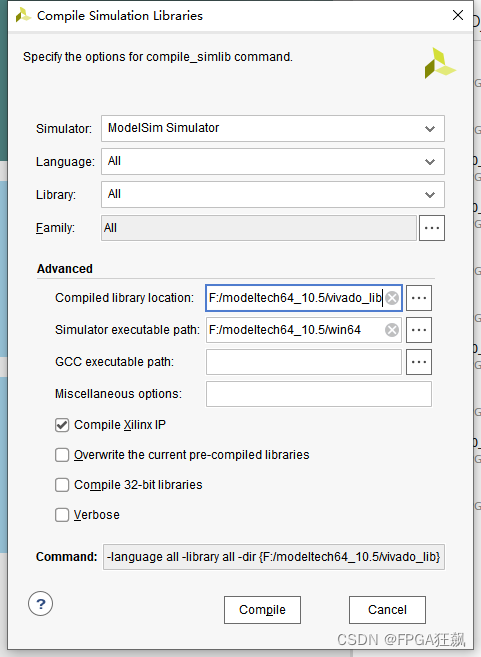

生成库函数设置

Simulator选择ModelSim Simulator

Language,Library,Family选择全部(All)

Compiled library location:编译库目录,可以选择在ModelSim的安装路径下,新建一个Vivado_lib的文件夹

Simulator executable path:选择ModelSim的启动路径

点击Compile,即可开始生成库文件,等待编译完毕。

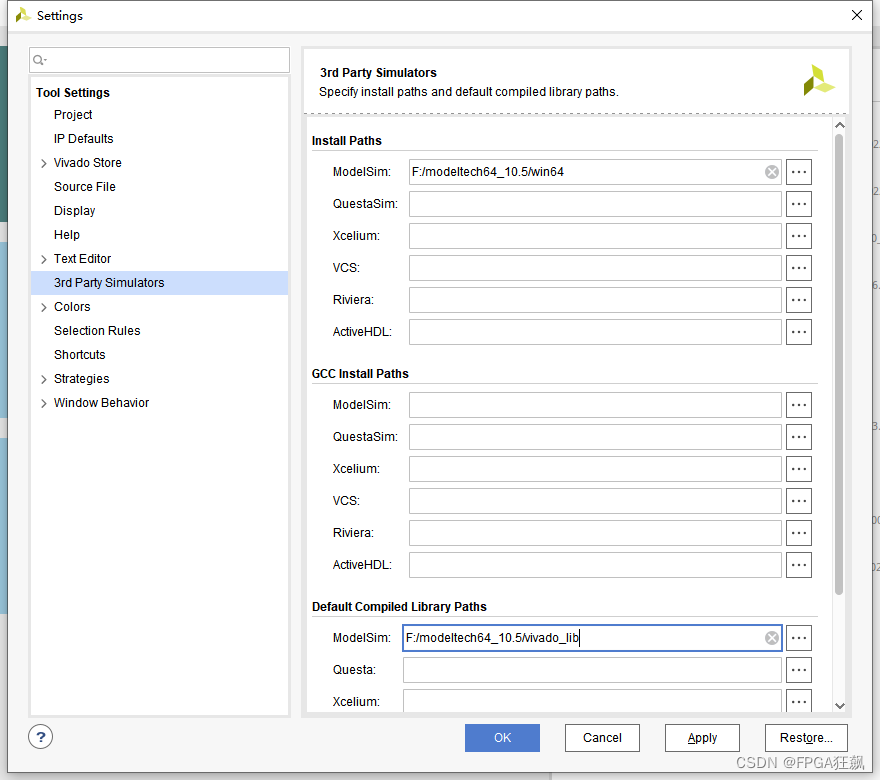

(2)在Vivado中添加ModelSim调用设置

Vivado --> Tools --> setting,分别设置仿真软件和仿真库

(3)在ModelSim中添加Vivado仿真库

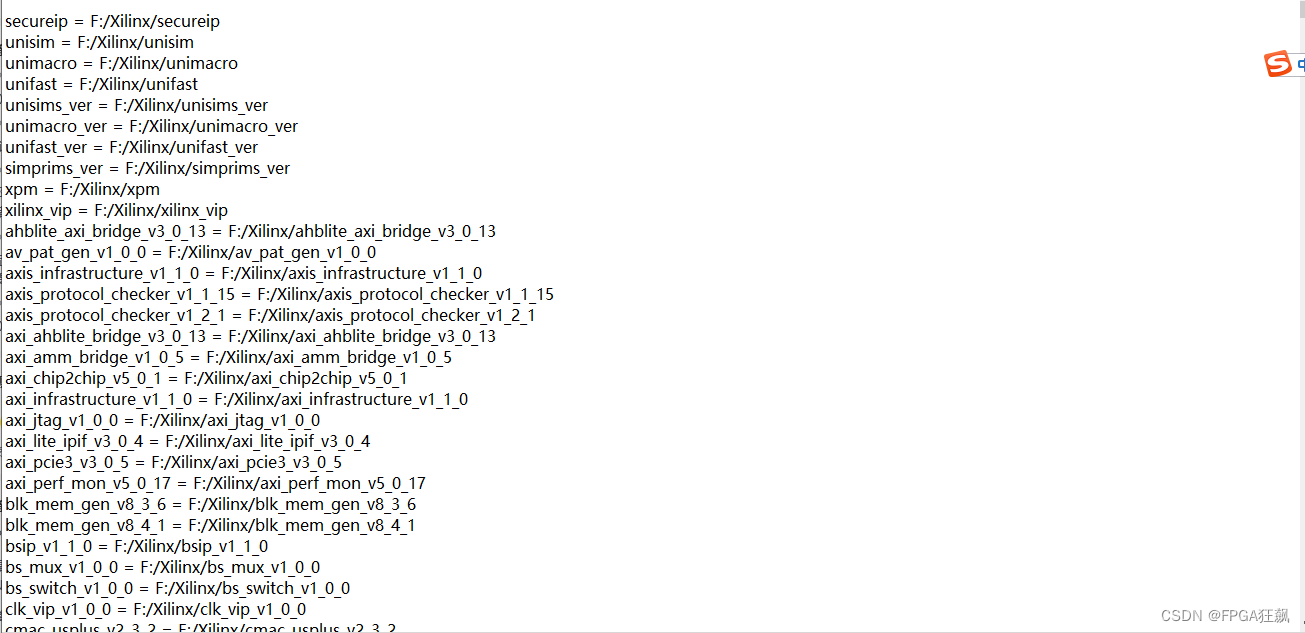

a、在modelsim安装目录下的vivado仿真库文件夹vivado_lib下找到modelsim.ini文件,打开如下图所示的库路径

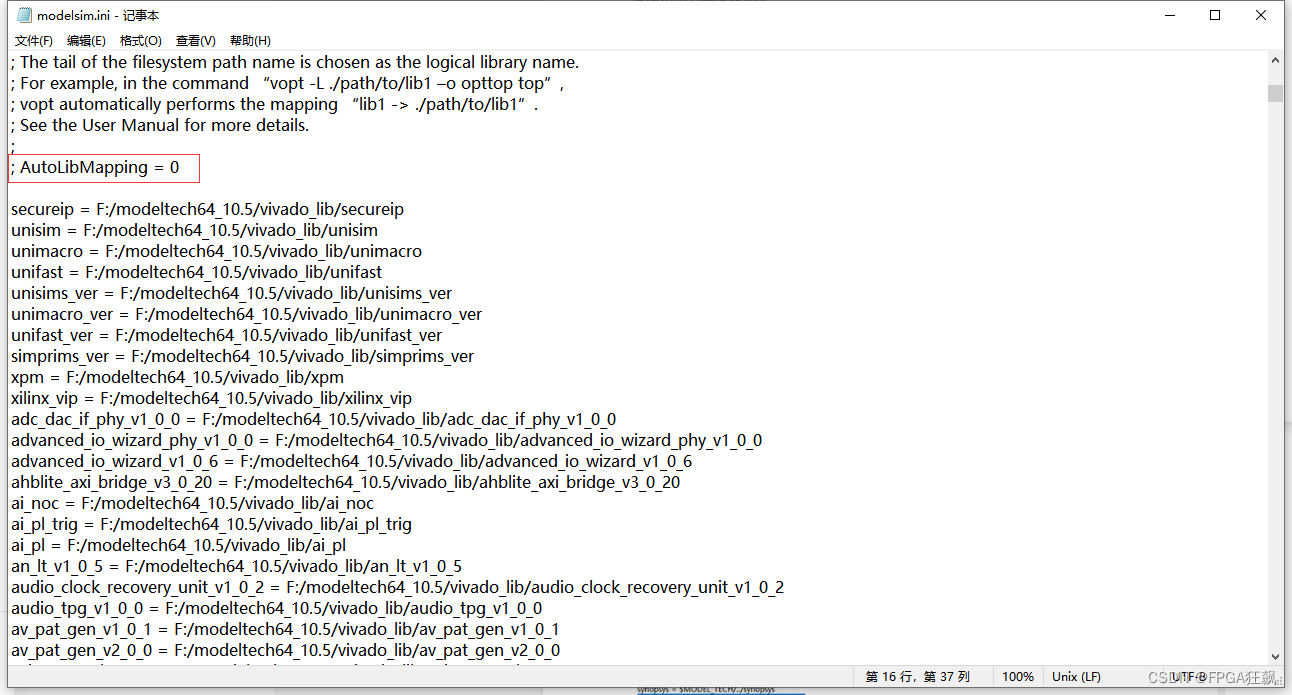

b、在modelsim安装路径下有一个modelsim.ini文件,取消只读属性,然后用记事本将其打开,找到“; AutoLibMapping = 0”处准备添加ip库路径

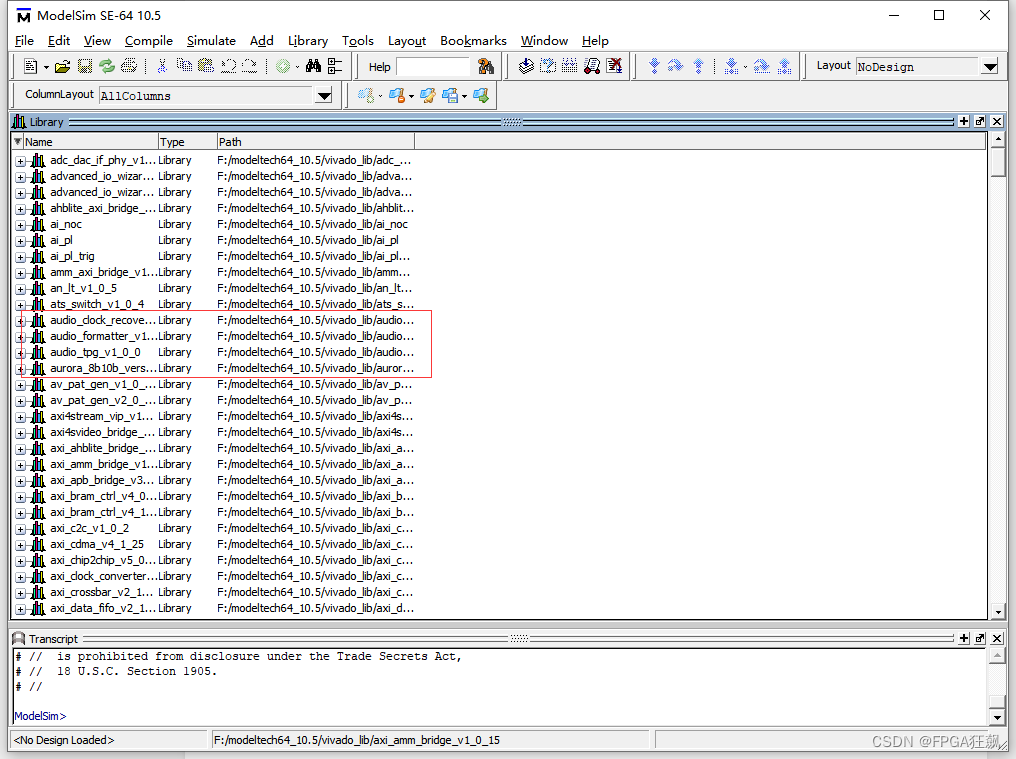

(4) 打开ModelSim,就会Vivado的lib全部添加到ModelSim中添加进来了。

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!**

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

655

655

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?