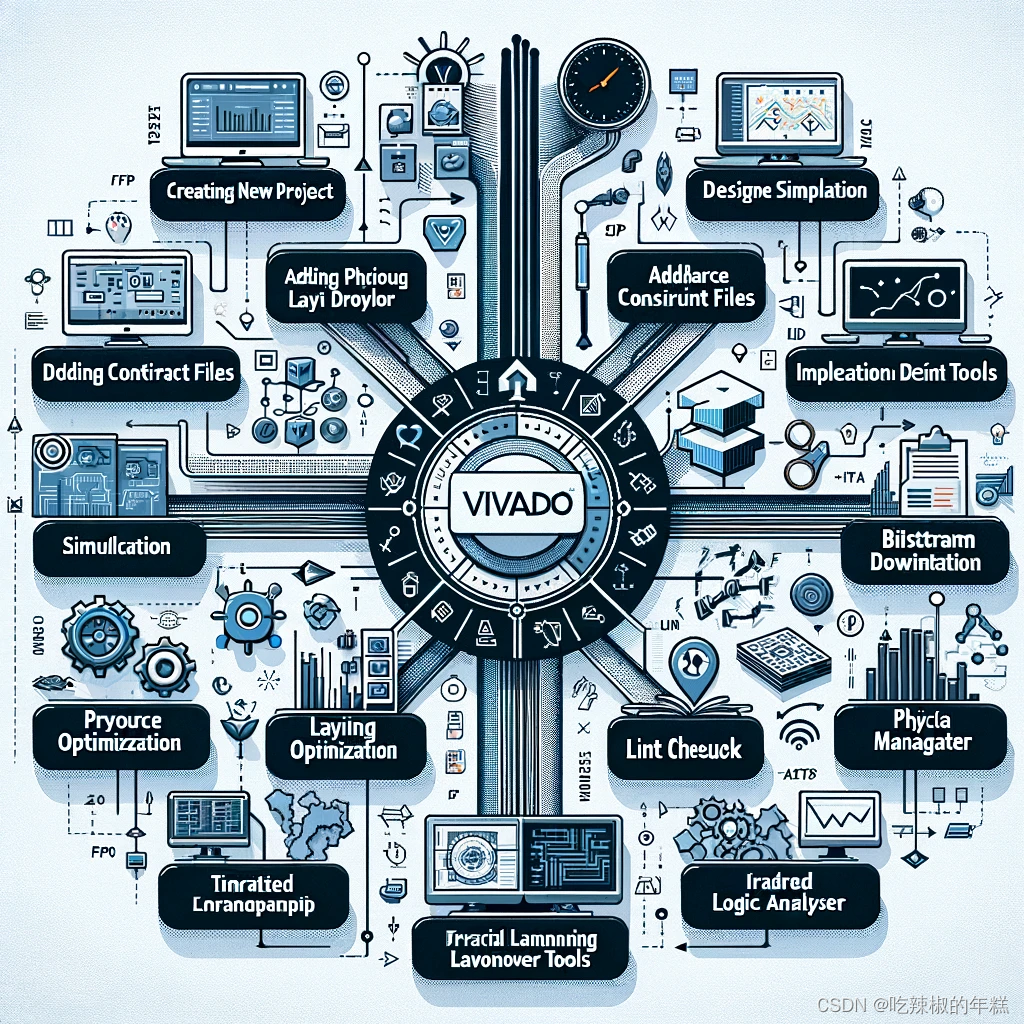

Vivado 是 Xilinx 公司推出的一款用于 FPGA 设计的集成开发环境 (IDE),提供了从设计输入到实现、验证、调试和下载的完整流程。本文将详细介绍 Vivado 的使用方法,包括项目创建、设计输入、约束文件、综合与实现、仿真、调试、下载配置等步骤。

一、创建新项目

1.1 启动 Vivado

打开 Vivado 应用程序,进入欢迎界面。

1.2 创建新项目

- 在欢迎界面选择“Create New Project”。

- 输入项目名称和路径。

- 选择“RTL Project”,并勾选“Do not specify sources at this time”。

- 选择目标器件(如 XC7Z020-1CLG484)。

- 点击“Finish”完成项目创建。

二、设计输入

2.1 添加设计源文件

- 在 Flow Navigator 面板中,选择“Add Sources”。

- 选择“Add or Create Design Sources”并点击“Next”。

- 点击“Create File”以创建新的 Verilog 或 VHDL 文件。

- 输入文件名并选择文件类型(Verilog/VHDL)。

- 点击“Finish”完成文件创建。

2.2 编辑设计源文件

- 在 Sources 面板中,双击新创建的源文件以打开编辑器。

- 编写设计代码。例如,以下是一个简单的 Verilog 模块:

module led_blink (

input wire clk,

input wire rst,

output reg led

);

reg [23:0] counter;

always @(posedge clk or posedge rst) begin

if (rst) begin

counter <= 24'd0;

led <= 1'b0;

end else begin

counter <= counter + 1;

if (counter == 24'd9999999) begin

counter <= 24'd0;

led <= ~led;

end

end

end

endmodule

三、添加约束文件

3.1 添加约束文件

- 在 Flow Navigator 面板中,选择“Add Constraints”。

- 选择“Create File”并命名文件(如“constraints.xdc”)。

- 点击“Finish”完成文件创建。

- 在 Sources 面板中,双击新创建的约束文件以打开编辑器。

- 添加引脚约束。例如:

set_property PACKAGE_PIN W5 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN U16 [get_ports rst]

set_pro

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

944

944

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?