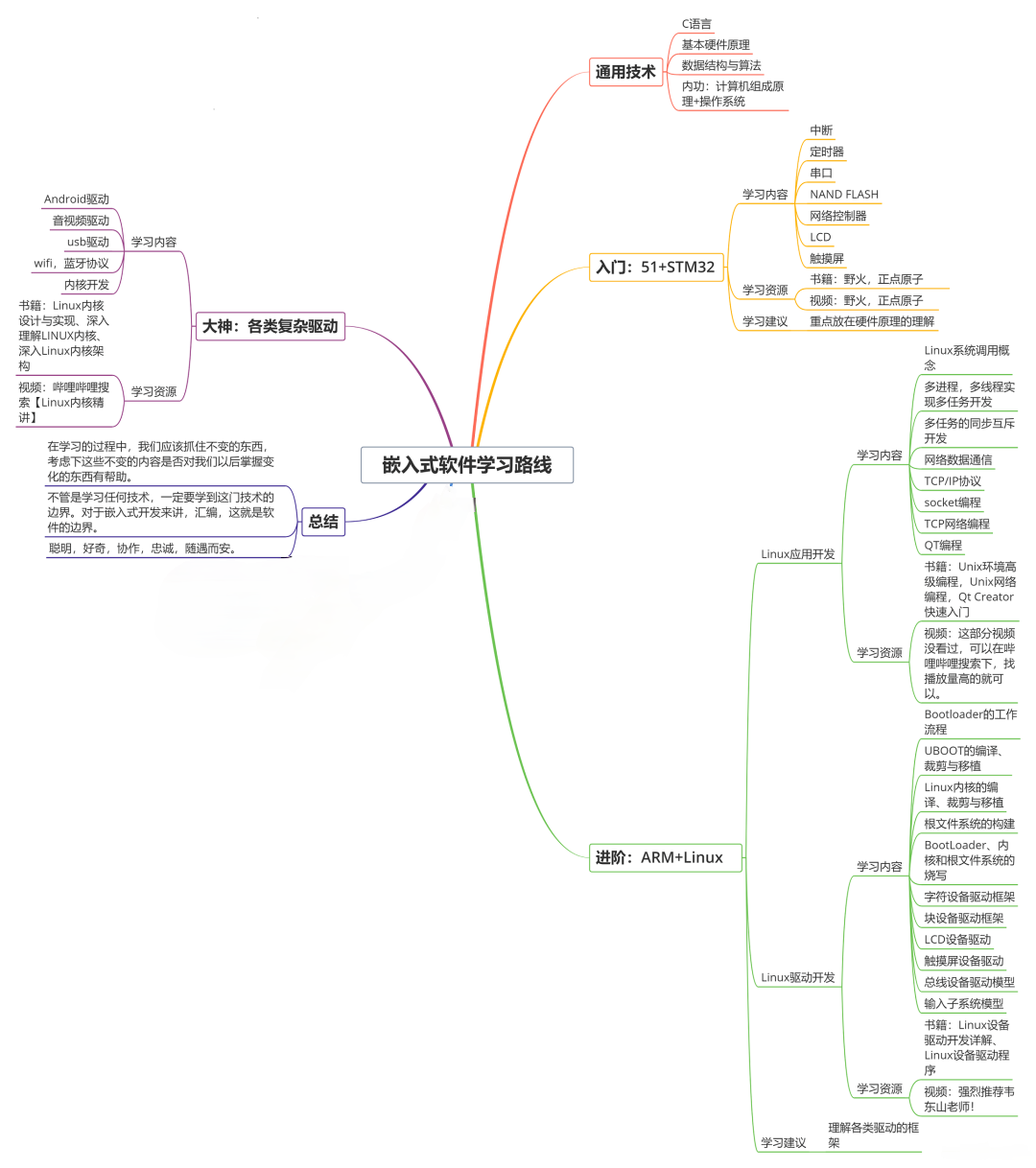

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上物联网嵌入式知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、电子书籍、讲解视频,并且后续会持续更新

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

1.3.2 Posted 和 Non⁃Posted 传送方式

1.PCI基础知识

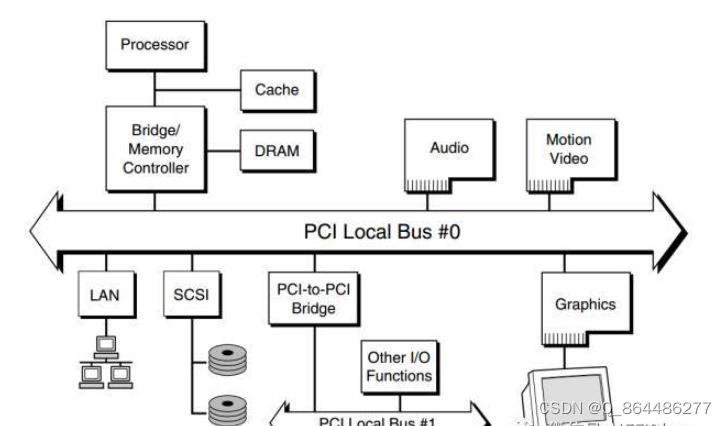

PCI 总线作为处理器系统的局部总线, 其主要目的是为了连接外部设备, 而不是作为处理器的系统总线连接 Cache 和主存储器。

在今天来看PCI总线许多概念略显过时,但是当年与ISA、EISA和MAC相比,具备很多优点:

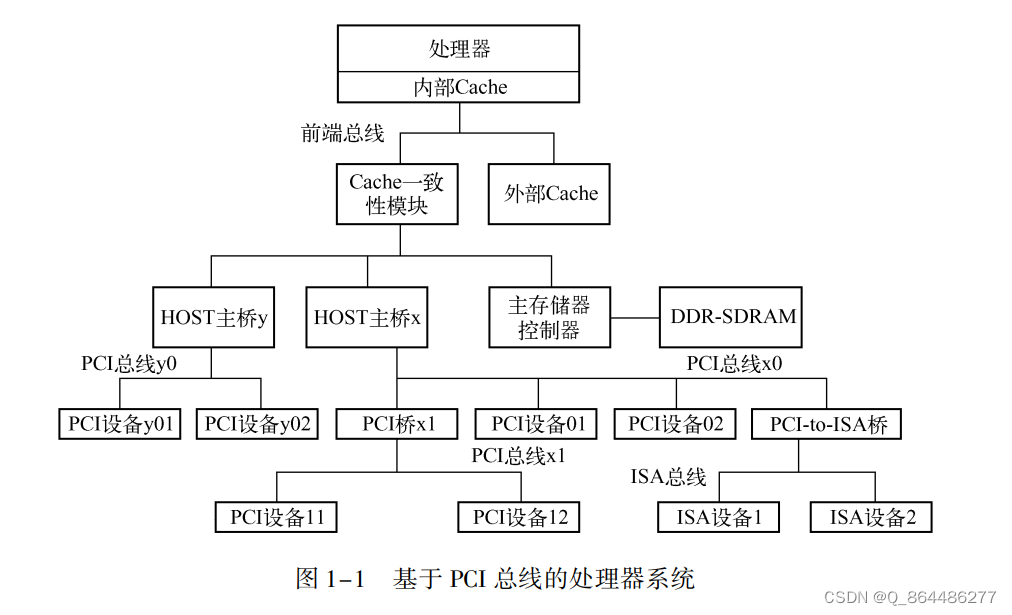

(1)PCI总线空间与处理器空间隔离

用HOST主桥对PCI总线空间和存储器空间进行区分,这两个空间进行通信要经过HOST主桥将地址进行转换。

(2)PCI具备扩展性

HOST主桥可以作为根,然后可以分出PCI桥,其又可以连接更多的设备;但是在1 棵 PCI 总线树上, 最多只能挂接 256 个 PCI 设备 (包括 PCI 桥)。

(3)动态配置机制

PCI 设备使用的地址可以根据需要由系统软件动态分配。

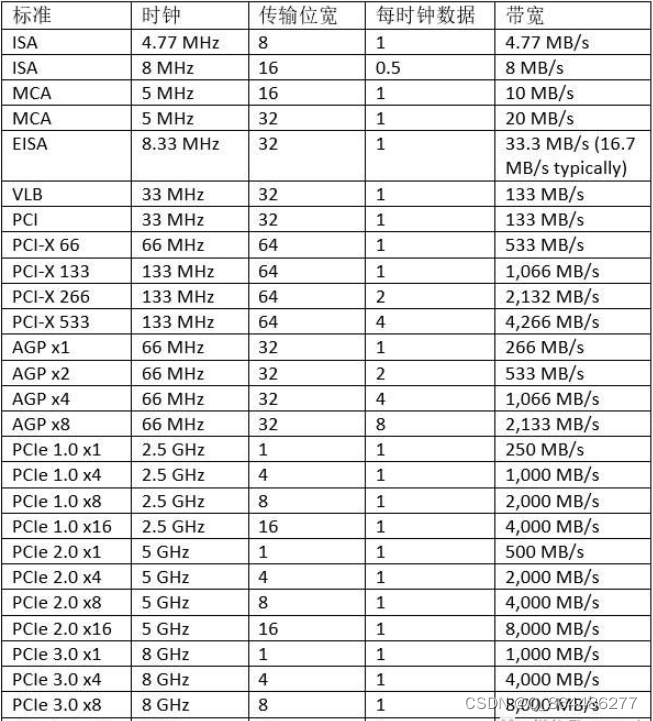

(4)总线带宽,PCIE更快

(5) 共享总线机制

PCI设备通过仲裁获得总线控制后,都会在总线上进行数据传输。PCI 总线仲裁器不在 PCI 总线规范定义的范围内, 也不一定是 HOST 主桥和 PCI 桥的一部分。这种占用总线的机制不如 PCIe 总线采用的交换结构。

(6)中断机制

PCI 总线上的设备可以通过四根中断请求信号 INTA ~ D#向处理器提交中断请求。

1. 1 PCI 总线的组成结构

理解第一章,从这张图开始看

HOST主桥

主要功能是隔离处理器系统的存储器域与处理器系 统的 PCI 总线域, 管理 PCI 总线域, 并完成处理器与 PCI 设备间的数据交换。PCI 设备通过 HOST 主桥访问主存储器时, 需要与处理器的 Cache 进行一致性操作, 因 此在设计 HOST 主桥时需要重点考虑 Cache 一致性操作。在一个处理器系统中, 每一个 HOST 主桥 都管理了一棵 PCI 总线树, 在同一棵 PCI 总线树上的所有 PCI 设备属于同一个 PCI 总线域。

PCI 总线

在一 棵 PCI 总线树中可能具有多条 PCI 总线, 而具有血缘关系的 PCI 总线组成一棵 PCI 总线树。

PCI 设备

PCI 主设备、 PCI 从设备和桥设备。

其中 PCI 从设备只能被 动地接收来自 HOST 主桥或者其他 PCI 设备的读写请求; 而 PCI 主设备可以通过总线仲裁获 得 PCI 总线的使用权, 主动地向其他 PCI 设备或者主存储器发起存储器读写请求。 而桥设备 的主要作用是管理下游的 PCI 总线, 并转发上下游总线之间的总线事务。

HOST处理器

PCI 总线规定在同一时刻内, 在一棵 PCI 总线树上有且只有一个 HOST 处理器。 这个 HOST 处理器可以通过 HOST 主桥, 发起 PCI 总线的配置请求总线事务, 并对 PCI 总线上的 设备和桥片进行配置。

在 PCI 总线中, HOST 处理器是一个较为模糊的概念。 在 SMP ( symmetric multiprocess⁃ ing) 处理器系统中, 所有 CPU 都可以通过 HOST 主桥访问其下的 PCI 总线树, 这些 CPU 都 可以作为 HOST 处理器。 但是值得注意的是, PCI 总线树的实际管理者是 HOST 主桥, 而不是 HOST 处理器。

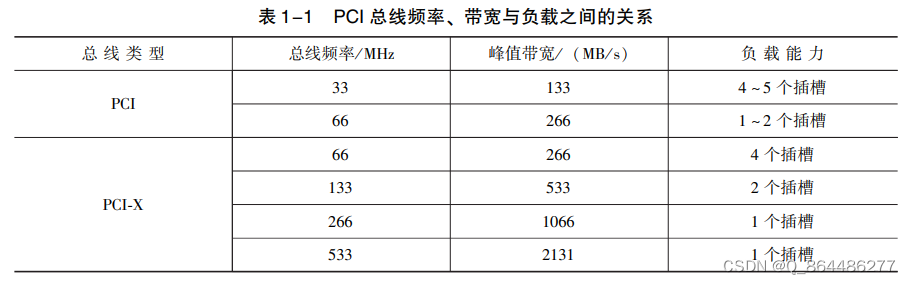

PCI总线负载

线频率越高, 能挂接的负载越少。

1.2 PCI总线的信号定义

PCI 总线是一条共享总线, 在一条 PCI 总线上可以挂接多个 PCI 设备。 这些 PCI 设备通 过一系列信号与 PCI 总线相连, 这些信号由地址/ 数据信号、 控制信号、 仲裁信号、 中断信 号等多种信号组成。

PCI 总线可以使用33 MHz 或者66 MHz 的时钟频率, 而 PCI⁃X 总线可以使用 133 MHz、 266 MHz 或者 533 MHz 的时钟频率。

除了 RST#、 INTA ~ D#、 PME#和 CLKRUN#等信号之外, PCI 设备使用的绝大多数信号 都使用这个 CLK 信号进行同步。 其中 RST#是复位信号, 而 PCI 设备使用 INTA ~ D#信号进 行中断请求。 本书并不详细介绍 PME#和 CLKRUN#信号。

1.2.1 地址和数据信号

(1) AD[31∶0]信号

PCI 总线复用地址与数据信号。第一个时钟传送地址,后面传数据,支持突发传送

(2) PAR 信号

PAR 信号是 AD[31∶ 0]和 C / BE[3∶ 0]的奇偶校验信号。

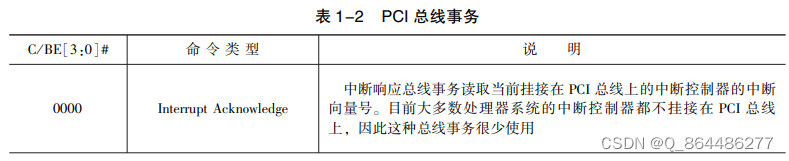

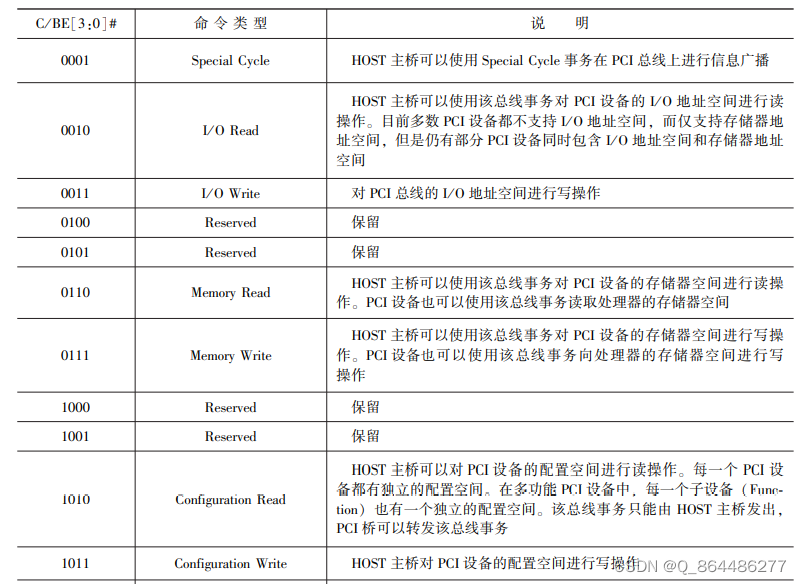

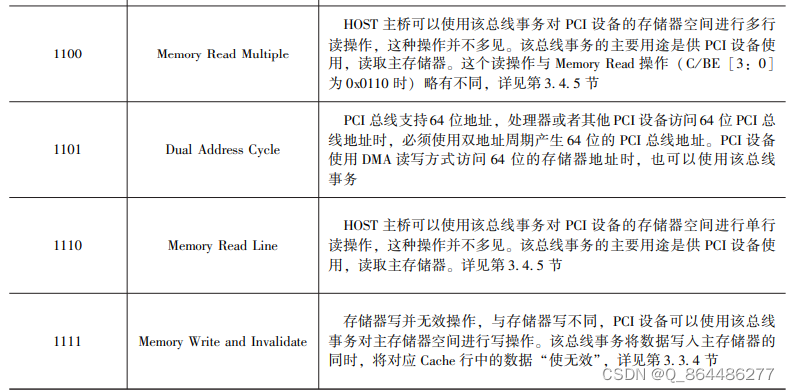

(3) C / BE[3∶0] #信号

1.2.2 接口控制信号

(1) FRAME#信号

该信号指示一个 PCI 总线事务的开始与结束。低电平有效,高电平无效。

(2) IRDY#信号

如果当前 PCI 总线事务为写事务, 表示数据已经在 AD[31∶ 0]上有效; 如果为读事 务, 表示 PCI 目标设备已经准备好接收缓冲, 目标设备可以将数据发送到 AD[31∶ 0]上。

(3) TRDY#信号

如果当前 PCI 总线事务为写事务, 表示目标设备已经准备好接收缓冲, 可以将 AD[31∶ 0]上的数据写 入目标设备; 如果为读事务, 表示 PCI 设备需要的数据已经在 AD[31∶ 0]上有效。

(4) STOP#信号

该信号有效时表示目标设备请求主设备停止当前 PCI 总线事务。

(5) IDSEL 信号

PCI 总线在进行配置读写总线事务时, 使用该信号选择 PCI 目标设备。

(6) DEVSEL#信号

该信号有效时表示 PCI 总线的目标设备准备好, 该信号与 TRDY#信号的不同之处在于 该信号有效仅表示目标设备已经完成了地址译码。 目标设备使用该信号通知 PCI 主设备, 其 访问对象在当前 PCI 总线上, 但是并不表示目标设备可以与主设备进行数据交换。 而 TRDY# 信号表示数据有效, PCI 主设备可以向目标设备写入或者从目标设备读取数据。 11 PCI 总线规范根据设备的译码速度, 将 PCI 设备分为快速、 中速和慢速三种。 在 PCI 总 线上还有一种特殊的设备, 即负向译码设备, 在一条 PCI 总线上当快速、 中速和慢速三种设 备都不能响应 PCI 总线事务的地址时, 负向译码设备将被动地接收这个 PCI 总线事务。 如果 在 PCI 主设备访问的 PCI 总线上, 没有任何设备可以置 DEVSEL#信号为有效, 主设备将使 用 Master Abort 周期结束当前总线事务。

(7) LOCK#信号

PCI 主设备可以使用该信号, 将目标设备的某个存储器或者 I / O 资源锁定, 以禁止其他 PCI 主设备访问此资源, 直到锁定这个资源的主设备将其释放。PCI 总线使用 LOCK#信号实 现 LOCK 总线事务, 只有 HOST 主桥、 PCI 桥或者其他桥片可以使用 LOCK#信号。

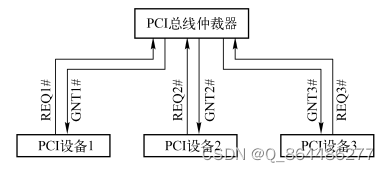

1.2.3 仲裁信号

在一棵 PCI 总线树中, 每一条 PCI 总线上都有一个总线仲裁器。 一个处理器系统可以使 用 PCI 桥扩展出一条新的 PCI 总线, 这条新的 PCI 总线也需要一个总线仲裁器, 通常在 PCI 桥中集成了这个总线仲裁器。 多数 HOST 主桥也集成了一个 PCI 总线仲裁器, 但是 PCI 总线 也可以使用独立的 PCI 总线仲裁器。 PCI 主设备使用 PCI 总线进行数据传递时, 需要首先置 REQ#信号有效, 向 PCI 总线仲裁 器发出总线申请, 当 PCI 总线仲裁器允许 PCI 主设备获得 PCI 总线的使用权后, 将置 GNT#信 号为有效, 并将其发送给指定的 PCI 主设备。 而 PCI 主设备在获得总线使用权之后, 将可以置 FRAME#信号有效, 与 PCI 从设备进行数据通信。

1.2.4 中断请求等其他信号

PCI 总线提供了 INTA#、 INTB#、 INTC#和 INTD#四个中断请求信号。信号置低表示向处理器请求中断,处理器执行完毕后,将中断信号置高。

PCI 总线规定单功能设备只能使用 INTA#信号, 而多功能设备才能使用 INTB# / C# / D# 信号。PCI 总线在进行数据传递过程时, 难免会出现各种各样的错误, 因此 PCI 总线提供了一 些错误信号, 如 PERR#和 SERR#信号。 其中当 PERR#信号有效时, 表示数据传送过程中出 现奇偶校验错( Special Cycle 周期除外) ; 而当 SERR#信号有效时, 表示当前处理器系统出 现了三种错误可能, 分别为地址奇偶校验错、 在 Special Cycle 周期中出现数据奇偶校验错、 系统出现其他严重错误。如果 PCI 总线支持 64 位模式, 还需要提供 AD[63∶ 32] 、 C / BE[7∶ 4] 、 REQ64、 ACK64 和 PAR64 这些信号。

1.3 PCI 总线的存储器读写总线事务

总线的基本任务是实现数据传送, 将一组数据从一个设备传送到另一个设备。PCI 总线支持以下几类存储器读写总线事务。

(1) HOST 处理器对 PCI 设备的 BAR 空间进行数据读写, BAR 空间可以使用存储器或 者 I / O 译码方式。 HOST 处理器使用 PCI 总线的存储器读写总线事务和 I / O 读写总线事务访 问 PCI 设备的 BAR 空间。 (2) PCI 设备之间的数据传递。 在 PCI 总线上的两个设备可以直接通信, 如一个 PCI 设 备可以访问另外一个设备的 BAR 空间。 不过这种数据传递在 PC 处理器系统中较少使用。 (3) PCI 设备对主存储器进行读写, 即 DMA 读写操作。 DMA 读写操作在所有处理器系 统中都较为常用, 也是 PCI 总线数据传送的重点。 在多数情况下, DMA 读写操作结束后将 伴随着中断的产生。 PCI 设备可以使用 INTA#、 INTB#、 INTC#和 INTD#信号提交中断请求, 也可以使用 MSI 机制提交中断请求。

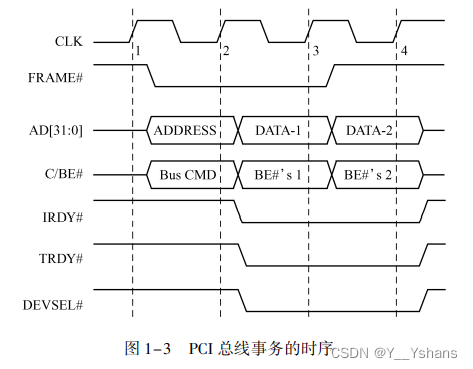

1.3.1 PCI 总线事务的时序

与 PCI 总线事务相关的控制信号有 FRAME#、 IRDY#、 TRDY#、 DEVSEL#等其他信号。

当PCI设备需要使用PCI总线的时候,先发送请求REQ#,通过仲裁,返回GNT#信号。PCI设备获得控制权后,FRAME#置为有效,总线事务结束后, FRAME#信号将被置为无效。PCI 主设备将访问的目的地址和总线命令分别驱动到 AD[31∶ 0]和 C / BE#信号上。 如果当前总线命令是配置读写, 那么 IDSEL 信号线也被置为有效。当 IRDY#、 TRDY#和 DEVSEL#信号都有效后, 总线事务将使用数据周期进行数据 传递。 当 IRDY#和 TRDY#信号没有同时有效时, PCI 总线不能进行数据传递, PCI 总线使用 这两个信号进行传送控制。

1.3.2 Posted 和 Non⁃Posted 传送方式

PCI 总线规定了两类数据传送方式, 分别是 Posted 和 Non⁃Posted 数据传送方式。

收集整理了一份《2024年最新物联网嵌入式全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升的朋友。

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

朋友。**

[外链图片转存中…(img-baSw23Xh-1715892968339)]

[外链图片转存中…(img-X2Rcqgr8-1715892968339)]

需要这些体系化资料的朋友,可以加我V获取:vip1024c (备注嵌入式)

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人

都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

4624

4624

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?