文章目录

-

- 一、实验目的

-

二、实验内容

-

三、实验设计

-

四、实验结果及仿真

熟悉元件封装方法,掌握层次化电路设计方法;掌握VHDL例化语句的设计方法。

1.用VHDL语言设计1位全加器,其中仅就半加器实体进行例化声明及端口映射语句,或运算直接调用运算函数。通过编译、仿真验证功能正确性。

2.就实验过程及结果进行简要描述和分析,并思考与用原理图方法设计的各自特点。

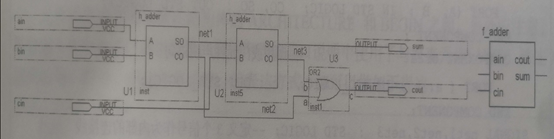

全加器可以由两个半加器和一个或门连接而成,其经典的电路结构如下图所示。图的右侧是全加器的实体模块,它显示了全加器的端口情况。设计全加器之前,需要先设计好半加器。

整个设计过程和表述方式都可以用VHDL来描述。首先设计出半加器。半加器实现的VHDL描述如下所示。

Library Ieee;

Use Ieee.Std_Logic_1164.All;

Entity h_adder is

port (a,b : in Std_Logic; co,so : out Std_Logic);

End Entity h_adder;

Architecture Bhv of h_adder is

Begin

so <= a xor b; --半加器核心逻辑功能的实现

co <= a and b; --半加器核心逻辑功能的实现

End Architecture Bhv;

(而至于或门,则不需要单独用VHDL来描述,直接调用即可。)

然后根据上面的电路图用VHDL语句将两个元件连接起来,构成了全加器的VHDL顶层描述。程序如下图。

Library Ieee; --全加器顶层设计描述

Use Ieee.Std_Logic_1164.All;

Entity f_adder is

Port (ain,bin,cin : in Std_Logic;

sum,cout : out Std_Logic);

End Entity f_adder;

Architecture Bhv of f_adder is

component h_adder --调用半加器声明

port (a,b : in Std_Logic; co,so : out Std_Logic);

End component h_adder;

signal so1,co1,co2 : Std_Logic; --定义三个信号变量作为内部的连接线

begin

u1: h_adder Port Map (a=>ain,b=>bin,so=>so1,co=>co1); --例化语句

u2: h_adder Port Map (a=>so1,b=>cin,so=>sum,co=>co2);

cout <= co1 or co2;

End Architecture Bhv;

在实体中首先定义了全加器顶层设计的端口信号,然后在Architecture和Begin之间加入了调用元件的声明语句,即利用Component语句对准备调用的元件做了声明,并定义so1,co1,co2三个信号作为全加器内部的连接线。最后利用端口映射语句Port Map()将两个半加器模块和一个或门模块连接起来构成一个完整的全加器。

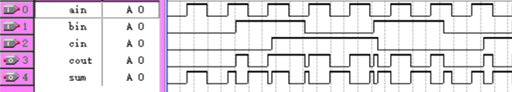

分别给ain、bin和cin合适周期的方波信号输入,观察count和sum输出信号。如下图所示。

观察输入与输出的可以分析出“1为全加器”的功能已经实现。即实现如下功能:

五、实验思考与总结

元件例化语句分为元件声明和元件例化两部分。用元件例化方式设计电路的方法是: (1)完成各种元件的设计。(2)元件声明。(3)通过元件例化语句调用这些元件。元件例化是可以多层次的。一个调用了较低层次元件的顶层设计实体本身也可以被更高层次设计实体所调用,成为该设计实体中的一个元件。

用原理图设计较VHDL更为直观明了,可以通过电路图清楚其逻辑关系和实现的功能关系。而用VHDL语言设计则较为简便,只需清楚各个接口之间的关系和调用的原则。

最后

小编这些年深知大多数初中级工程师,想要提升自己,往往是自己摸索成长,自己不成体系的自学效果低效漫长且无助。

因此我收集整理了一份《2024年Java全套学习资料》,初衷也很简单,就是希望能够帮助到想自学提升又不知道该从何学起的朋友,同时减轻大家的负担。

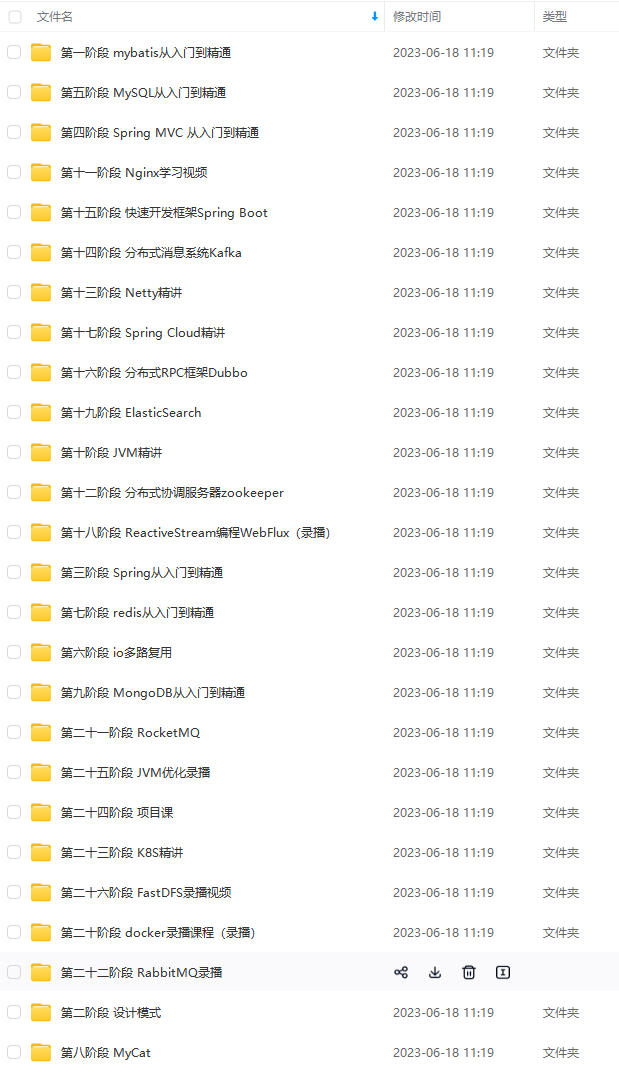

由于文件比较大,这里只是将部分目录截图出来,每个节点里面都包含大厂面经、学习笔记、源码讲义、实战项目、讲解视频,并且会持续更新!

如果你需要这些资料,⬅专栏获取

WLD4G11-1719507685788)]

[外链图片转存中…(img-T4dizW5n-1719507685789)]

由于文件比较大,这里只是将部分目录截图出来,每个节点里面都包含大厂面经、学习笔记、源码讲义、实战项目、讲解视频,并且会持续更新!

如果你需要这些资料,⬅专栏获取

676

676

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?