FPGA——1位全加器和4位全加器的实现

一、认识全加器

1、半加器

1.半加器的定义

半加器是能够对两个一位的二进制数进行相加得到半加和以及半加进位的组合电路。

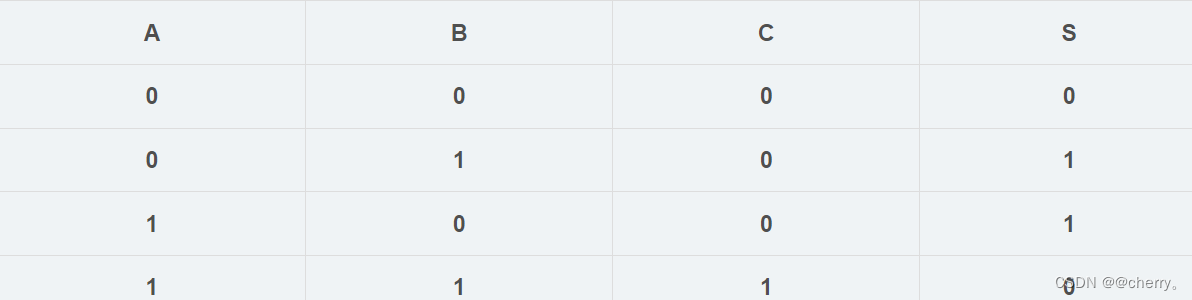

2.半加器的真值表

A,B表示二进制数,C表示半加进位,S表示半加和

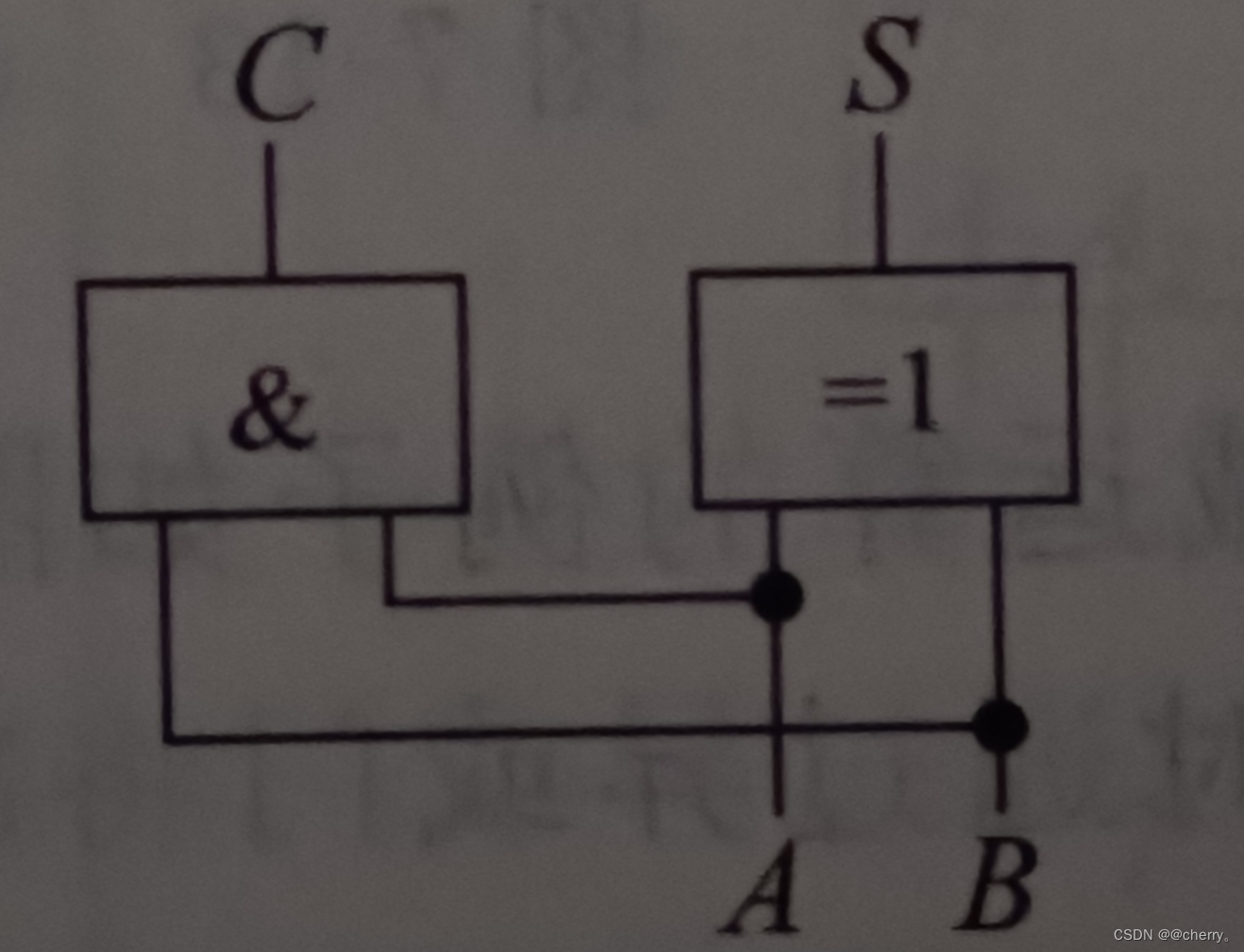

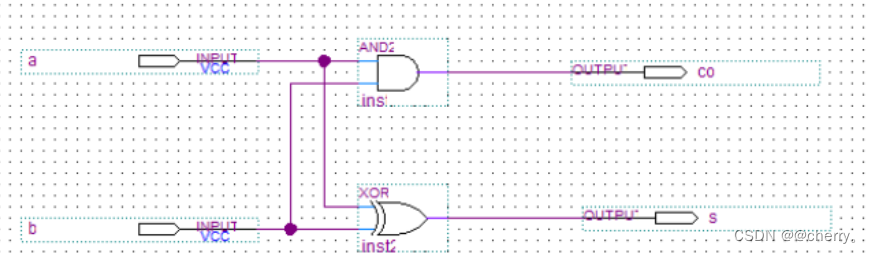

3.逻辑电路图

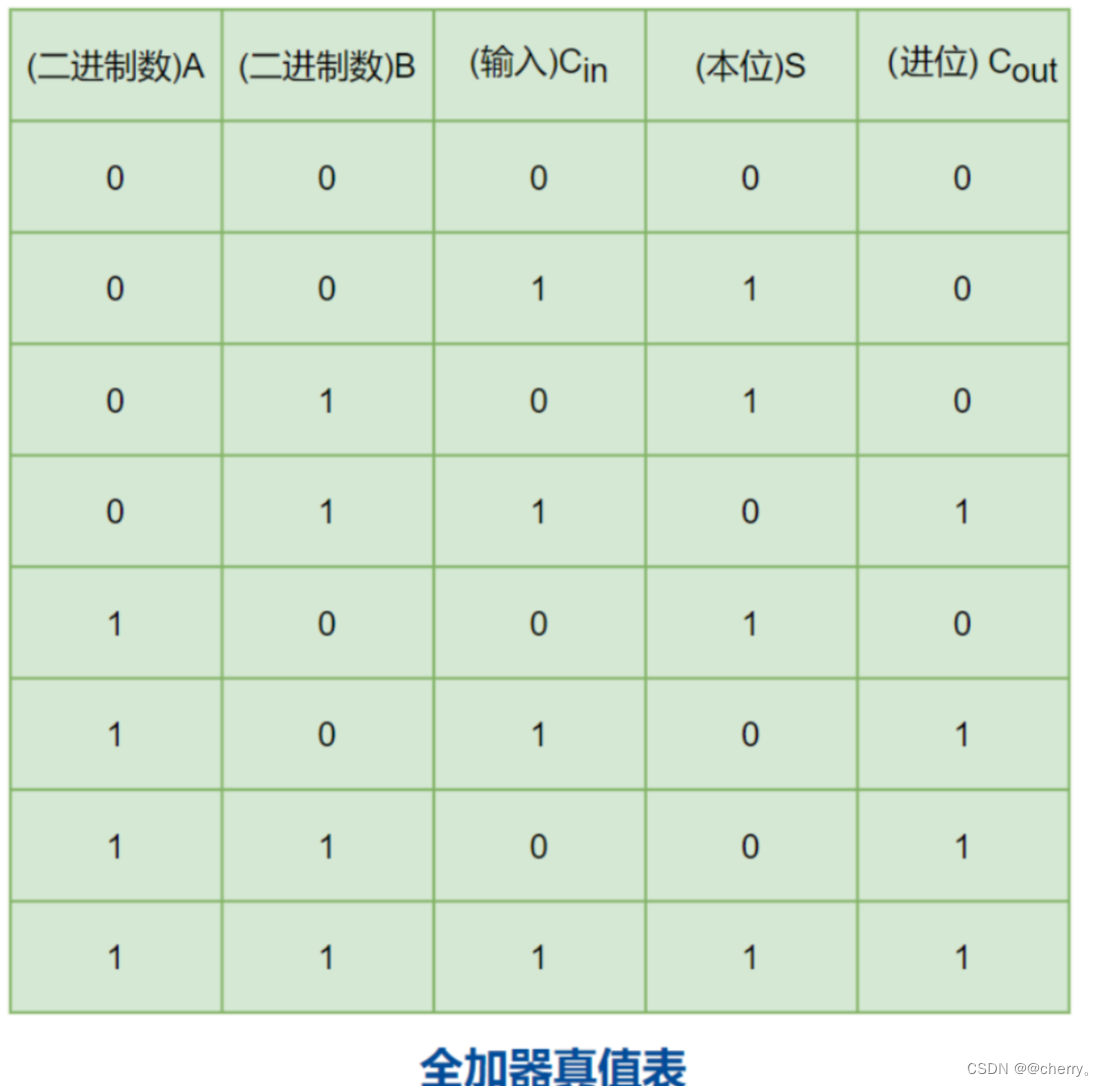

2、 全加器

二、输入原理图实现1位加法器

1、工程创建

因为之前写过了,参考以下创建工程

链接: link

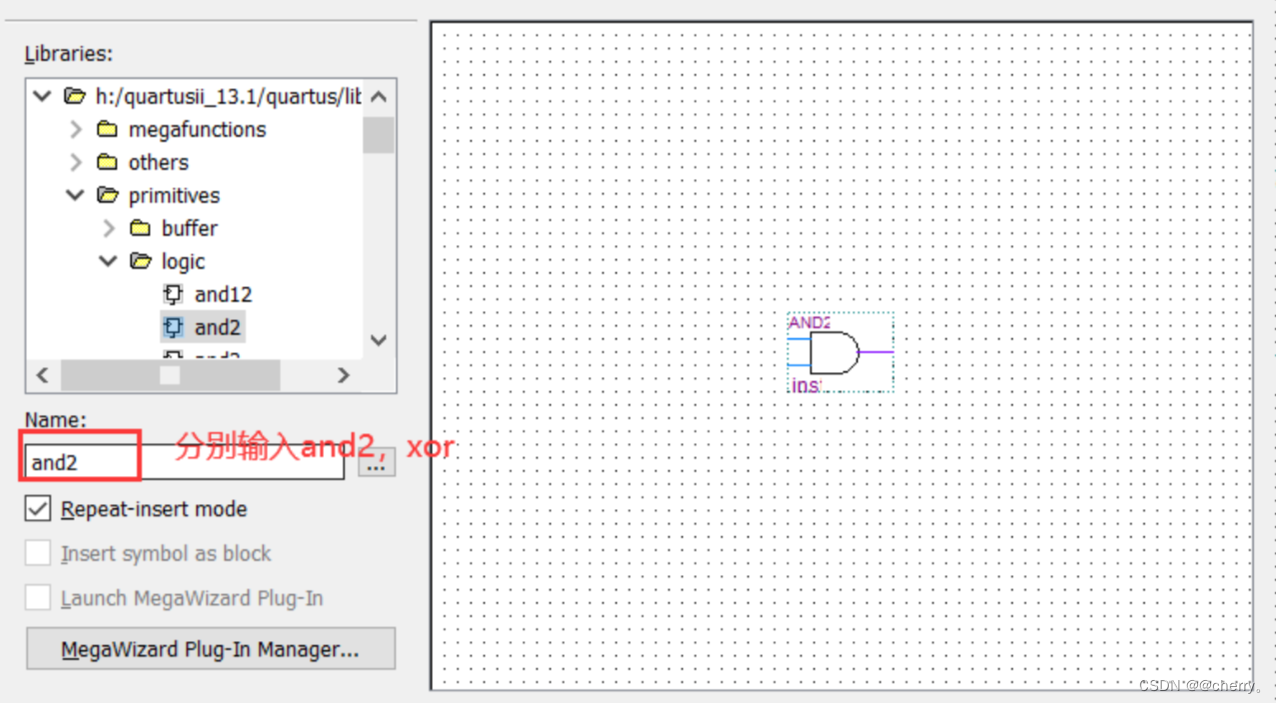

2、半加器原理图输入

1、分别调入元件and2, xor,然后设计原理图如下:

2、保存文件,并编译

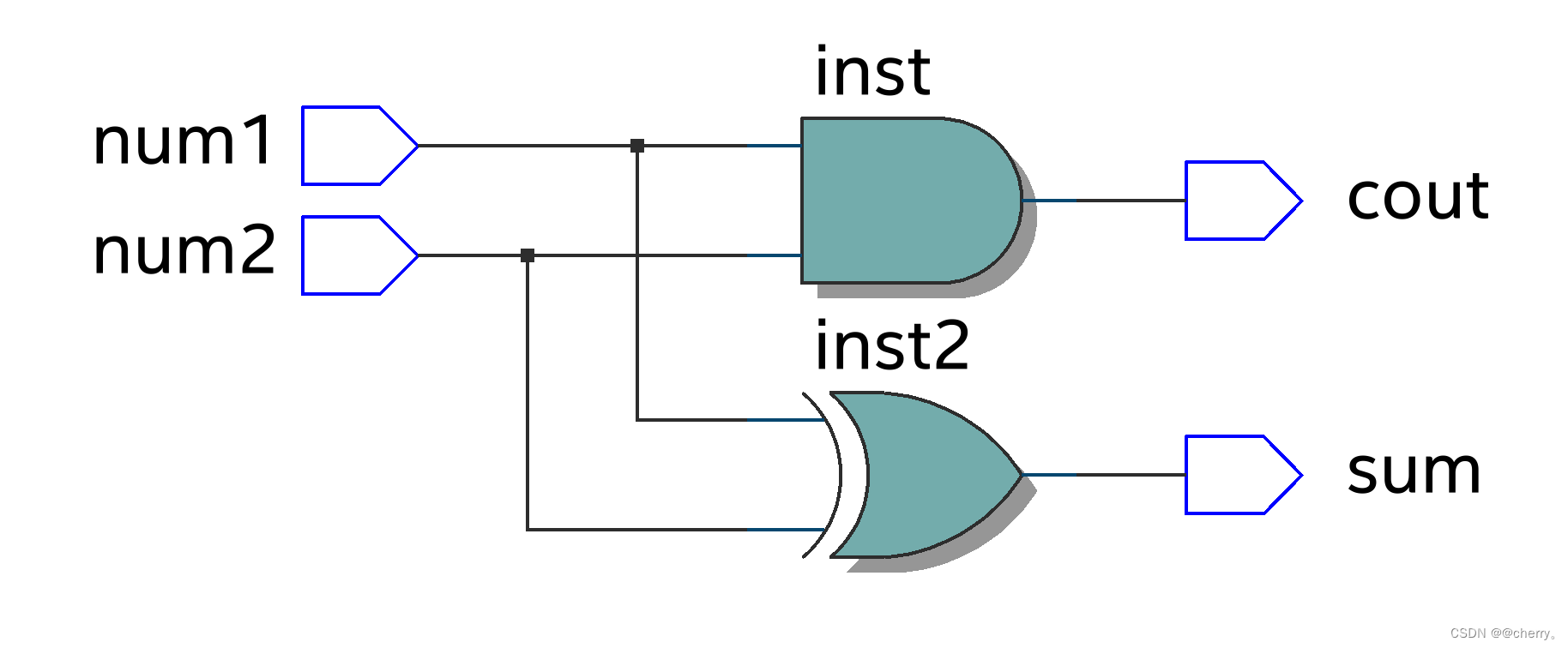

通过tool->Netlist Viewers->RTL Viewer,查看电路图

保存该文件为:add.bdf,然后进行编译

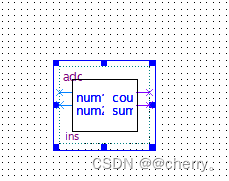

- 将设计项目设置成可调用的元件

为了构成全加器的项层设计,必预将以上设计的半加器half_adder.bdf 设置成可调用的元件。

选择菜中File中的Create/Update→Create Symbol Files for Current File项,即可将当前文件add变成一个元件符号存盘,以 待在高层次设计中调用。

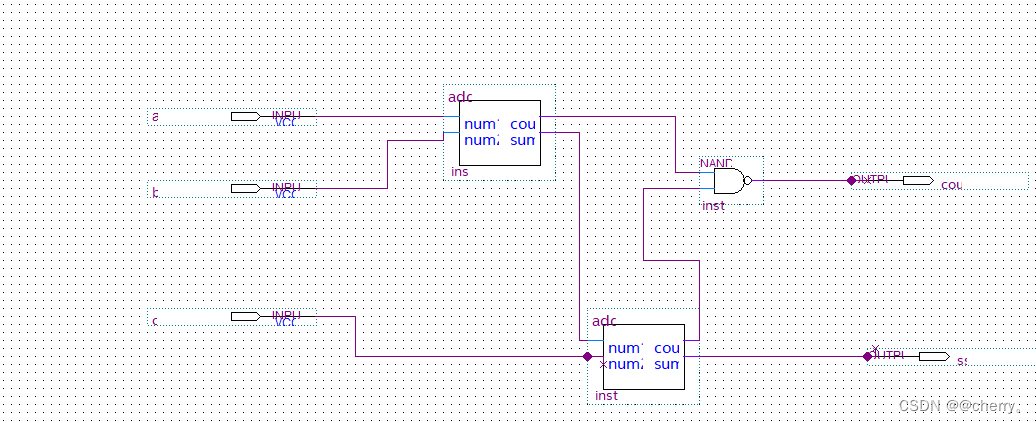

- 新家全加器原理图文件

新建方法同第二步新建半加器原理图文件方法一样

在弹出的“symbol”窗的“name”栏输入底层文件半加器的存储名“add” 调出半加器

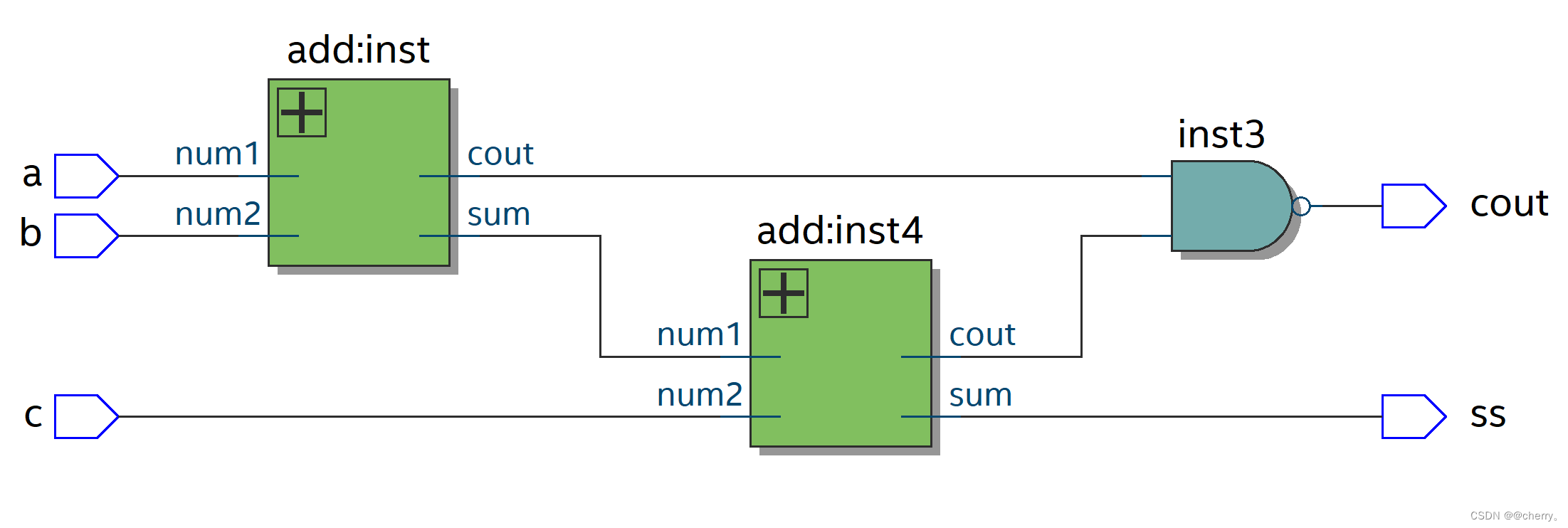

5、然后设计原理图如下:

3、实验效果

引脚绑定及硬件下载测试

① 选择目标芯片:cycloneIVE系列的EP4CE11529C7 ,在菜单中选择,“assignments→device…”(同新建工程所选择的型号一样)

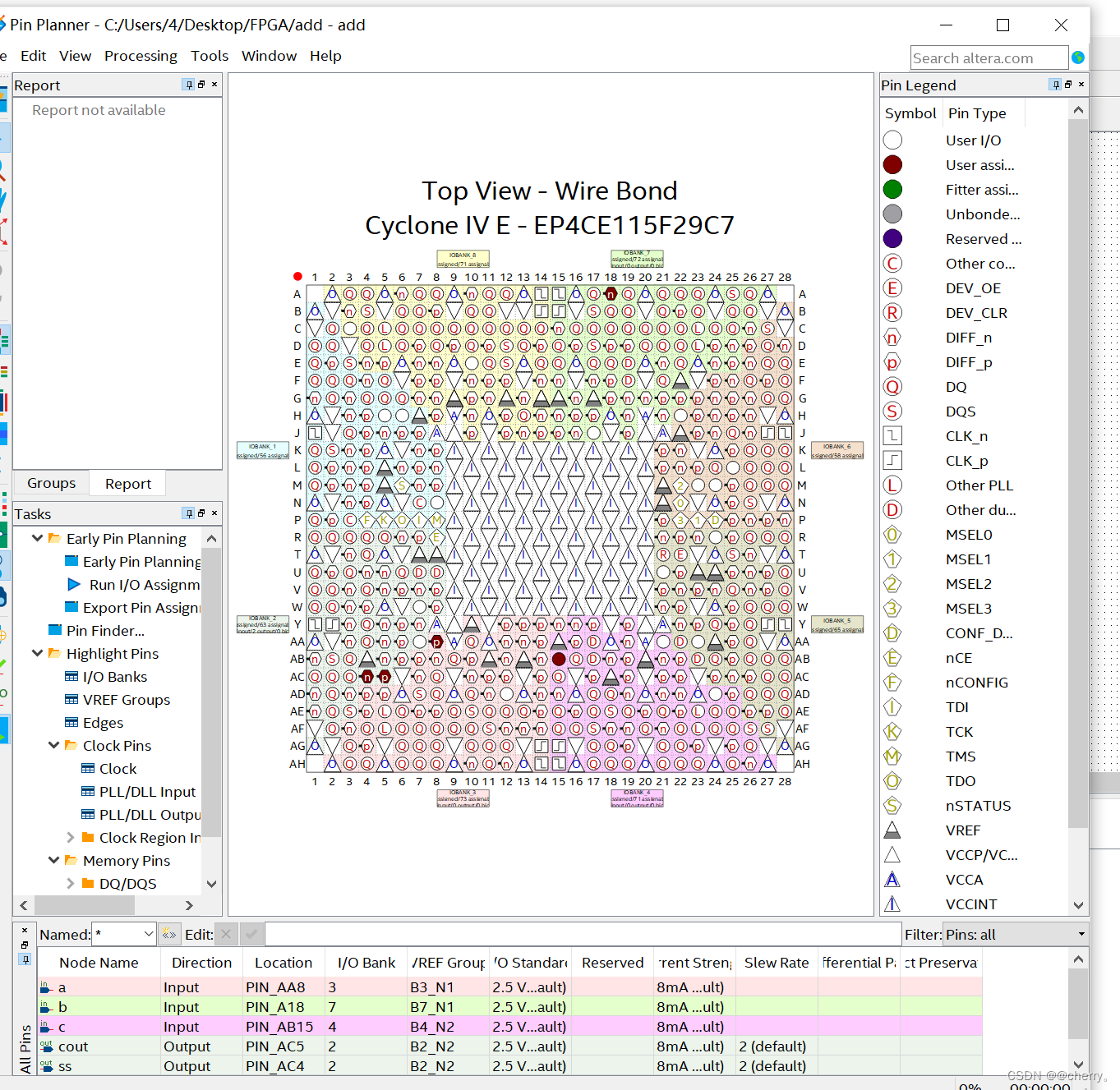

② 引脚绑定

先从菜单中选择“assignments→pin planner”,然后进行如下配置:

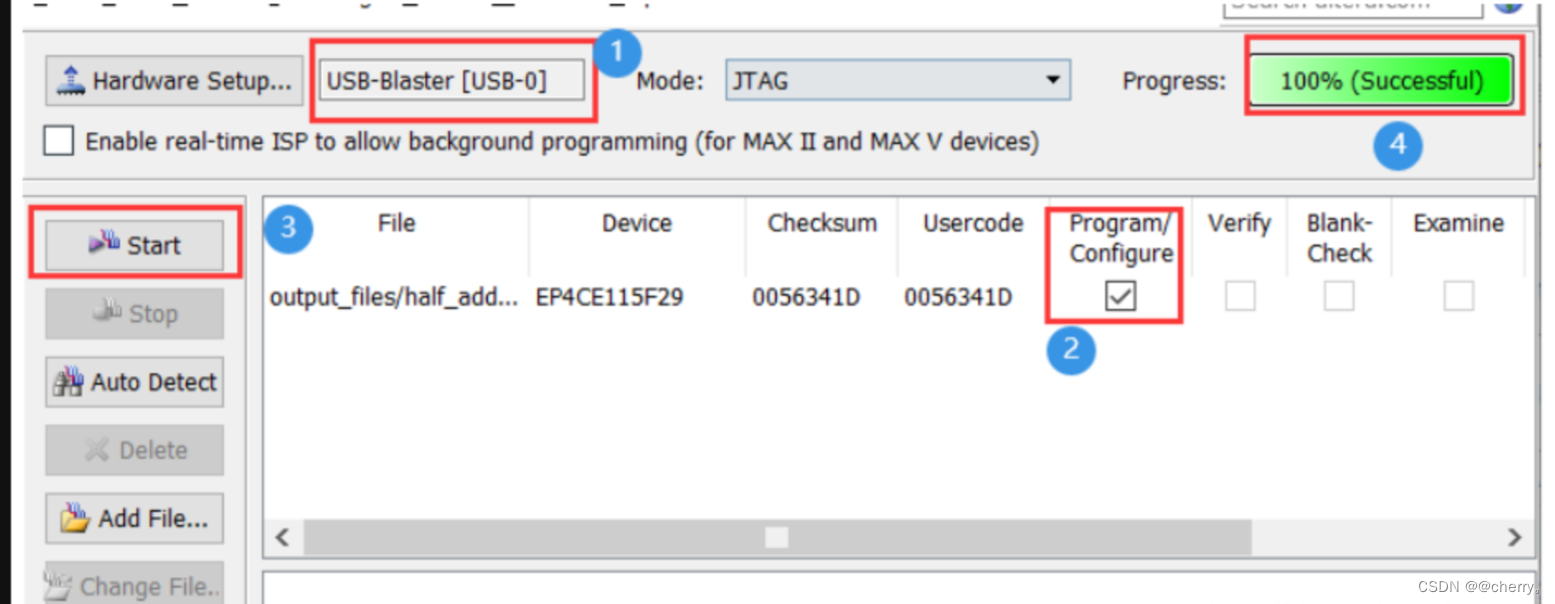

③ 把开发板接上电源,USB 接口接电脑, 然后点击Programmer按钮,然后弹出一个下载界面。

如果第一次下载需安装 硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USB blaster”,再点击“ok”,则硬件被安装上。

如果找不到,请先在电脑设备管理器中配置USB-Blaster驱动

4、实验结果

三、Verilog实现1位全加器

1. 新建工程

工程名字为add_1bit,芯片型号选择同上

2. 新建一个Verilog文件

File -----> New -----> Verilog HDL File

module add_1bit(S,C_out,A,B,C_in);

input A,B,C_in ;

output S,C_out ;

reg S,C_out ;

always @(A or B or C_in)

begin

{C_out,S} = A +B +C_in ;

end

endmodule

从抽象层次来说,这并不是用数电的设计方法来实现的,但是这不影响我们通过这个来实现一位全加器。

该Verilog文件名为 add_1bit.v

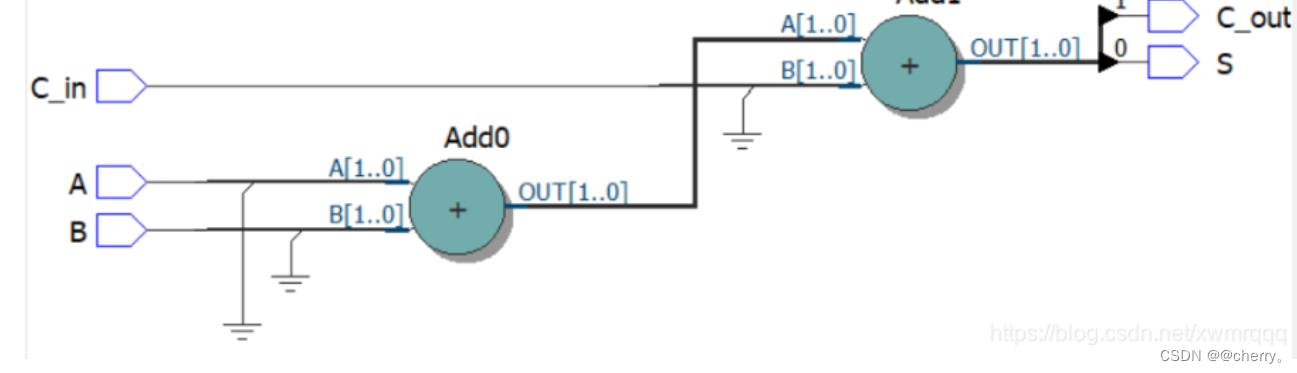

编译之后,查看其硬件电路图如下:

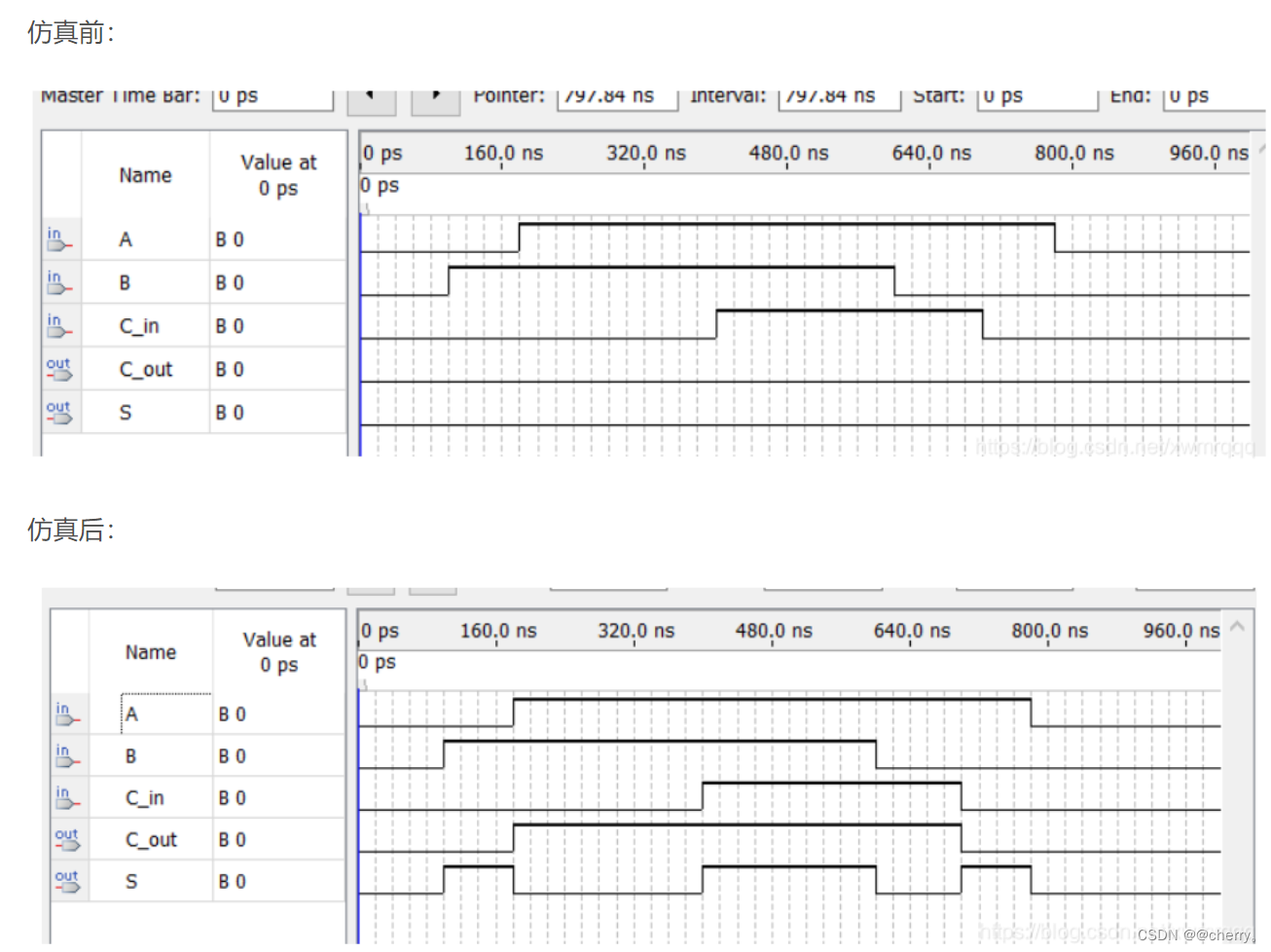

3、仿真

其他

引脚的绑定,烧入结果如上

四、位全加器的实现

1、工程

module four (

num1,

num2,

cin,

cout,

sum

);

input [3:0] num1;

input [3:0] num2;

input cin;

output cout;

output [3:0] sum;

reg cout;

reg [3:0] sum;

reg add;

always @(num1 or num2 or cin)

begin

// 第一位

sum[0] = (num1[0] ^ num2[0]) ^ cin;

cout = (num1[0] & num2[0]) | (num2[0] & cin) | (num1[0] & cin);

add = cout;

// 第二位

sum[1] = (num1[1] ^ num2[1]) ^ add;

cout = (num1[1] & num2[1]) | (num2[1] & add) | (num1[1] & add);

add = cout;

// 第三位

sum[2] = (num1[2] ^ num2[2]) ^ add;

cout = (num1[2] & num2[2]) | (num2[2] & add) | (num1[2] & add);

add = cout;

// 第四位

sum[3] = (num1[3] ^ num2[3]) ^ add;

cout = (num1[3] & num2[3]) | (num2[3] & add) | (num1[3] & add);

add = cout;

end

endmodule

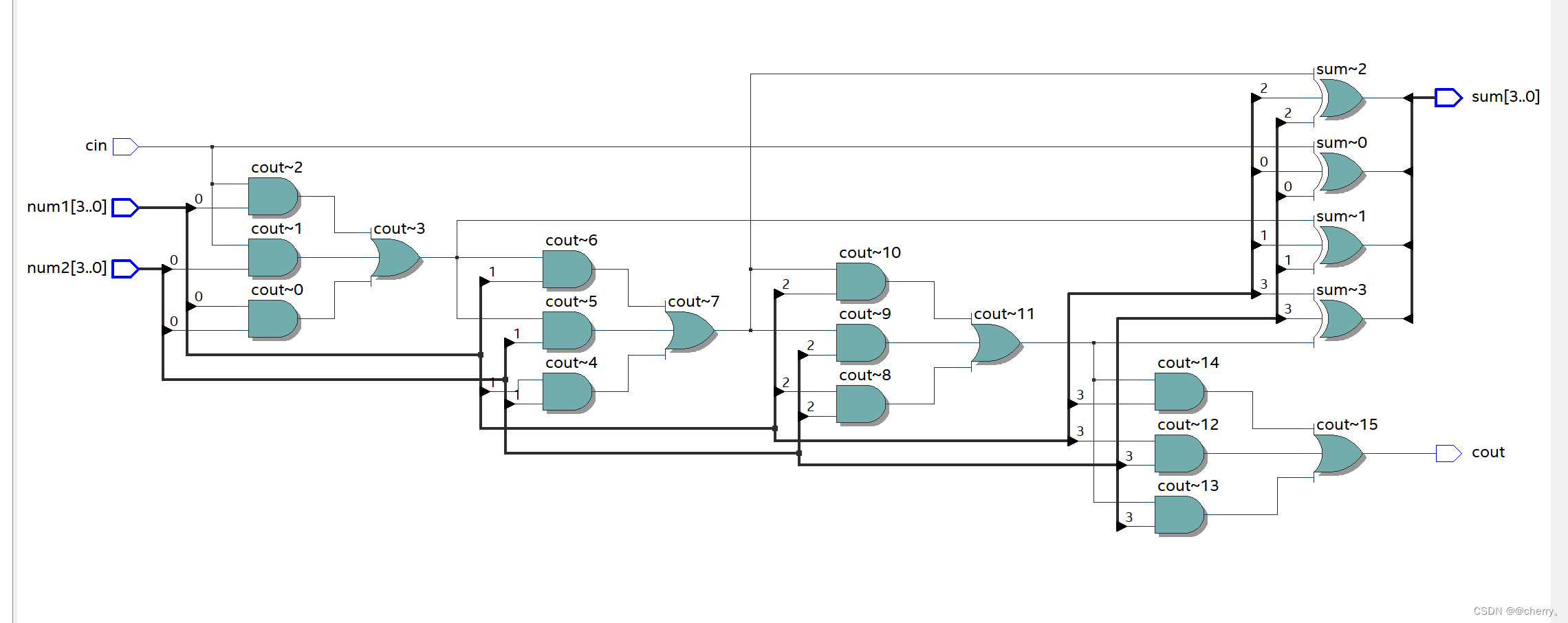

2、电路图

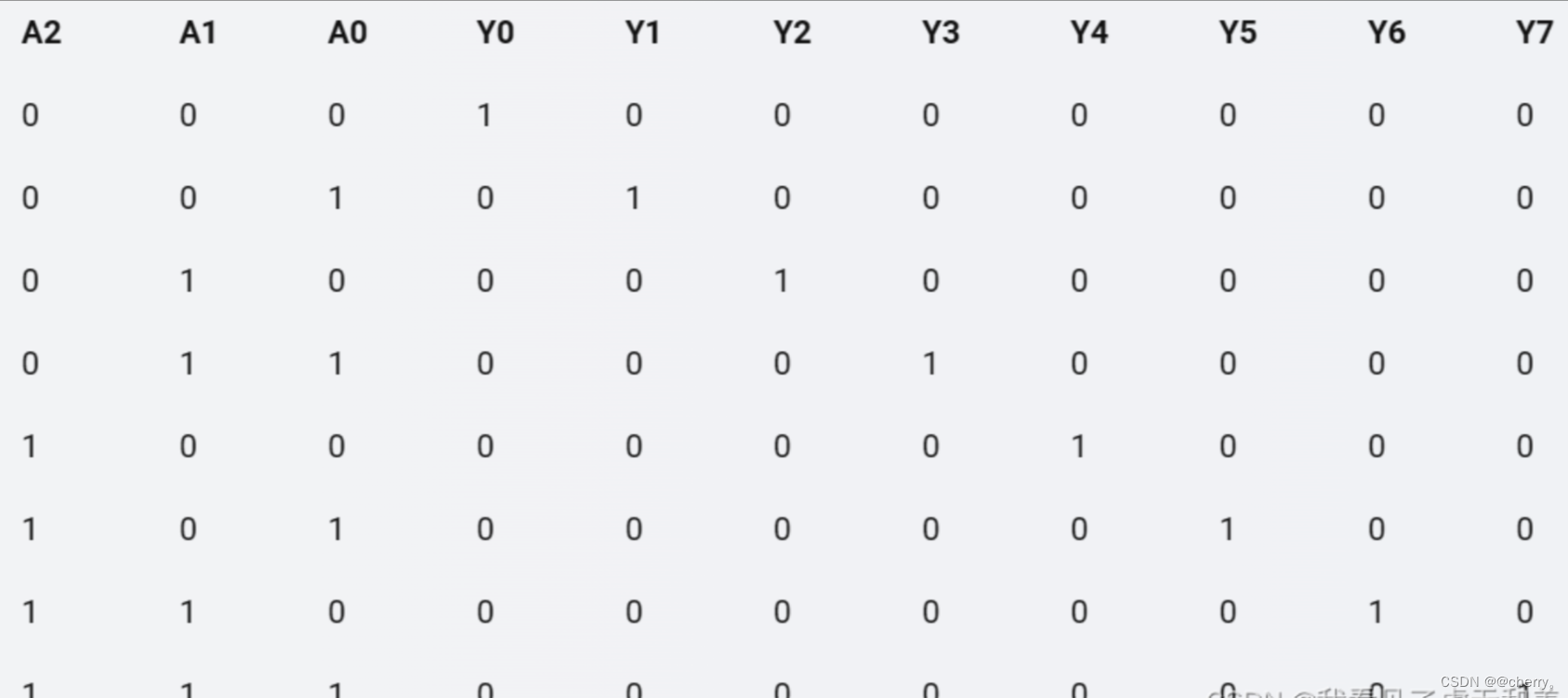

五、关于3-8译码器

真值表

六、参考

链接: link

3206

3206

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?