1.对74LS192芯片的简单介绍

74LS192是一款经典的同步十进制可逆计数器芯片,属于TTL(晶体管-晶体管逻辑)系列。它具有以下主要特点和功能:

主要特点

• 同步操作:所有触发器在同一时刻响应时钟脉冲的变化,确保数据的一致性和准确性。

• 双向计数能力:可以执行向上(增)或向下(减)的计数操作。

• 双时钟输入:具有两个时钟输入端,分别用于加计数(CPU)和减计数(CPD)。

• 清零与预置功能:提供异步清除端口(MR)以及并行加载输入端(PL),用于设置初始状态或强制回到特定数值。

• 级联能力:可以直接级联而无需外接电路,借位输出(BO)和进位输出(CO)可以用于级联递增计数和递减计数。

应用场景

• 数字计数:常用于需要进行数字计数的场合,如计时器、计数器等。

• 时序控制:用于控制时序电路,确保系统的同步性和稳定性。

引脚功能

• CPU:加计数时钟输入端。

• CPD:减计数时钟输入端。

• PL:并行加载输入端,低电平有效。

• MR:异步主复位(清除)输入。

• P0-P3:并行数据输入端。

• Q0-Q3:触发器输出端。

• TCU:终端计数上(进位)输出。

• TCD:终端计数下(借位)输出。

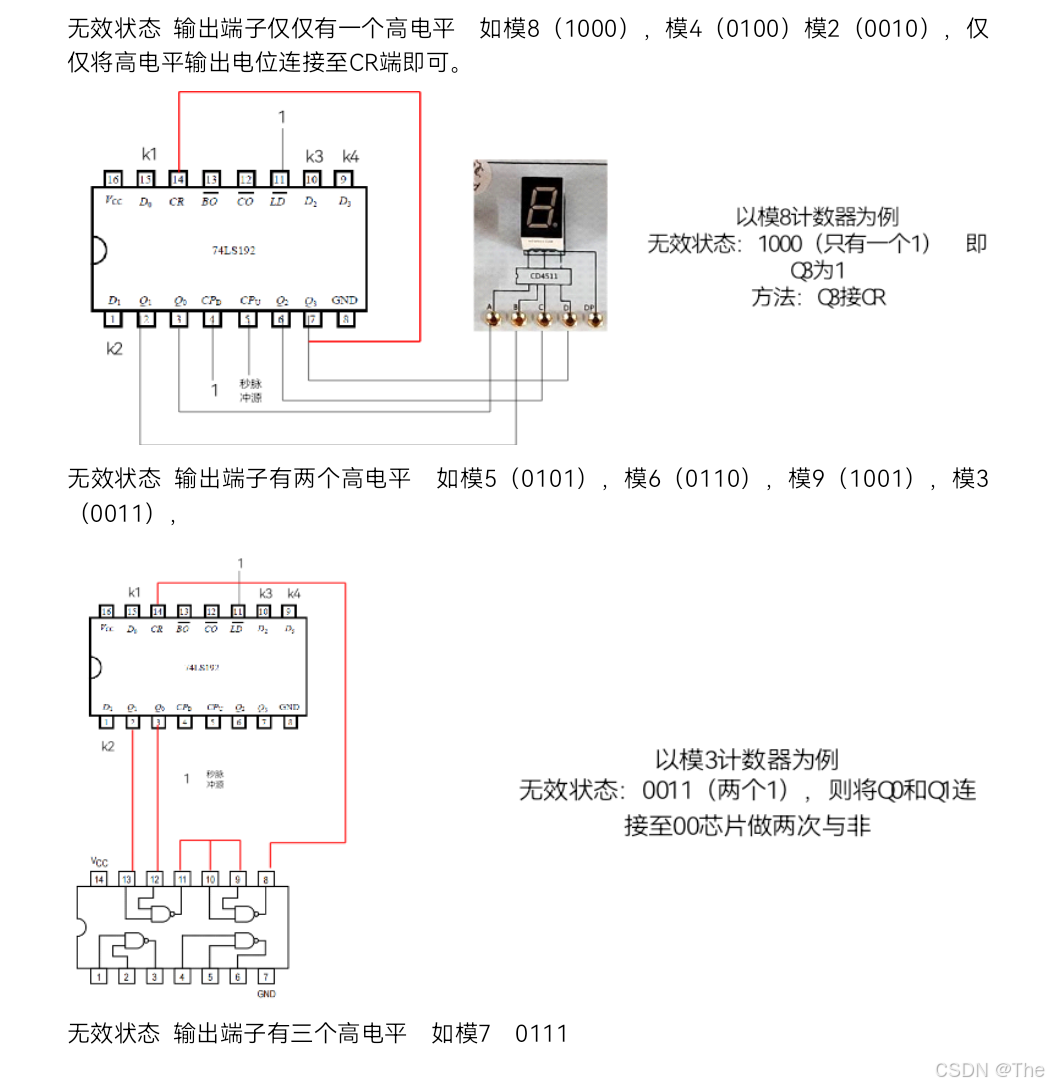

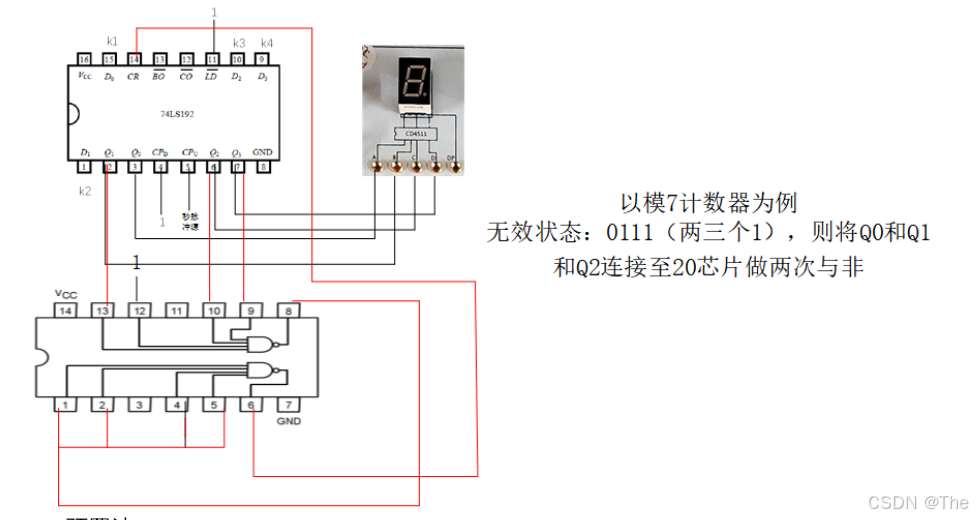

2.复位法(CR)

思路:利用输出和CR端对输出清零

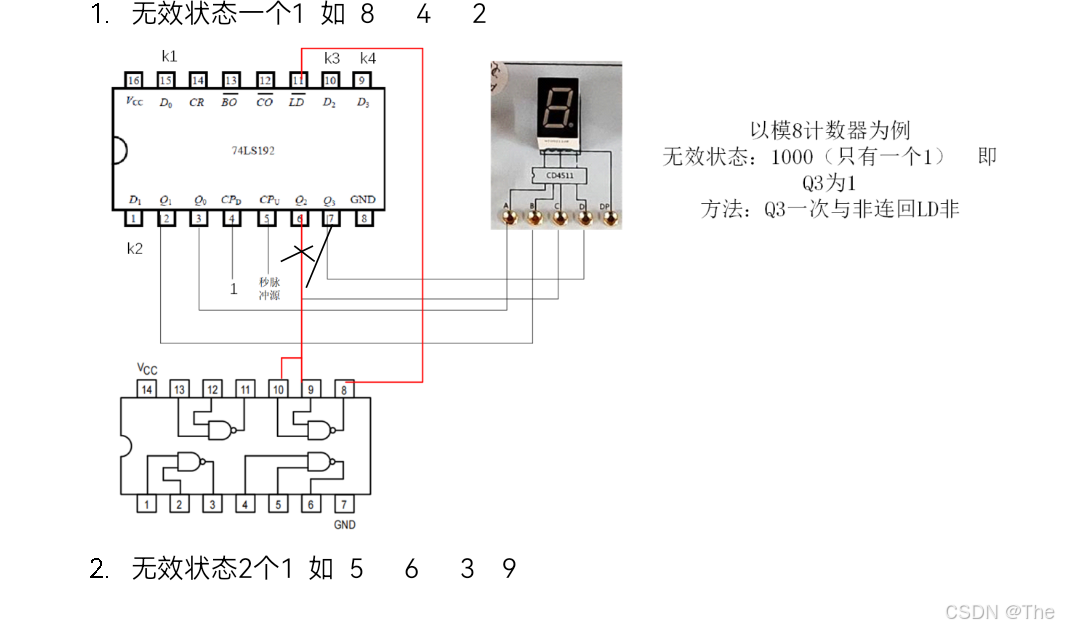

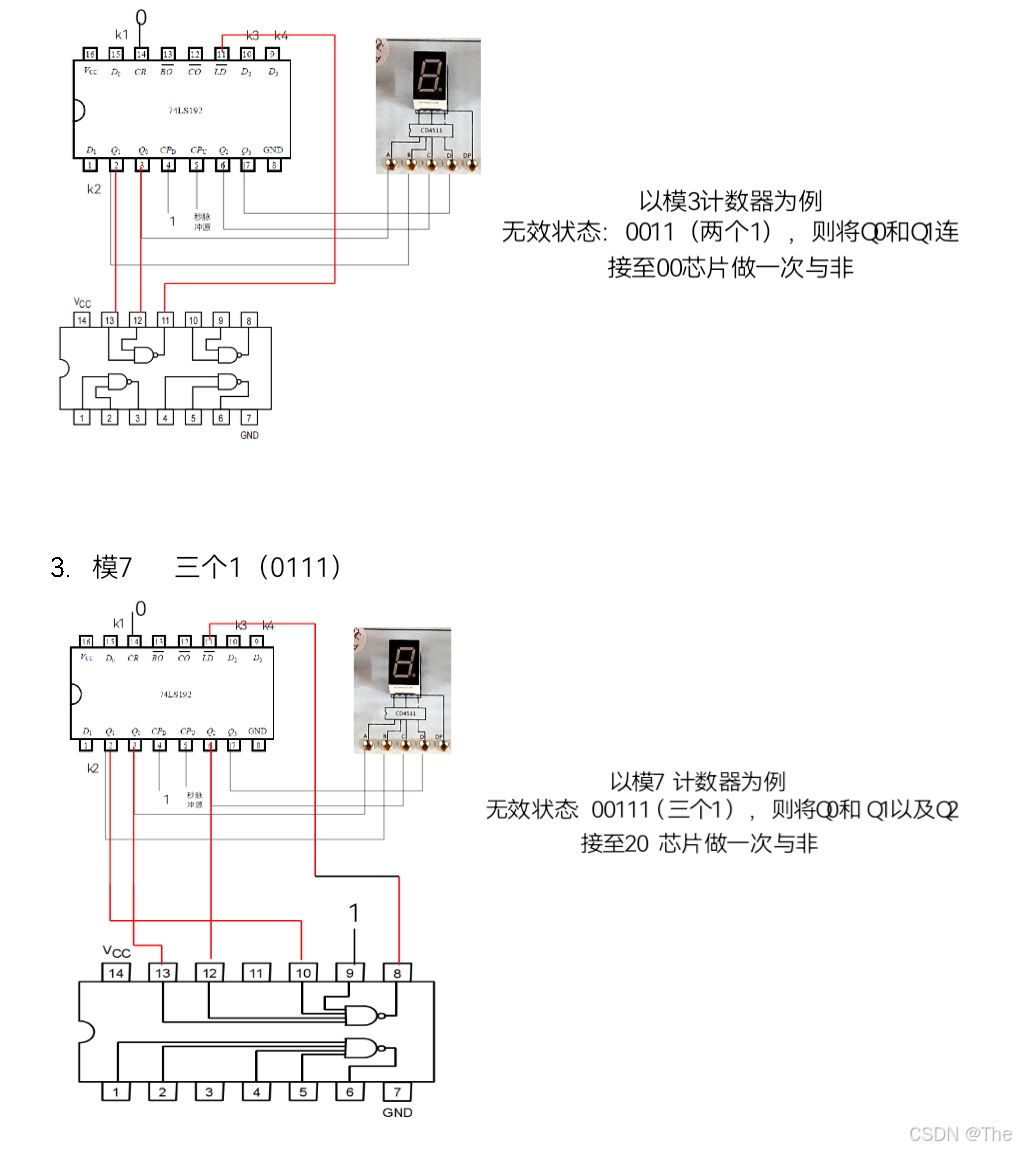

3.预置法(LD非)

思路:利用输出和LD非端对输出置0;此时D3D2D1D0均为0000

如有不足,欢迎补充!

9708

9708

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?