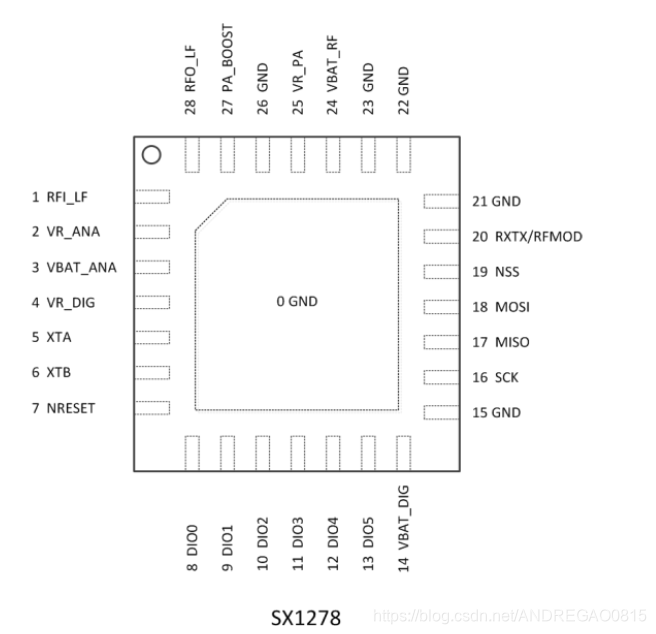

主要引脚说明

NRESET–复位触发输入

DIOx—数字IO,软件配置

GND—接地

SCK—SPI时钟输入

MISO—SPI数据输入

MOSI—SPI数据输出

NSS—SPI片选输入

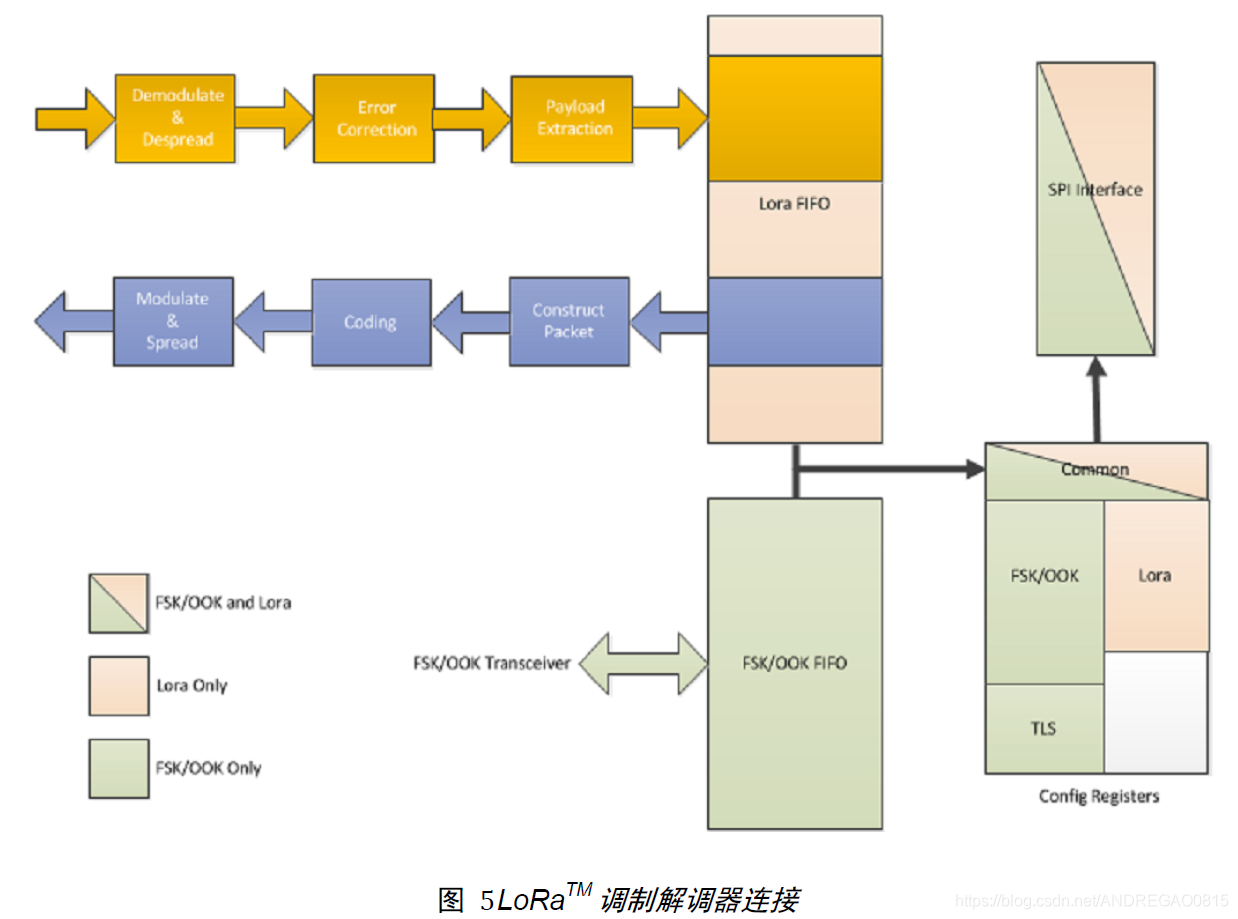

Lora调制解调器

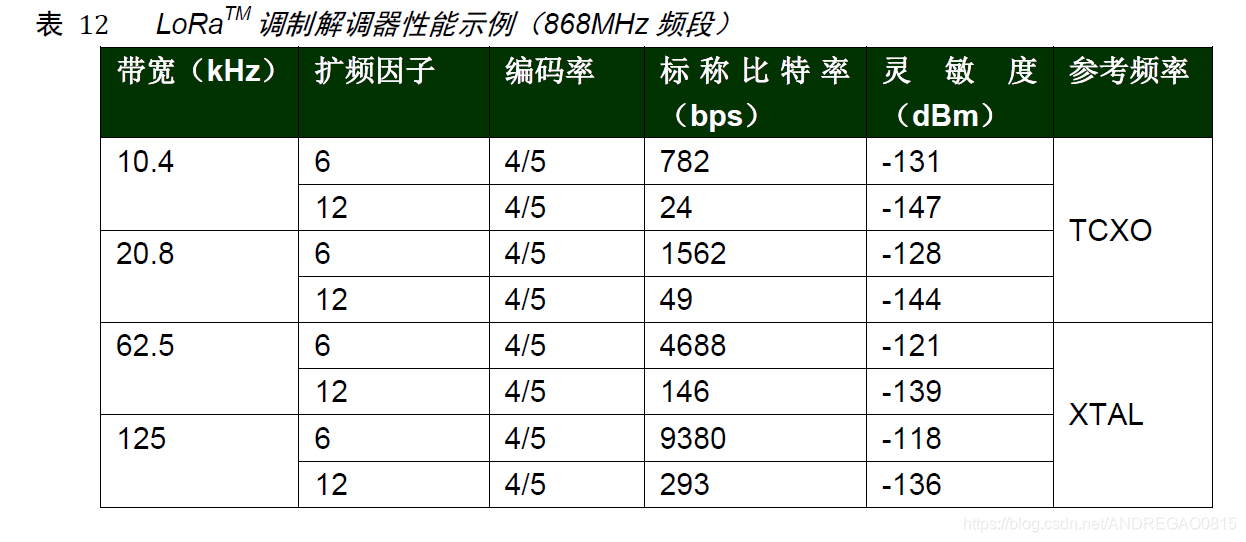

LoRa调制解调器采用扩频调制和前向纠错技术。与传统的FSK或OOK调制技术相比,这种技术不仅扩大了无线通讯链路的覆盖范围,而且还提高了链路的鲁棒性。下表列明了通过几种设置可以提高LoRa调制解调器性能的一些示例。设计师可以通过调整扩频因子和纠错率这两种设计变量,从而在带宽占用、数据速率、链路预算改善以及抗干扰性之间达到更好的平衡

Lora调制解调器的配置

只需要通过配置寄存器RegOpMode就能将FSK调制解调器切换成Lora调制解调器。

Lora调制解调器拥有独立的双端口数据缓冲FIFO,且在是所有操作模式下均可通过SPI接口访问该通道

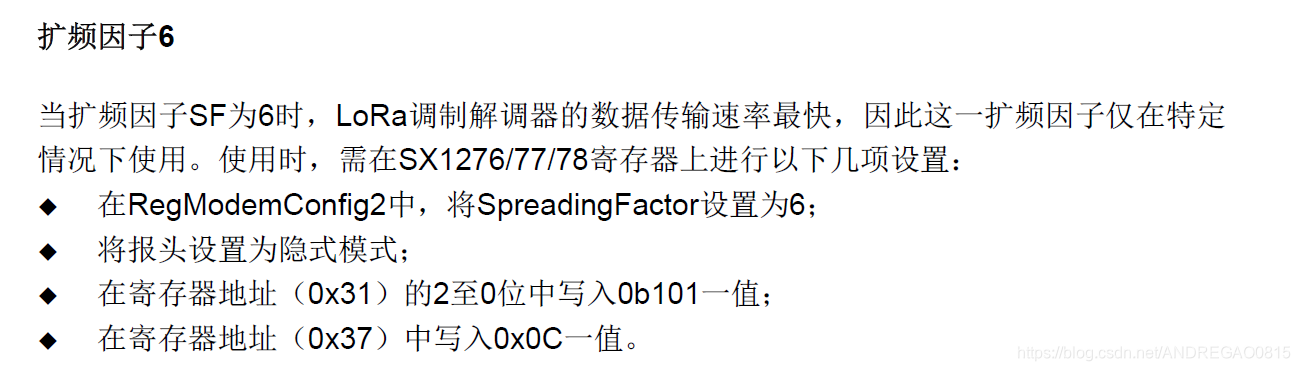

扩频因子

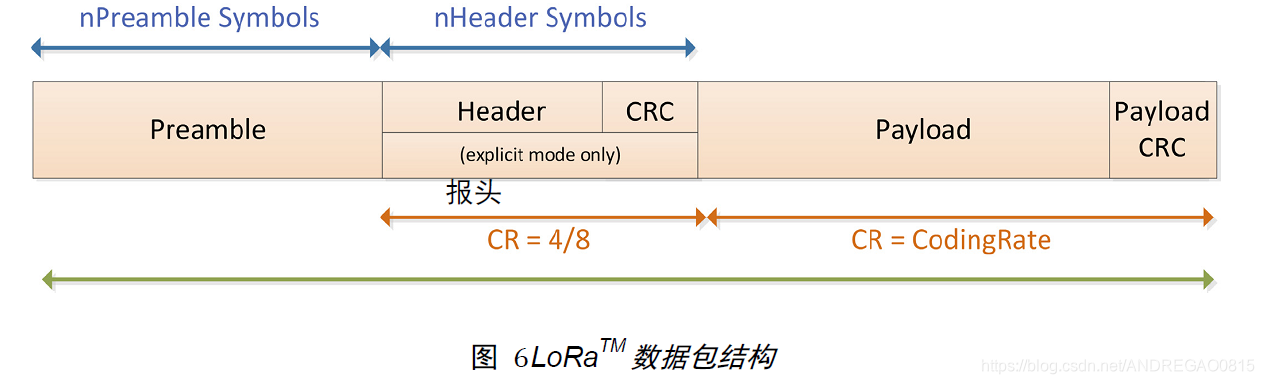

Lora数据包结构

LoRaTM调制解调器采用隐式和显式两种数据包格式。其中,显式数据包的报头较短,主要包含字节数、编码率及是否在数据包中使用循环冗余校验(CRC)等信息。

前导码:用于保持接收机与输入的数据流同步。在默认情况下,数据包含有12个符号长度的前导码。

报头:有显式报头和隐式报头。

显式—默认的操作模式,包括

·以字节数表示的有效负载长度

·向前纠错码率

·是否打开可选的16位负载CRC

隐式—特定情况下,有效负载长度,编码率以及CRC为固定或已知,比较有效的做法是通过调用隐藏式报头模式来缩短发送时间。(如果扩频因子为6,只能使用隐式报头模式)

有效负载:是一个长度不定的字段。

Lora数字接口

Lora调制解调器有三个数字接口,静态配置寄存器,状态寄存器以及一个FIFO数据缓存

Lora配置寄存器–通过SPI接口访问。寄存器在任何设备模式下均可读,但仅在睡眠和待机模式下可写。

Lora状态寄存器–在接收机运行过程中提供状态信息。

Lora FIFO数据缓存–只能通过SPI接口访问。除睡眠模式下,在其他操作模式下均可读。

原理:FIFO数据缓存拥有双端口配置,因此可以在缓存内同时存储将要发送和接收的信息。

RegFifoTxBaseAddr规定了将要发送数据的起始位置。

RegFifoRxBaseAddr规定了接收操作中写入缓存的起始位置。(默认情况下,器件上电后,以保证一半的可用内存用于Rx

RegFifoRxBaseAddr被初始化

至地址0x00),另外一半的可用内存用于Tx(RegFifoTxBaseAddr被初始化至地址0x80)

为充分利用FIFO数据缓存,可以将基地址RegFifoTxBaseAddr和RegFifoRxBaseAddr设置为0x00,从而使整个FIFO数据缓存仅在发送或接收模式下使用。

通过SPI接口读取或写入当前数据的FIFO数据缓存单元由地址指针RegFifoAddrPtr定义。

寄存器RegRxNbBytes会定义待写入数据的所占缓存单元的大小。

寄存器RegPayloadLength则显示待发送数据所占用的缓存单元大小。(在隐式报头模式下,RegRxNbBytes是无效的,因为此时有效负载字节数必须是已知的)

寄存器RegFifoRxCurrentAddr显示最后接收的数据包在FIFO数据缓存中的存储位置。

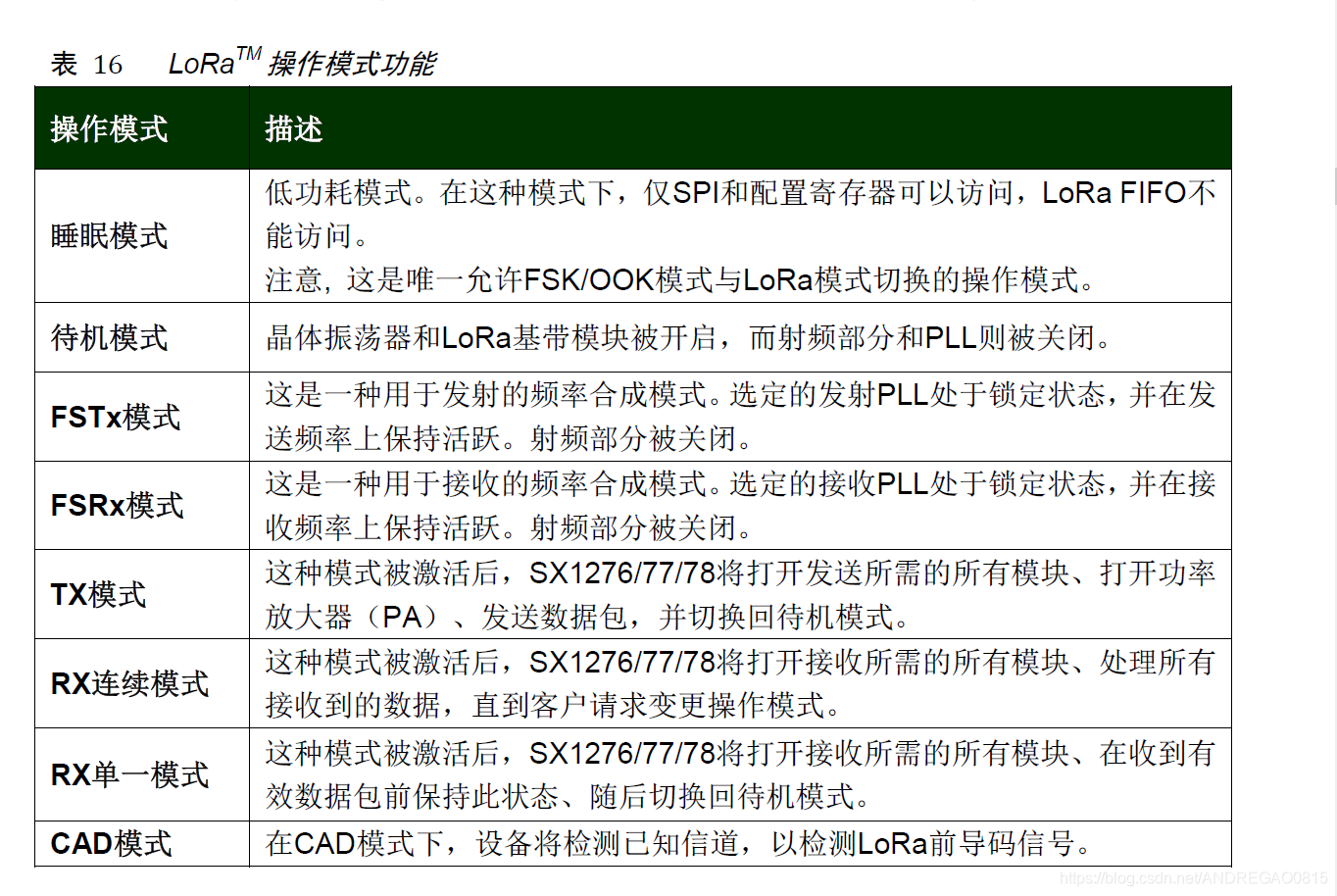

Lora调制解调器操作模式

启动Lora模式(设置RegOpMode的LongRangeMode位)后,就可以查看Lora调制解调器的操作模式。

通过修改RegOpMode寄存器的值,可以从任意模式切换到另一种模式。

Lora接收机模式

1.单一接收操作模式

调制解调器在给定的时间窗口内搜索前导码。如果在给定的时间窗口内还未找到前导码,则芯片会产生RxTimeout中断信号并切换回待机模式。时间窗口长度由RegSymbTimeout寄存器定义。

在有效负载结束时,如果负载CRC无效,则会产生RxDone中断信号及PayloadCrcError中断信号。

2.连续接收操作模式

每当调制解调器检测到前导码时,调制解调器都会在收到数据包前对该前导码进行检测和跟踪,然后等待检测下一个前导码。

在连续的RX模式下,当产生超时中断时,设备不会进入待机模式。这是,用户必须在设备继续等待有效前导码的同时直接清除中断信号。

从FIFO数据缓存提取有效负载数据

为从FIFO数据缓存检索接收数据,用户必须保证状态寄存器RegIrqFlags中的ValidHeader、PayloadCrcError、RxDone及RxTimeout等中断信号未意外生效,以确保数据包接收成功终止(即不应设置任何标志)。

如果发生错误,应跳过以下步骤,同时丢弃数据包。为从FIFO数据缓存检索到有效的接收

数据,用户必须:

RegRxNbBytes:表示到现在为止已接收到的字节数。

RegFifoAddrPtr:精确标志了LoRa调制解调器接收数据写入位置的动态指针。

将RegFifoAddrPtr设置为RegFifoRxCurrentAddr:表示将FIFO指针指向FIFO数据缓存中最后接收的数据包的存储位置。可以通过RegRxNbBytes次读取寄存器RegFifo中的数据,以提取数据包的有效负载数据。

或者,可以手动将RegFifoAddrPtr设置为RegFifoRxByteAddr减去RegRxNbBytes的值,使该指针从当前数据包开始,一直指向最后接收的数据包的存储位置。可以通过RegRxNbBytes次读取寄存器RegFifo中的地址,以提取数据包的有效负载字节。

963

963

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?