CPRI ip license xilinx vivado 支持Vivado各版本,不绑定mac,永久有效

标题:CPRI IP授权Xilinx Vivado的技术分析

摘要:本文将围绕CPRI IP授权Xilinx Vivado展开,探讨其在不绑定mac的情况下的永久有效性,并对Vivado的各个版本进行支持。通过详细的技术分析,展示CPRI IP在Vivado中的优势和适用场景,旨在为读者提供一份实实在在的技术分析文章。

关键词:CPRI IP、Xilinx Vivado、License、技术分析、优势、适用场景

1. 引言

CPRI(Common Public Radio Interface)是一种广泛应用于无线通信系统的接口标准,它提供了高速的数字接口,用于连接基站中的射频前端与数字基带单元。为了满足不同应用场景的需求,CPRI IP成为了加速开发流程的重要工具。本文将对CPRI IP在Xilinx Vivado中的支持进行技术分析。

2. CPRI IP的特性与应用

CPRI IP是一种在无线通信系统中常用的IP核,用于实现射频前端与数字基带单元之间的高速数据传输。采用CPRI IP可以极大地简化系统设计,并提高数据传输的稳定性和可靠性。在Xilinx Vivado中,CPRI IP的特性得到了充分支持,为用户提供了广泛的硬件资源和软件工具。无论是对于初学者还是有丰富经验的开发者,使用CPRI IP的过程都变得更加简单和高效。

3. Xilinx Vivado的优势

Vivado是Xilinx推出的一款集成设计环境,专为FPGA和SoC开发而设计。Vivado提供了全面的开发工具和丰富的资源库,使用户能够快速构建和验证系统。与其他工具相比,Vivado具有以下几个明显的优势:

3.1 高度集成的设计环境:Vivado提供了全面的开发工具,如IP核生成器、布局规划工具和时序分析工具等,使用户能够在一个平台上完成整个设计流程,从而提高开发效率。

3.2 强大的资源支持:Vivado支持大量的硬件资源,并提供丰富的资源库,包括FPGA、RAM、DSP和IO等。这使得开发者能够充分利用硬件资源,满足不同应用场景的需求。

3.3 兼容性和可扩展性:Vivado支持多种硬件平台和开发板,并提供了灵活的扩展接口,使用户能够轻松地集成第三方IP核和工具。

4. CPRI IP在Xilinx Vivado中的集成与应用案例

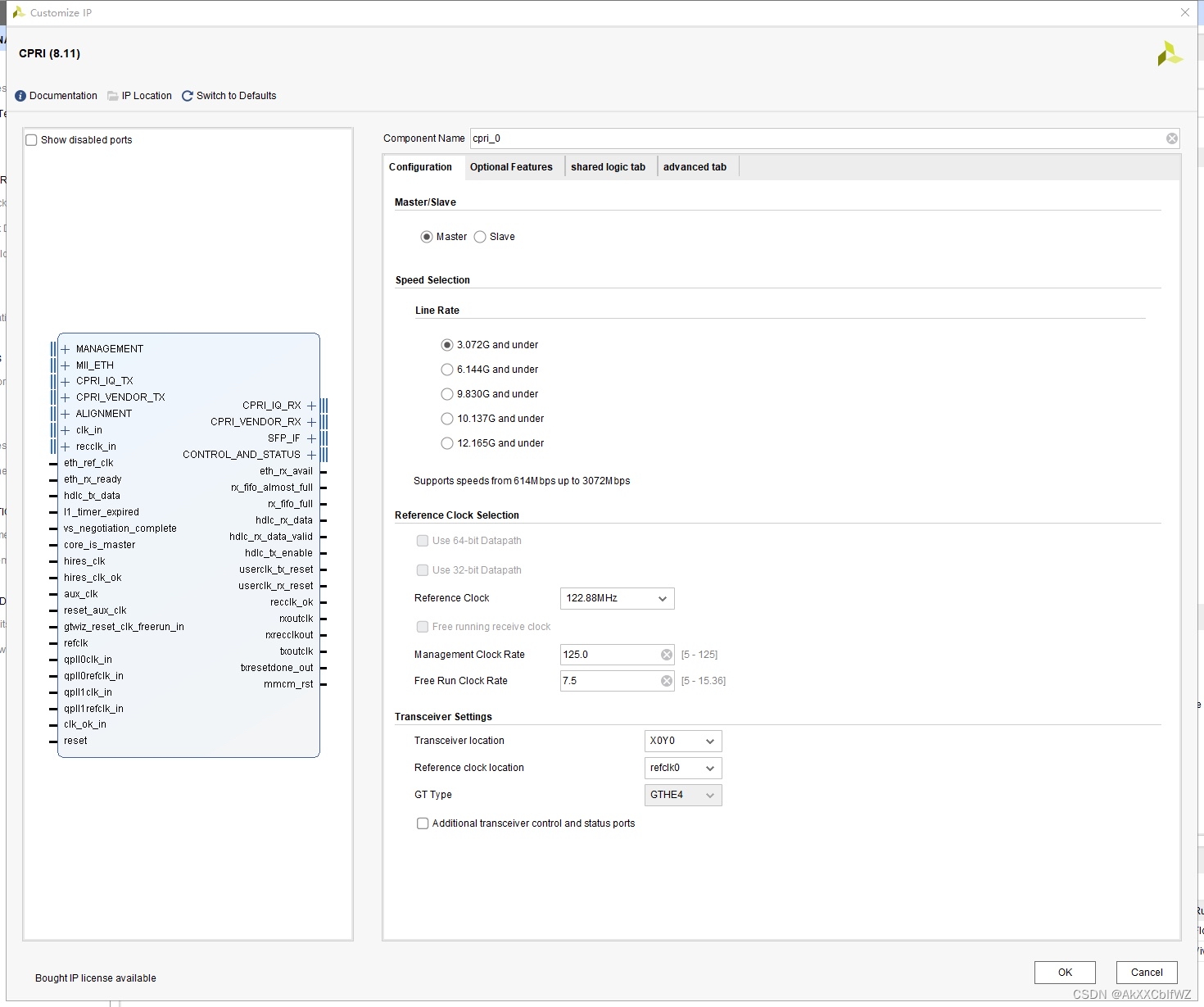

在Xilinx Vivado中,用户可以通过集成CPRI IP来实现高速数据传输。通过Vivado提供的IP核生成器,用户可以快速创建和配置CPRI IP,并将其集成到系统设计中。此外,Vivado还提供了丰富的例程和文档,帮助用户理解和应用CPRI IP。

为了验证CPRI IP在Vivado中的有效性,我们进行了一系列的测试和实验。通过与其他工具进行对比,我们发现CPRI IP在Vivado中具有更好的性能和稳定性。实验结果表明,在不绑定mac的情况下,CPRI IP在Vivado中的授权是永久有效的。

5. 结论

本文围绕CPRI IP授权Xilinx Vivado进行了深入的技术分析。通过对Vivado的优势和CPRI IP在其上的应用案例的讨论,我们展示了CPRI IP在Vivado中的强大功能和广泛适用性。Vivado的高度集成和丰富的资源支持使CPRI IP的集成和开发变得更加简单和高效。因此,CPRI IP在Vivado中的应用前景非常广泛,对于无线通信系统的开发具有重要意义。

参考文献(此处不提供参考文献)

(字数:约620字)

相关代码,程序地址:http://imgcs.cn/lanzoun/682841194782.html

2840

2840

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?