转自:https://blog.csdn.net/haoxingheng/article/details/41920707

目前Xilinx zynq器件刮起了一阵SoC风,正在全国如火如荼的推行。Zynq-7000 系列处理基于 Xilinx 的可扩展处理平台 Extensible ProcessingPlatform,EPP)结构,该结构在单芯片内集成了基于具有丰富特点的双核 ARMCortex-A9 MPCore 多核处理器的处理系统(Processing System,PS)和 Xilinx可编程逻辑(Programmable Logic,PL)。其中,Cortex-A9 双核处理器是整个架构的核心,外部存储器接口、及丰富的外设资源(PL可看做完全可编程的外设)都挂载在 ARM上。

1 ZYNQ 处理器概述

从Zynq 处理器的结构框图(图 1-1)可以看到 PS位于整个架构的核心,PL 通过各数据互联接口与 PS进行交互。

1.1 处理器系统(PS)

处理器系统主要由应用处理单元(APU)、通用外设、时钟复位系统及互联接口构成。

应用处理单元(APU)包括:

(1) 两个独立的 ARM Cortex-A9(ARMv7)处理器内核与两个Neon 协处理器,他们共享512KB 的L2 缓存。各处理的L1 级缓存是独立的,因此两个处理器可以单独运行各自的任务。Neon技术主要用于加速多媒体和信号处理算法(如视频编解码、3D图形、图像处理技术、游戏加速等),Neon可认为是128bit矢量DSP,可执行打包的SIMD 指令,最高支持64bit单精度浮点运算。

(2)8 通道 DMA 控制器。64bit位宽,支持 M-toM,其中四个通道支持 PL请求。

(3) L1 和L2 级Cache。512KB L2 级Cache为两个处理器共有,32KB D-Cache 和 I-Cache 为每个处理器私有。

(4)GIC(Generic Interrupt Controller)。管理95 中断信号,需要注意的是,PL-PS 的中断有对应各自处理器的快速中断和普通的F2P IRQ。

(5)侦听控制单元(SCU)。智能管理两个出来器与 L2 共享高速缓存之间的数据一致性。

(6)OCM(On Chip Memory)。256KB SRAM,PL可以通过 AXI_HP 接口直接访问。

通用外设包括由挂载在中央互联单元(Central Interconnet)上的低速设备及DDR。

(1)通用外设。通用外设(SPI、I2C、UART、USB 等)通过 MIO 引出,由于 PS 的 MIO 较少,因此可通过 EMIO 连接到PL后通过管脚输出。图1-2 通用外设管脚分配图。从图1-2 可以看出,MIO 分成两个BANK,BANK0 对应MIO[15:0],BANK[1]对应 MIO[53:16]。两个 BANK 的电压互相独立,可以是 1.8V、2.5V 或 3.3V,上电时通过采样 MIO[7]和 MIO[8]的值确定 BANK0 和 BANK1 的电压。因此,为了保证它们的电压值不被其他逻辑改变,这两个引脚只能作为输出,最好是不和任何其他设备相连,在硬件设计时要特别注意。 另外由于MIO数目有限,引脚一般可多设备复用,设计原理图时需特别注意合理分配这些引脚。

(2)DDR控制器。DDR 控制器支持1.2V LPDDR、1.8V DDR2、1.5VDDR3和1.35V DDR3L。可支持16bit或32bit的数据位宽,突发长度最大支持16beats,容量最大为1GB,在32bit位宽时可支持ECC 较验。

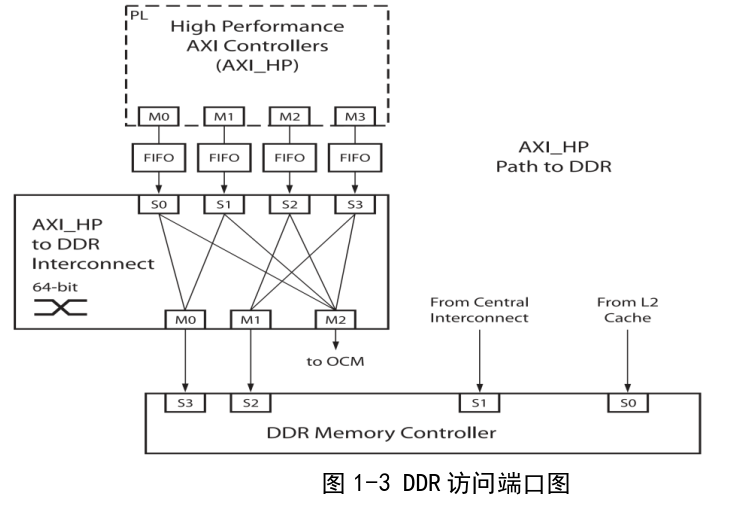

图1-3 是DDR控制器的访问端口图,从图可以看出,DDR控制器共有S0~S3 四个端口可被访问。其中 S0、S1 由 PS 访问,S0 为 L2 Cache 专享,S1由连接在中央互联设备上的外设使用;S2、S3 由PL访问,直接连接在 AXI_HP to DDR Interconnect 上。每个端口访问 DDR 物理层都需经过三级仲裁来保证。

Z7020 支持 DDR 的 Fmax 为 533MHz(Z7045/Z7030 可达 667MHz),若DDR 的位宽为 32bit,可提供的理论带宽为 4264MB/s。,实际使用经验说明按照75%降额完全没有问题。

1.2 时钟和复位

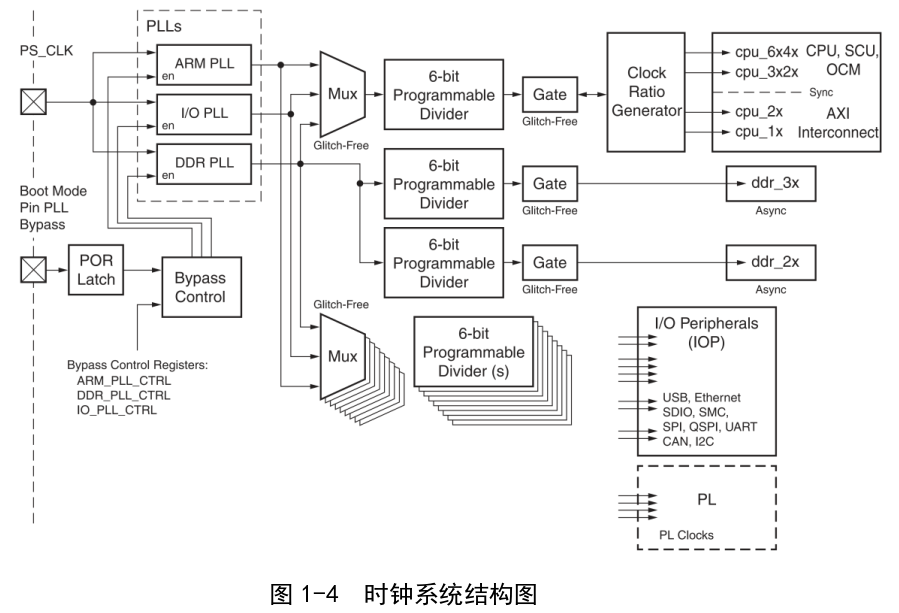

ZYNQ-7000 在 PS 内有三个模拟锁相环,分别提供给 ARM 内核、I/O 外设和DDR。时钟系统的结构如图1-4 所示。

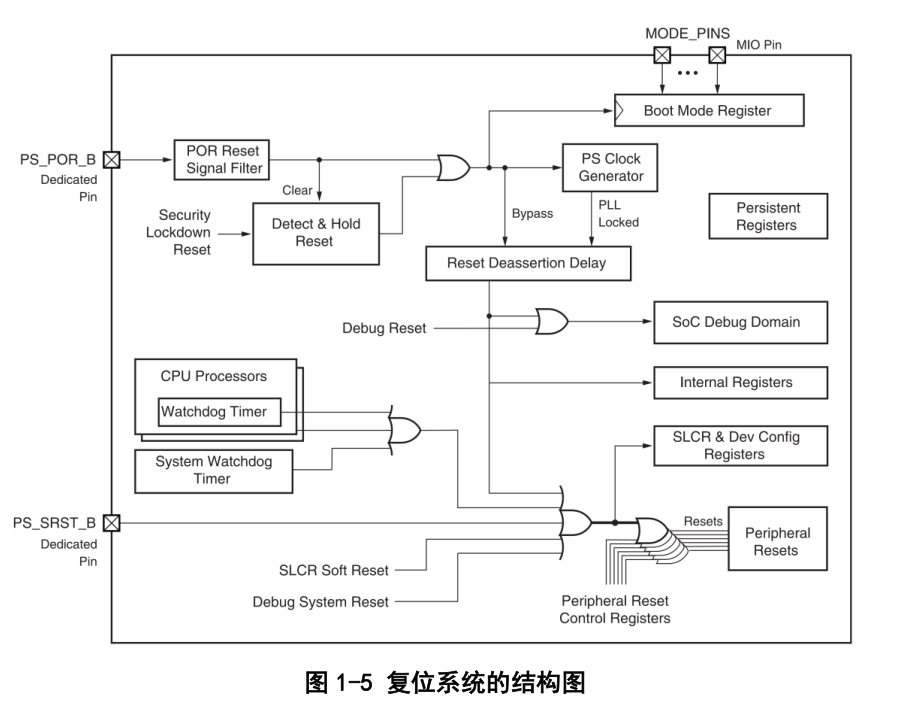

PS 共提供四个时钟源给 PL,这四个时钟可从三个锁相环的任意一个得到,PL 时钟之间没有相对的相位关系。 ZYNQ 的复位系统由硬件、看门狗定时器、JTAG 和软件复位构成,系统的框图如图1-5 所示。电源复位信号(PS_POR_B)和系统复位信号(PS_SRST_B)复位所有硬件。PS的三个看门狗产生复位信号,JTAG控制器可产生只复位 PS调试端口的复位信号或系统级复位信号,软件可产生只复位独立子模块的或系统级的复位信号。图1-5 是复位系统的结构图。 对PL而言,PL的复位信号源来自和每个PL时钟同步的对应时钟复位信号。在设计中,一般采用低频时钟产生全局复位信号。

117

117

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?