1. I2C总线概述

I2C总线是一种受欢迎且性能强大的总线,它是PHLIPS公司推出的一种串行简单、双向二线制同步串行总线。只需要两根线(SDA和SCL)即可在连接于总线上的器件之间传送信息。具有接口线少,控制方式简单,通信速率高等优点。可以用于主(可多主)和单个或多个从设备之间的通信。

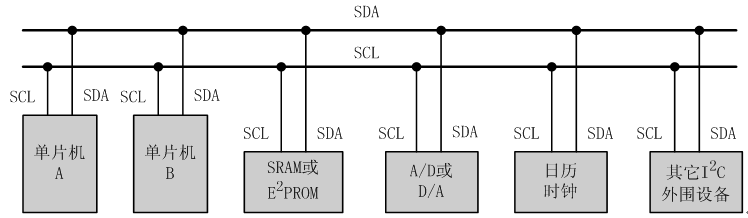

图1展示了典型的I2C总线系统,此I2C系统中有多个从机,单片机A/B作为主机控制着多种从机,如:EEPROM、ADCs/DACs等设备。

图1 I2C总线拓扑示例

2. I2C电气结构及特性

2.1 电气结构

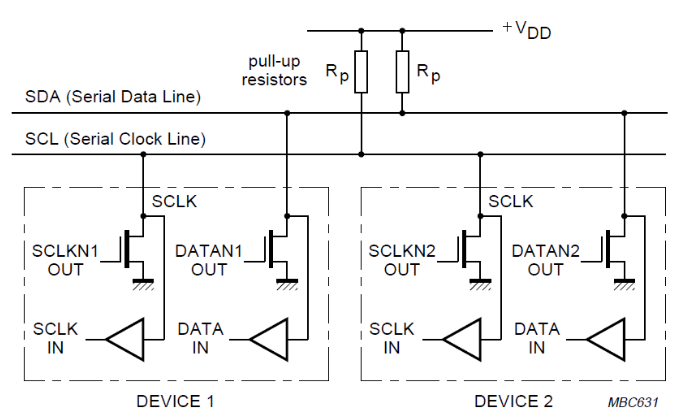

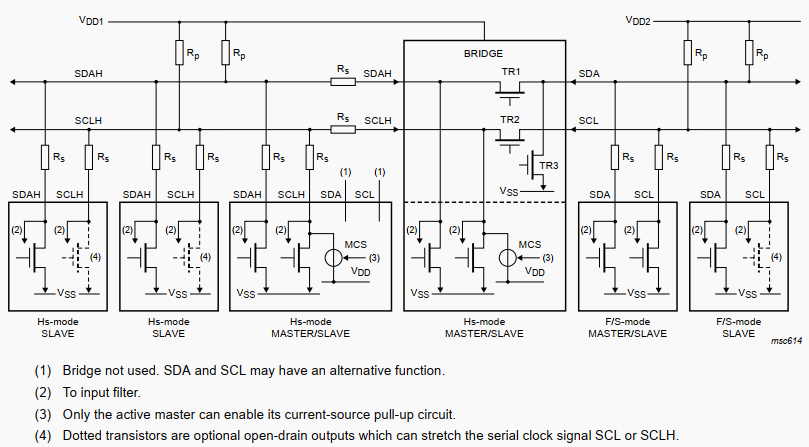

图2 I2C总线结构图

I2C总线通过两根线进行通信的:串行时钟线(SCL)和串行数据线(SDA)。这两根信号线采用了漏极开路(Open-Drain)或集电极开路(Open-Collector)的输出结构,它可以将拉低到某个电压(大多数情况下接地)或释放总线通过上拉到电源的电阻拉高到电源电压。由于OC/OD结构,不具备使总线驱高的能力,因此总线的驱高就需要上拉电阻到电源来提供高电平信号,因此在此情况下,没有任何设备可以将线路强制输出高电平,就是说总线永远不会出现某一个设备在高电平,其他设备低电平时候出现短路的情况,避免了总线出现电气故障,但是也因此由于OC/OD结构,I2C总线在标准模式和快速模式最大速率仅达到400KHz,从而限制了总线的传输的速率;

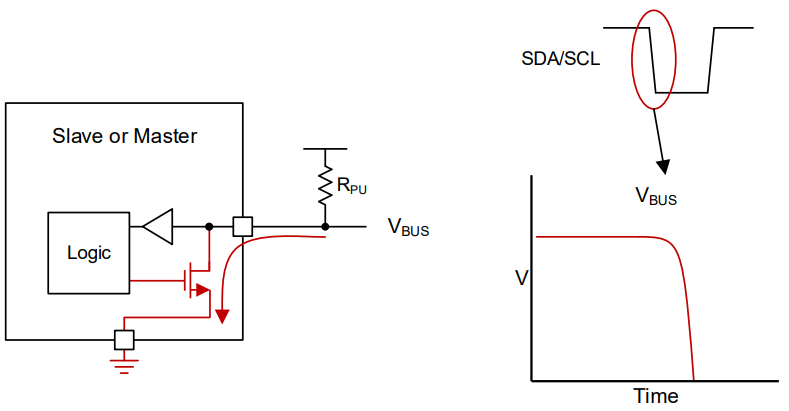

图3 I2C-OD内部基础结构-总线拉低

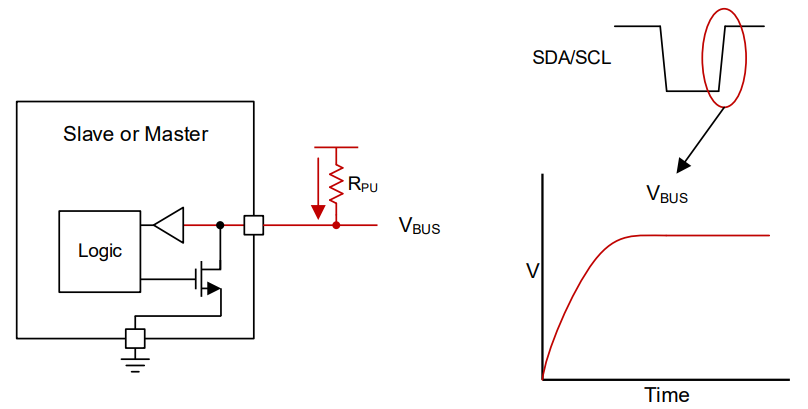

图4 I2C-OD内部基础结构-总线拉高

图3/4展示的是从设备或者主设备内部简化图,OD门电路输出管的漏极若是悬空,当输入高电平时候,MOS管导通,输出被拉低到GND,呈现低电平。当输入低电平时,MOS管截至,输出端相当于开路,呈现高阻,此时是无法输出高电平,若如上图2所示有上拉电阻Rpu,那么此结构下就可以将总线电平释放到高电平状态。也正是由于I2C这种硬件结构,实现了线与的硬件逻辑,只要有一个设备优先将设备拉低,那么整个总线就会拉低。

2.2 上拉电阻的选择

由于I2C总线采用OC/OD结构,因此只能通过上拉电阻Rp将信号拉高,因此I2C总线上的上拉电阻是不可缺少的,那么该如何选择呢?上拉电阻的选择与总线电容相关,总线电容指的是电路板上的走线、焊盘和元器件引脚之间的连接所产生的总体电容之和,总线电容和上拉电阻就构成了一个RC电路,RC电路的取值,决定了信号的充放电时间,也就决定了信号可以达到的上升和下降的时间。在这里,低电平的最大电压为供电电压的0.3倍,而高电平的最低电压为供电电压的0.7倍,通过这里的第一步计算,可以知道信号达到0.3VDD所需要的时间为t1,接下来的一步计算信号达到0.7VDD所需要的时间t2。t1和t2之间的时间差,也就被定义为信号的上升时间。阈值电压为VIH=0.7VDD和VIL=0.3VDD,时间常数RC与电压V(t)关系为V(t)= VDD(1 - e⁻ᵗ/ᴿᒼ),t是充电时间,RC是时间常数。

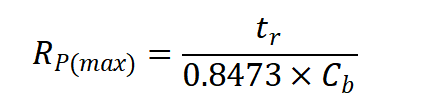

得到计算I2C总线上拉电阻最大值的公式。从这个公式中,可以看出这个电阻的最大值,决定于信号的上升时间tr,和总线电容Cb。参考I2C协议可知,在标准模式最大时间1000ns,快速模式中上升时间最大为300ns,

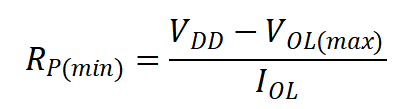

上拉电阻的最小值计算较为简单,直接套用公式即可:

当供电电压VDD大于2V时,低电平输出的最高电压值VOL(max)都是0.4V,当低电平输出电压VOL(max)为0.4V时,在标准和快速模式下,其输出电流至少为3mA。利用这些数值,就可以计算出I2C总线上拉电阻的最小值。

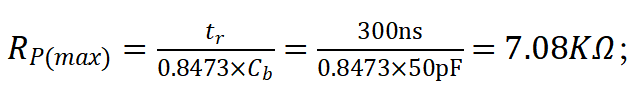

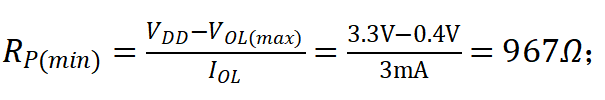

exp:在快速模式下,供电电压为3.3V,总线电容为50pF:

上拉电阻的最大值:

上拉电阻的最小值:

3. I2C标准介绍

3.1 支持的频率:

Standard-mode(标准模式):工作频率在0~100kHz,双向总线;

Fast-mode(快速模式):工作频率在0~400kHz,双向总线;

Fast-mode Plus(快速+模式):工作频率在0~1000kHz,双向总线;

Hs-mode(高速模式):在Cb为小于100pf时,工作频率在0~3.4MHz,在400pf时,工作频率为0~1.7MHz,双向总线;

Ultra Fast-mode(超高速模式):工作频率在0~5MHz,单向总线;

3.2 设备工作的模式与数据包格式

主机模式:能够驱动SCL时钟线的设备;

从机模式:被主机寻址的设备,需要应答主机的设备;

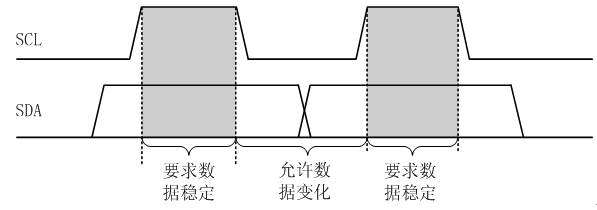

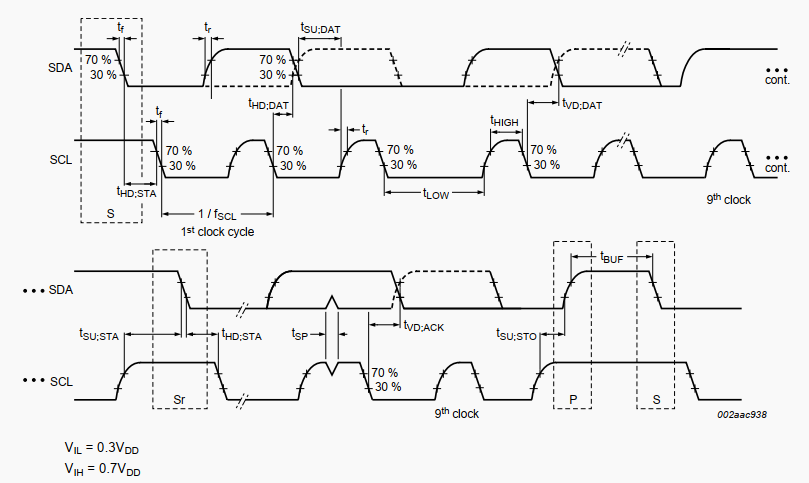

根据I2C协议,除了起始与停止条件外,当时钟为高电平时,数据线不会发生变化,当时钟信号为低时候,数据线才会容许变化,如图5所示;

图5 I2C数据线变化与时钟线变化的关系

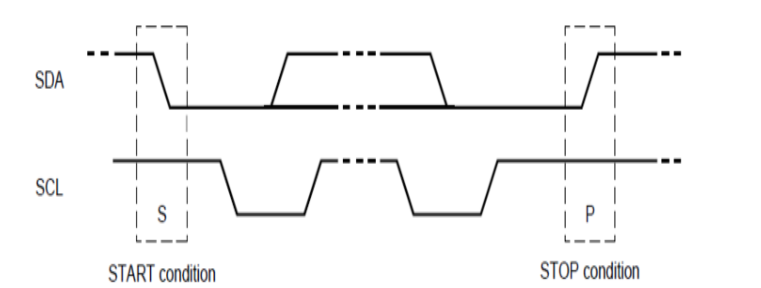

起始和终止信号:SCL线为高电平期间,SDA线由高电平向低电平的变化表示起始信号;SCL线为高电平期间,SDA线由低电平向高电平的变化表示终止信号,这是唯一违反时钟SCL高点平时SDA不能跳变的规则的情况;

图6 I2C起始条件与停止条件示意图

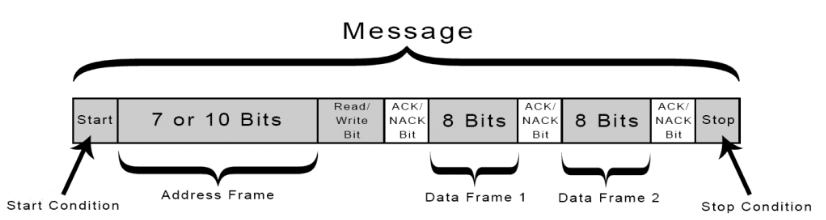

I2C数据包常见形式之一是起始条件(1bit)+从设备地址(7/10bit)+读写(1bit)+应答(1bit)+数据(8bit)+应答(1bit)+...+停止条件(1bit),从设备地址常见的为7bit情况,如下图6所示;

图7 I2C数据包示例

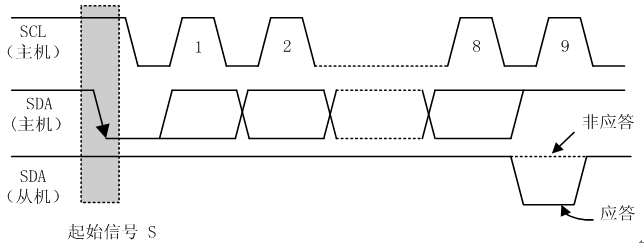

3.3 从机地址+读写+应答

由于I2C是有多个从机,因此针对特定从机的通信需要进行选中,I2C选中通信的从设备的方式是通过地址实现的,在地址后紧跟着读写位,高电平表示主机读取从机设备,低电平表示往从机写数据。在一组I2C系统中,每个从设备地址都是独特的,在传输中地址位是在起始位之后的,主机发送从机地址给多个从设备,若从设备与主机发送的地址是匹配的,那么从机就会返回一个低电平响应主机,如果没有从设备地址匹配成功,那么没有从机拉低,总线保持高电平在响应位,此时就是未响应,如下图8所示,地址与数据传输特点:每一个bit传输时候有限传输的最高位MSB,每一个被传输的bit后面都必须有一个应答,因此加起来一帧总共有9位;

图8 I2C传输帧前示例

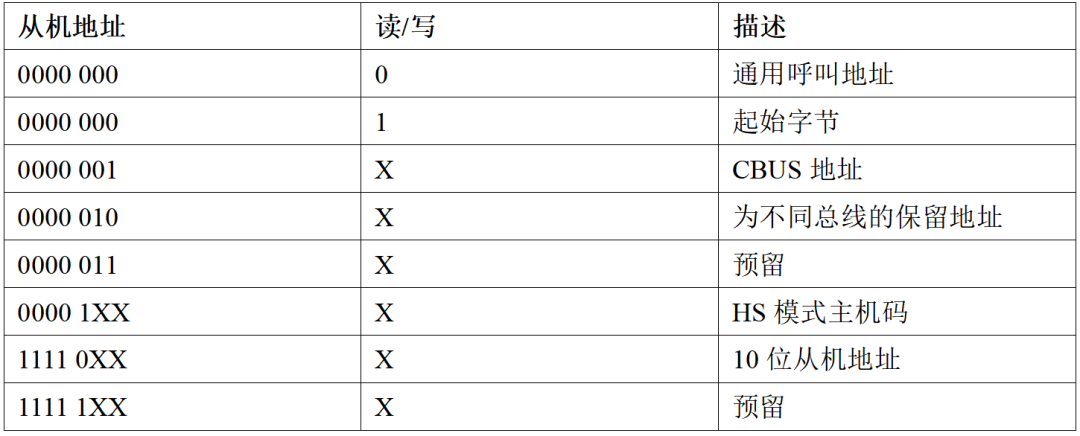

I2C保留了8个地址,用于特殊用途,特殊地址如下:

3.4 I2C总线数据的读写

1> I2C总线写数据,主机->从机:

A. 主机发送起始条件和地址给从机;

B. 从机应答,主机发送数据给从机,从机应答;

C. 主机发送停止信号;

若连续写多个数据,由于每一次传输最多传输8bit,因此多个字节数据需要重复B步骤直到写完成。最后执行C步骤即可,如下图所示;

图9 I2C连续写示例图

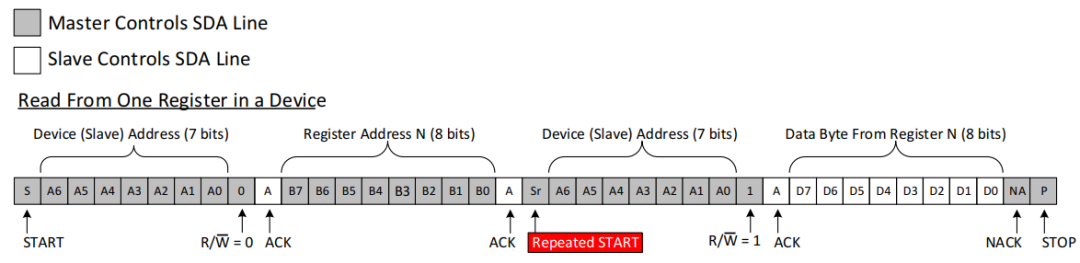

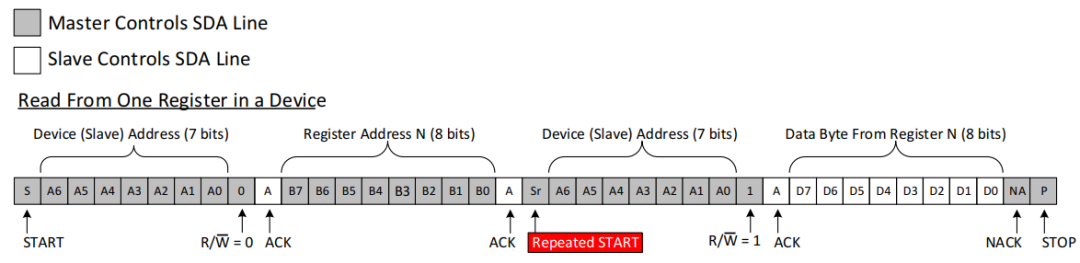

2> I2C总线读数据,从机->主机:

A. 主机发送起始条件和地址给从机,从机应答;

B. 主机将要读取的寄存器地址发送给从机,从机应答;

C. 主机发送重复起始条件信号和从机地址;

D. 从机应答后,并发送读取的寄存器的数据到SDA;

E. 主机等待从机应答,从机不应答后,发送停止信号结束读数据;

若连续读多个数据,由于每一次传输最多传输8bit,因此多个字节数据需要重复D步骤直到多个数据的读完成,最后执行E步骤即可,可以知道的是重复起始条件的触发是在连续读可以触发的,直白一点就是说在I2C中要想对重复起始条件进行观测需要使信号数据方向发生一次读写改变,如下图所示,在前面的地址中,先要发送寄存器地址的过程就是写数据过程,后续重复起始条件后开始方向变为读方向了;

图10 连续读数据示例

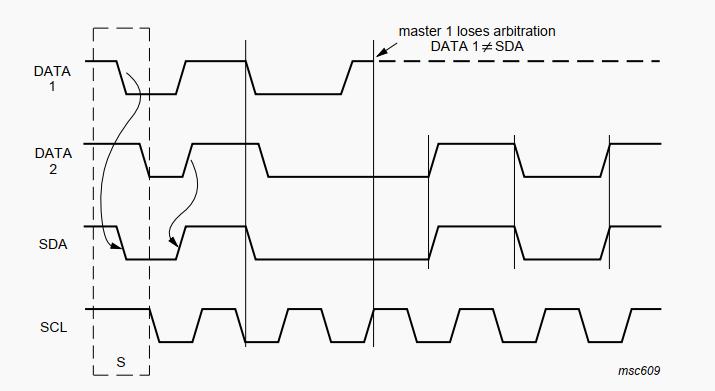

3.5 仲裁与同步

总线仲裁是在多个主机设备同时访问从设备时候的一种裁定机制,确保只能一个主机能够成功控制总线并传输数据,仲裁就是利用I2C总线OC/OD结构线与的特点实现的,也就是说只要有一个节点发送低电平时候,总线就会表现为低电平;

同步:由于线“与”逻辑功能的原理,当多个节点同时发送时钟信号时,在总线上表现的是统一的时钟信号。这就是SCL的同步原理。

仲裁过程是:多个主机在发送第一个数据bit时,若所有设备发送的均为下相同电平(0/1),那么就继续下一位进行仲裁,若下一位仲裁中有主机拉高,那么拉高的主机退出竞争,留下剩下的主机,直到仅有一个主机为止,即获得总线控制权,简单来说就是在总线传输中,哪个主机优先拉低SDA,哪个主机获得总线控制权,若两个都拉低,那就下一位,看是否还会保持拉低状态,还保持的就是获得仲裁获胜者,注意的是SDA仲裁和SCL时钟同步处理过程没有先后关系,而是同时进行的;

图11 时钟同步

图12两个主机仲裁

3.6 I2C各个模式的区别与时序

1> 标准模式(Standard-mode):标准模式下的I2C频率100kHz之内,符合前面章节的所有特点,也是我们最常见的工作模式;

2> 快速模式(Fast-mode):

A. 最大传输频率400kHz,相比于标准模式调整了I2C的信号时序,兼容标准模式;

B. 快速模式器件的输入有抑制毛刺的作用,SDA和SCL输入有施密特触发器;

C. 快速模式器件的输出缓冲器对SDA和SCL信号的下降沿有斜率控制的功能;

D. 如果快速模式器件电源电压被关断,SDA和SCL的I/O引脚必须悬空,不能阻塞总线;

E. 连接到总线的外部上拉器件必须调整以适应快速模式I2C总线更短的最大允许上升时间。对于负载最大是200pF总线,每条总线上的上拉器件可以是一个电阻,对于负载在200pF~400pF的总线上拉器件可以是一个电流源(最大值3mA)或者一个开关电阻电路。

3> 快速增强模式(Fast-mode Plus):

快速增强模式时钟频率可达到1MHz,可以向下兼容快速和标准模式,与快速/标准模式的总线协议和数据格式相同,但是快速增强模式器件中提供了更高的驱动电流,无需使用总线缓冲器即可驱动更长的走线距离,更大的负载的器件;

4> 高速模式(High-speed mode):

除了在高速传输器件不执行仲裁和时钟同步外,与快速增强/快速/标准模式兼容且具有系统保持相同的串行总线和数据格式。为了获取更大传输速率,达到3.4MHz的时钟频率,相比于常规I2C做了以下的改动:

A. 高速模式下主机具有一个用于SDAH信号的开漏输出缓冲器,且集成了开漏下拉和电流源上拉电路。仅容许一主机的电流源被使能,并且仅限高速模式;

B. 高速模式下不执行仲裁和同步,目的是为了提高处理能力;

C. 高速模式主机器件输出高低比为1:2串行时钟信号,降低了对建立和保持时间的要求;

D. 高速模式主机器件由一个内部的桥。在高速传输中,器件的高速数据SDAH和高速串行时钟SCLH线通过桥与快速/标准模式的SDA/SCL区分开,这降低了SDAH和SCLH的容许负载,提高上升下降沿时间,为速率的提升做了贡献;

E. 高速模式从机在SCLH和SDAH输出端具有开漏缓冲器。SCLH引脚上的可选下拉晶体管可用于SCLH信号的时钟低电平拉伸,时钟拉伸仅容许在高速模式传输的应答位后进行;

F. 高速模式器件的输入在SDAH和SCLH输入端集成了尖峰抑制和施密特触发器;

G. 高速模式器件的输出缓冲器集成了SDAH和SCLH信号下降沿的斜率控制。

图13 高速模式结构与快速/标准模式转换结构

5> 超快速模式(Ultra Fast-mode):

时钟频率可以到达5MHz,所以在超快速模式结构为推挽式驱动,没有上拉电阻,进而此种设计只能使得从机作为接收机使用。因此同一个系列总线协议和数据格式与高速/快速/快速增强保持一致,但是单向的,与其他模式半双工模式不兼容,也就是说此模式下不能从机向主机发送设备,此种模式下无应答机制,不包含ACK周期。

4. I2C标准模式的实际信号时序测试

4.1 时序测试

测试参数说明:

①.tWR:从内部写序列的有效停止条件到写第一个设备地址字节的开始条件的时间长度 ;

②.tSU;STA:时钟信号变为高电平至数据信号由高电平变为低电平的时间;

③.tHD;STA:数据起始条件保持至时钟信号变为低电平的时间;

④.tHD;DAT:时钟信号变为低电平至数据输出信号电平变化的时间;

⑤.tSU;DAT:数据输入信号电平变化至时钟信号变为高电平的时间;

⑥.tSU;STO:时钟信号变为高电平至数据信号由低电平变为高电平的时间;

⑦.tBUFF:停止条件和下一次开始条件之间空闲的时间;

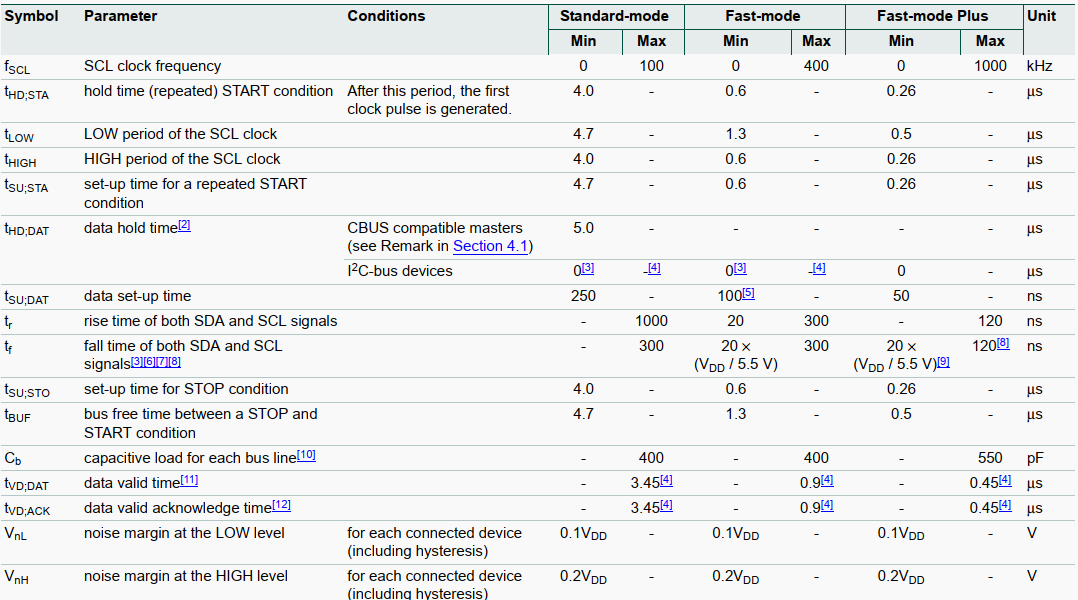

I2C标准模式时序图与要求如下:

表1 I2C时序参数要求

图14 I2C时序图

①. I2C读操作;

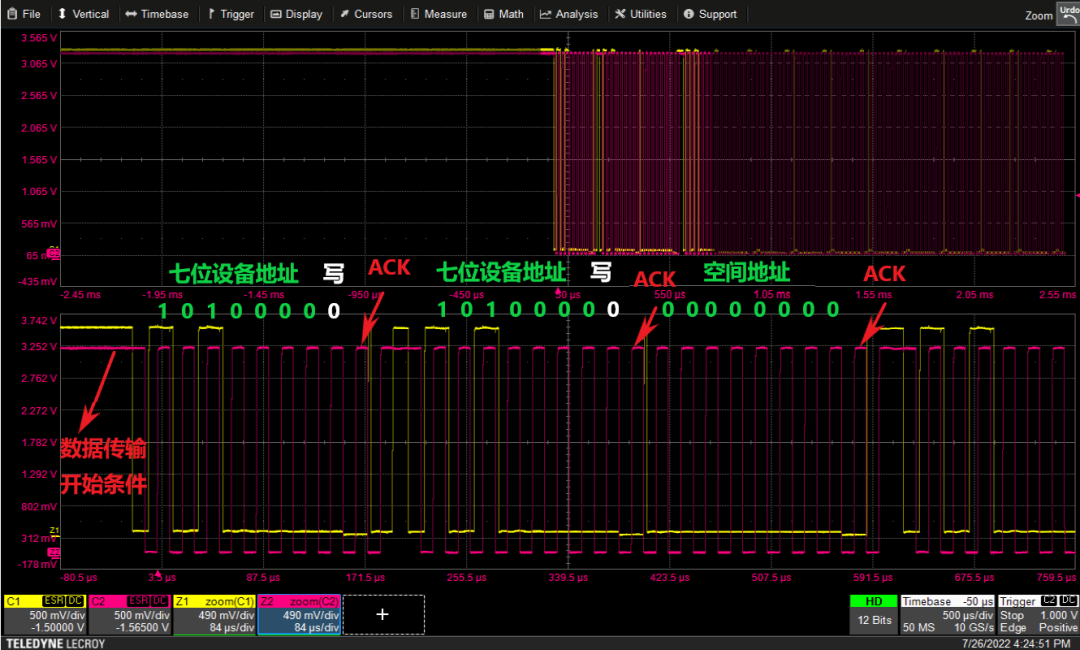

图15 I2C实际读测试信号波形展示

图16 I2C实际读信号Sr测试波形展示

I2C主机读取从机数据的操作流程:

写(目的是告诉EEPROM接下来要读的是哪个空间地址里面的数据)

-

主机发送开始信号+七位从设备地址+写操作位0;

-

从机发送应答ACK;

-

主机发送一个字节空间地址;

-

从机发送应答。

读(目的是读取EEPROM中某个空间地址里面的数据)

-

主机发送再开始信号Sr+七位从设备地址+读操作位1;

-

从机发送应答ACK;

-

从机发送一个字节数据;

-

主机发送应答ACK;

-

直到主机发送停止信号数据传输完成。

②. I2C写操作;

图17 I2C写信号测试波形展示1

图17 I2C写信号连续写波形展示2

I2C给从机写数据的操作流程:

-

主机发送开始信号+七位从设备地址+写操作位0;

-

从机发送应答ACK;

-

主机发送一个字节空间地址;

-

从机发送应答ACK;

-

主机发送一个字节数据;

-

从机发送应答ACK;

-

直到主机发送停止信号数据传输完成。

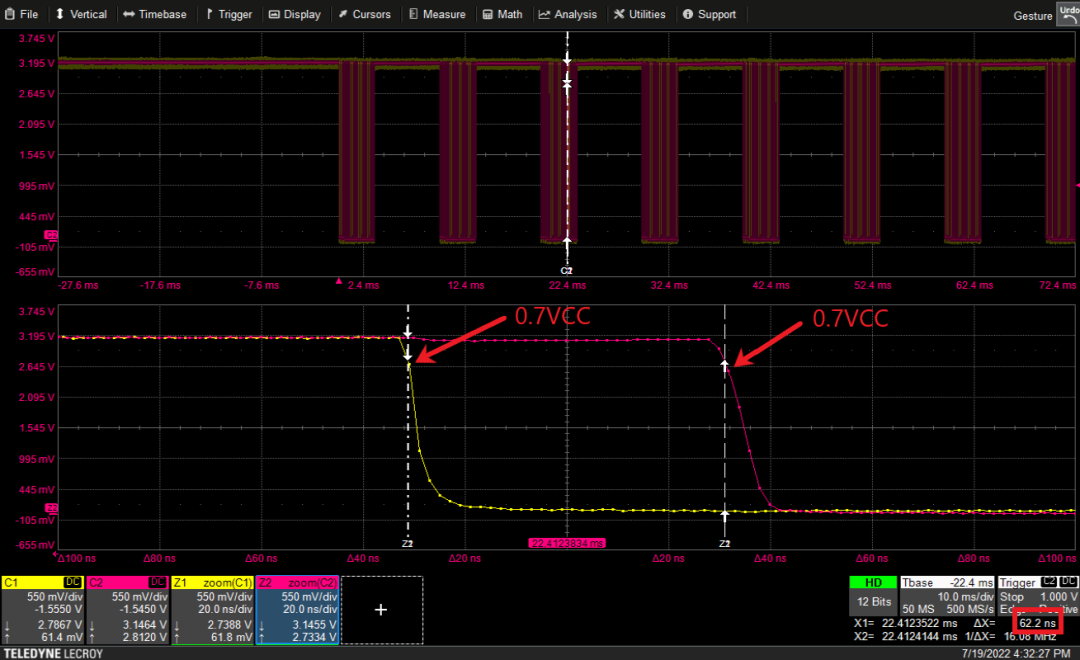

③. 图18 EEPROM的输出延时TAA测试;

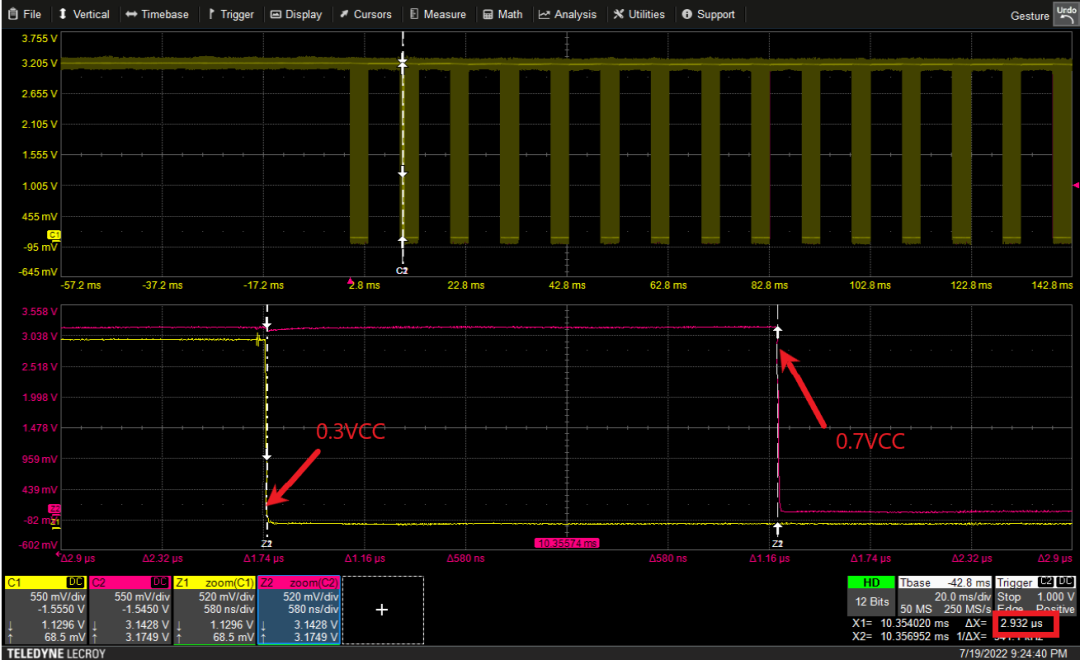

说明:此时在EEPROM读取数据下进行测试(软件输入命令切换读操作),黄色为时钟信号,红色为数据输出信号;时钟信号在0.7VCC处变为低电平,数据信号在0.7VCC处由高电平变为低电平并保持稳定,根据定义这两个坐标点横坐标之差即为输出延时TAA。

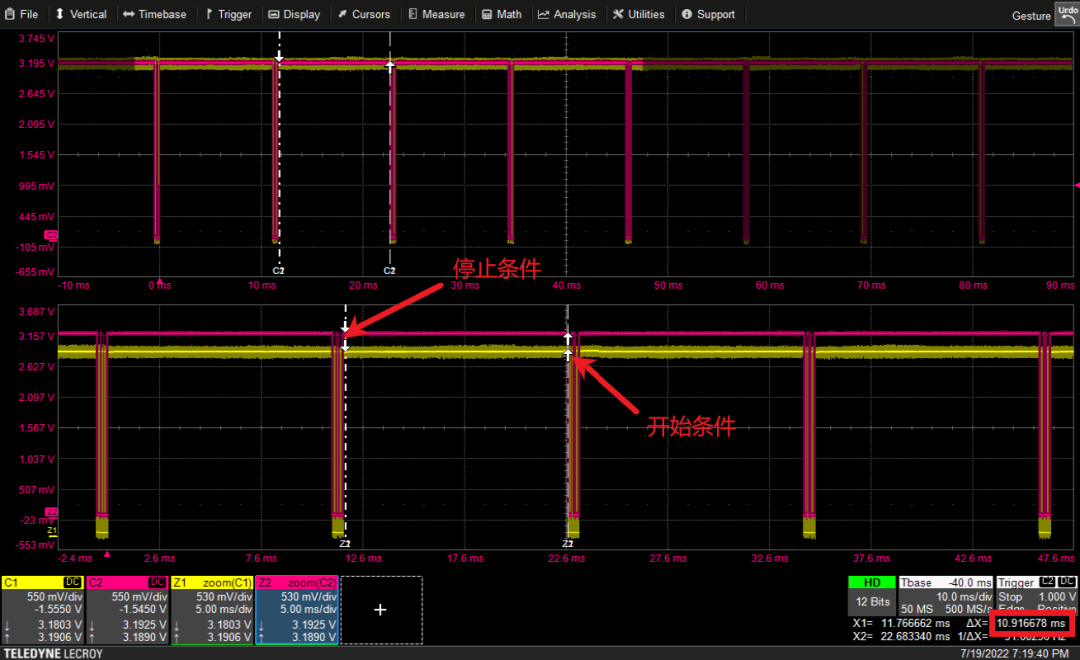

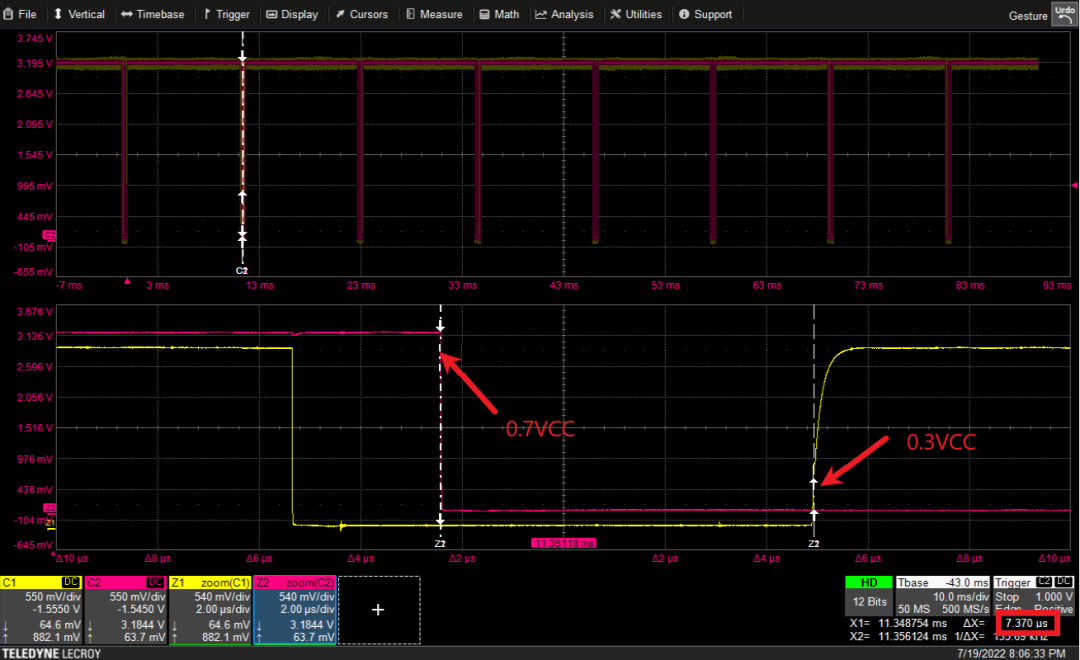

④. 图19 连续写周期EE(tWR)测试;

说明:此时在EEPROM写入数据下进行测试(软件输入命令切换写操作),黄色为时钟信号,红色为数据信号;左边数据信号由低电平变为高电平作为停止条件,右边数据信号由高电平变为低电平作为起始条件,根据定义这两个坐标点横坐标之差即为连续写周期EE(tWR)。

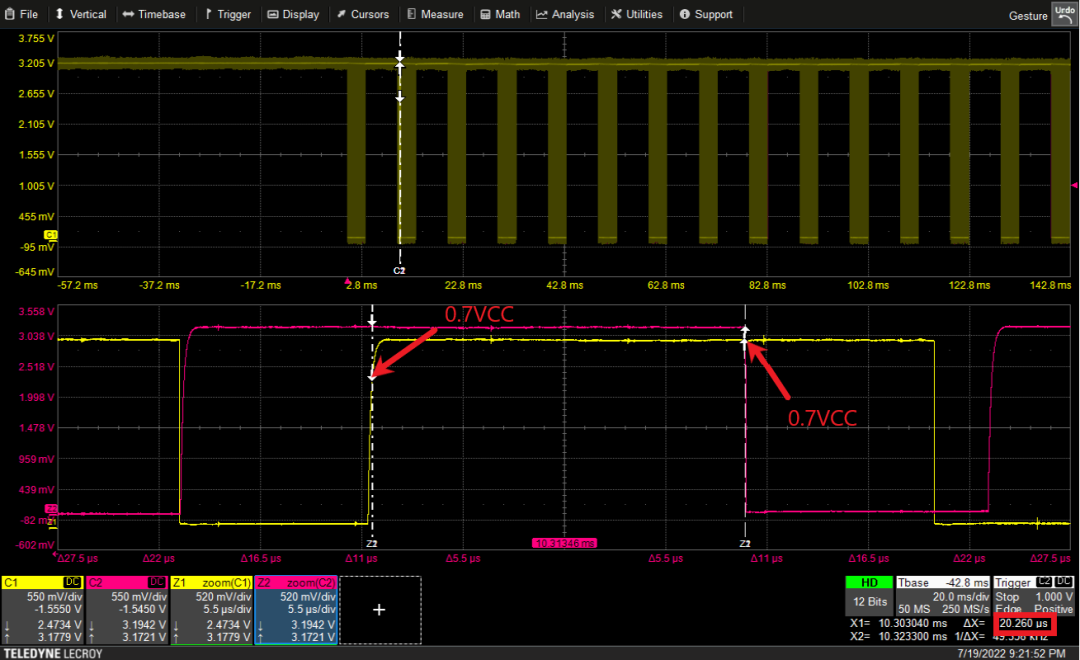

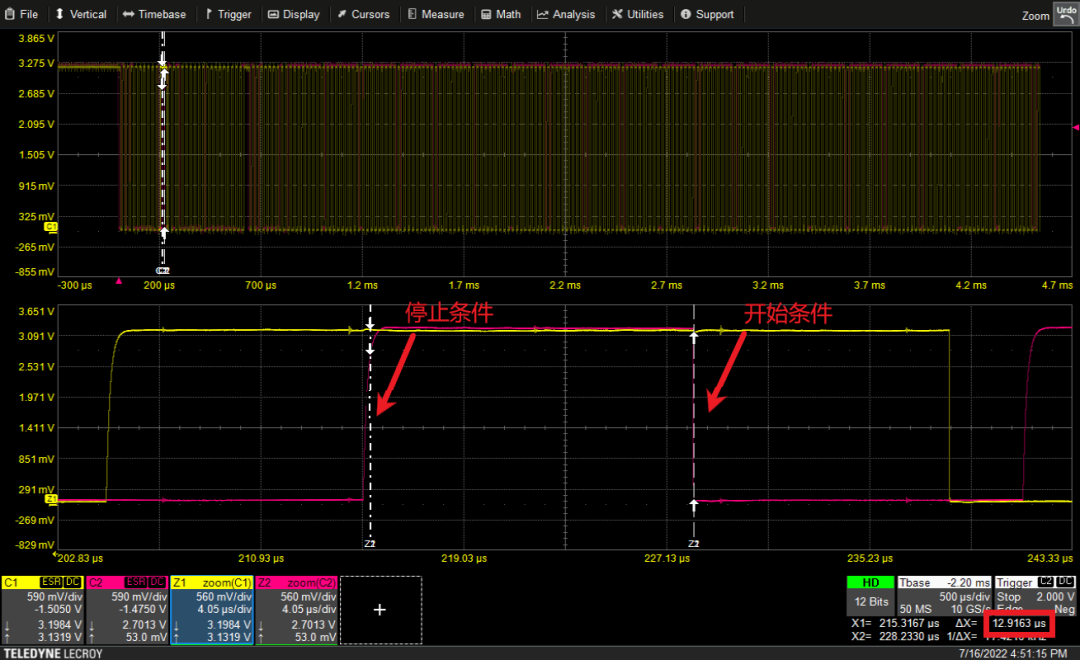

⑤. 图20 起始条件建立时间tSU;STA测试;

说明:此时在EEPROM读取和写入数据下均可测试;黄色为时钟信号,红色为数据输入信号;时钟信号在0.7VCC处开始采样,数据输入信号在0.7VCC处由高电平变为低电平,即为数据输入的开始条件,根据芯片手册定义这两点横坐标即为开始条件建立时间。

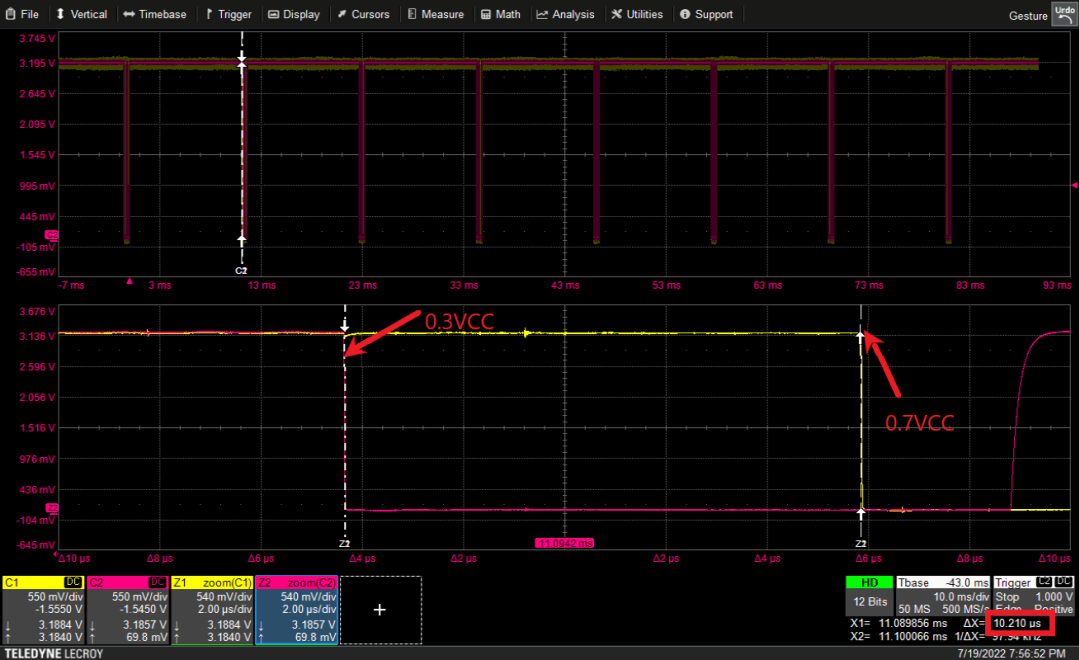

⑥. 图21起始条件保持时间tHD;STA测试;

说明:此时在EEPROM写入数据下进行测试(软件输入命令切换写操作);黄色为时钟信号,红色为数据输入信号;时钟信号在0.7VCC之前采样,在0.3VCC处数据输入信号启动开始条件并保持稳定,根据芯片手册定义此时两横坐标之差即为开始条件保持时间。

⑦. 图22数据信号输出保持时间tHD;DAT测试;

说明:此时在EEPROM读取数据下进行测试(软件输入命令切换读操作);黄色为时钟信号,红色为数据输出信号;时钟信号0.3VCC处后,数据输出信号在0.7VCC之前保持高电平稳定,根据芯片手册定义此时两横坐标之差即为数据输出保持时间。

⑧. 图23 数据信号输入建立时间tSU;DAT测试;

说明:此时在EEPROM读取数据下进行测试(软件输入命令切换读操作);黄色为时钟信号,红色为数据输入信号;时钟信号0.3VCC采样前,数据输入信号从高电平变为低电平,根据芯片手册定义此时两横坐标之差即为数据输入建立时间。

⑨. 图24 结束信号建立时间tSU;STO测试;

说明:此时在EEPROM写入数据下进行测试(软件输入命令切换读取);黄色为时钟信号,红色为数据信号;时钟信号高电平采样期间,数据信号在0.3VCC处由低电平变为高电平启动停止条件,根据芯片手册定义此时两横坐标之差即为停止条件建立时间。

⑩. 图25 总线空闲时间tBUFF测试;

说明:此时在EEPROM写入数据下进行测试(软件输入命令切换读取);黄色为时钟信号,红色为数据信号;根据定义此时图片标记处两横坐标之差即为总线空闲时间。

5. 参考文档

1. UM10204 I2C-bus specification and user manual.pdf

692

692

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?